今回、第8回は「動作不良事例と解決方法」について、代表的な5つの事例を踏まえて、ご紹介していきます。FPGAの電源部分を設計する際には、多様な不具合が発生する可能性があります。それはレイアウト、周辺部品、シーケンス、パターンなどに起因します。

以下、ご紹介する不具合動作事例と、その解決方法を ご参考にしていただき、今後のFPGA電源設計にお役立ていただければと思います。

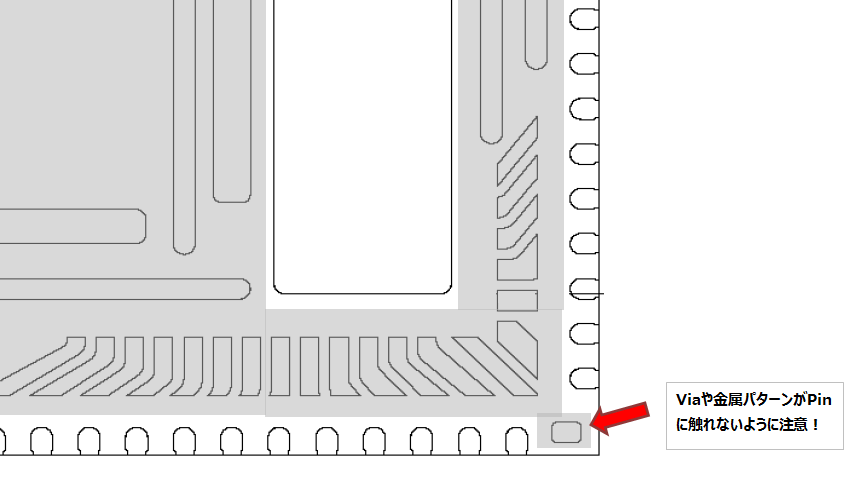

事例1:レイアウトに起因する出力不良

- 症状:出力電圧波形が三角波のように、特定電圧間を行ったりきたりする

- 原因:裏面のパターン配置禁止領域のパッドに、VIA が触れていた

- 対策:VIA の場所を移し、禁止領域にパターンを引かないことにより安定して出力

- 注意:データシートのパッケージ項を確認し、禁止領域にはパターンやVIAを配置しないようにする

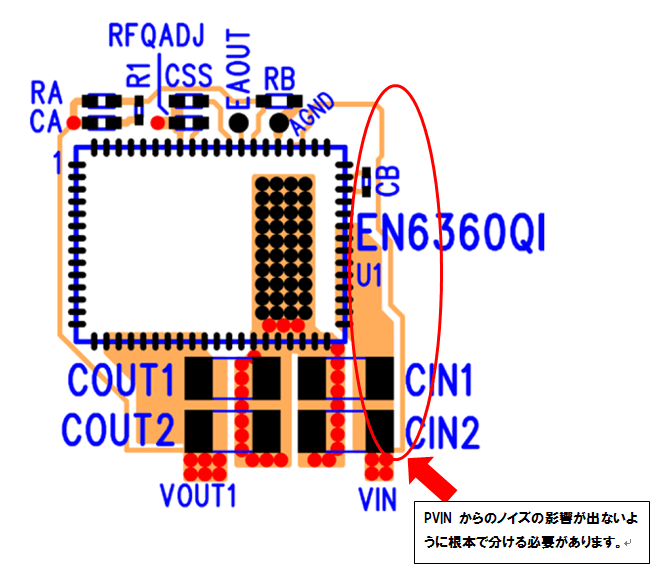

事例2:レイアウトに起因する動作不良

- 症状:動きはするが発熱がひどい

- 原因:VIN から分岐する AVIN の取り出しパターンが PVIN の電流ループに近くノイズが乗っていた

- 対策:VIN の根元からパターンを引くこと(ケルビン接続)により、ノイズ混入が緩和、発熱は収まった

- 注意:パターン例やデザインガイドを参照し、電源やフィードバックへのノイズの混入を極力減らすパターンにする

事例3:周辺部品による影響

- 症状:電源投入時出力されない

- 原因:出力容量の付け過ぎによる過電流検出

- 対策:出力容量を適切にすることで正常に起動

- 注意:出力容量の最大値があり / 各デバイスのデータシートで最大容量値を確認する

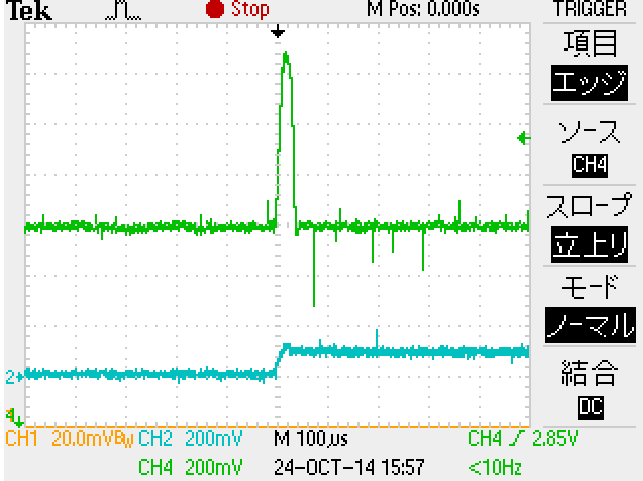

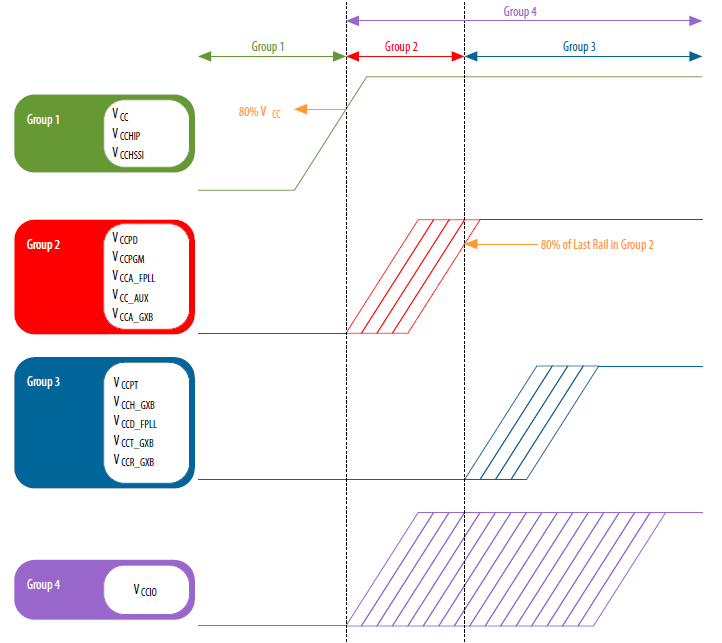

事例4:シーケンスに関する不良

- 症状:出力電圧が上がりかけるが途中で落ちてしまい、電源が起動しない

- 原因:起動シーケンスが守れておらず、起動時にリミット以上の電流が流れていたため、過電流が検出された

- 対策:起動シーケンスを守ることで、不要な電流がなくなり無事起動した

- 注意:Cyclone、Arria、Stratix の IV の一部や V 以降のシリーズには起動シーケンスあり / デバイスハンドブックの Power Management にある Power-Up Sequence 項を参照し、 各電源ラインを適切に起動する

以上のように、不具合事例と 解決方法をご参考いただき、今後のFPGAの電源設計の際にお役立ていただければ幸いです。

もっと、不具合事例を知りたい方は、電源コラム(不具合事例や注意点のまとめ)を見てください。

次のコラムではインテル社が提供している PDNツール を使ってご紹介します。