今回は、インテル社が提供している PDN ツール を使って、適切な容量の目安算出方法を ご紹介いたします。

インテル社 の PDN ツール (2015年9月15日現在2.0が最新)とは、 FPGA が搭載されたボード上の基板 (PCB) 設計において、デカプリングコンデンサーの適切な容量、数、形状の目安を算出するためのツールです。

PDNのソフトDLとマニュアルはこちら↓

PDNツールで算出された容量を目安に、電源デバイスを最適化し、場合によっては容量を変更することで、 FPGA、電源デバイス双方にとって適切な容量を手軽に算出することで基板設計の作業効率を大幅にアップさせることができます。

今回もCyclone V SoCをベースにご紹介していきます。

それでは早速、PDN ツール の使い方を見ていきましょう。

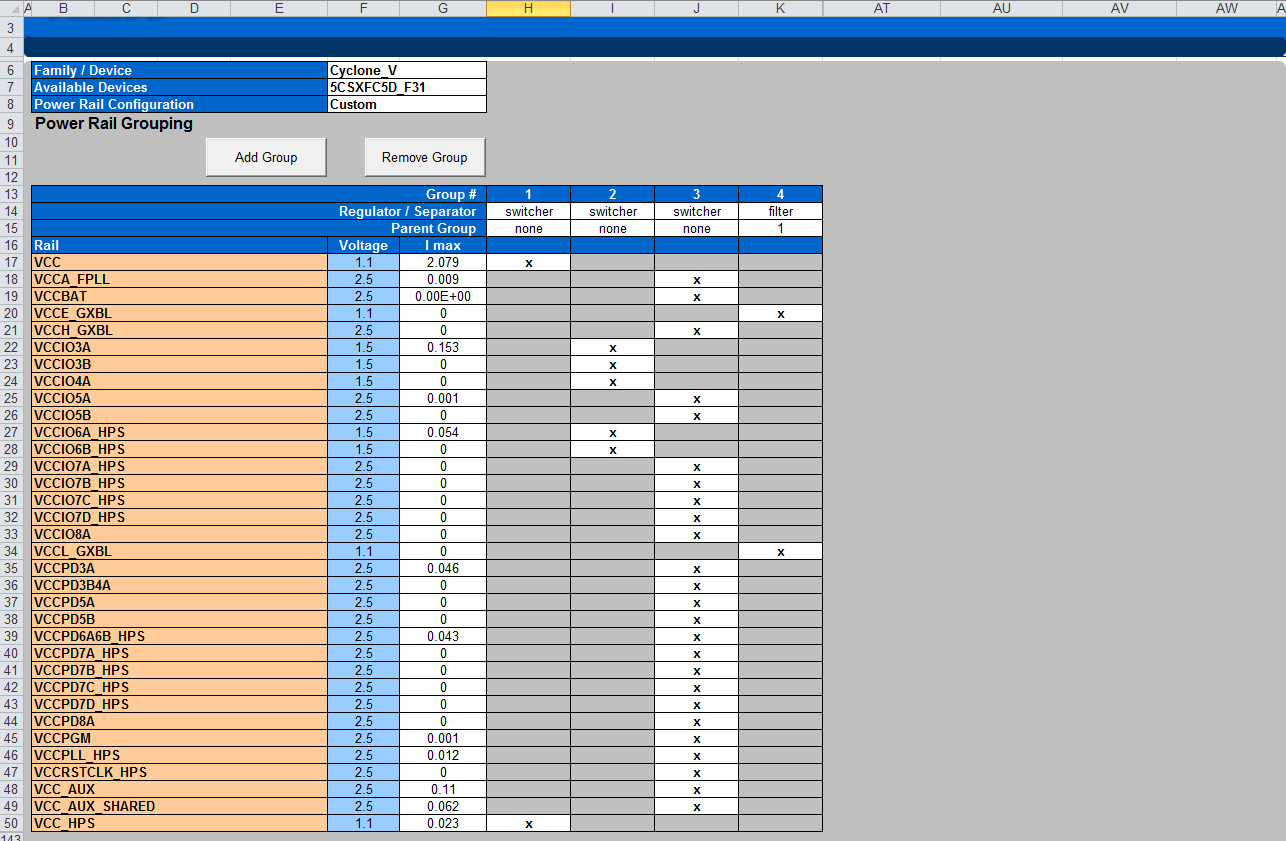

ステップ1: FPGAの選定をおこなう

ファミリーと品番を選定し電源構成を確定します。

ステップ2: Early Power Estimator (EPE) で算出した電源の構成と数値を入力

EPEで算出した数値を入力し、電源デバイス or Filterを選定、X or X/relatedを選択して電源構成を作成

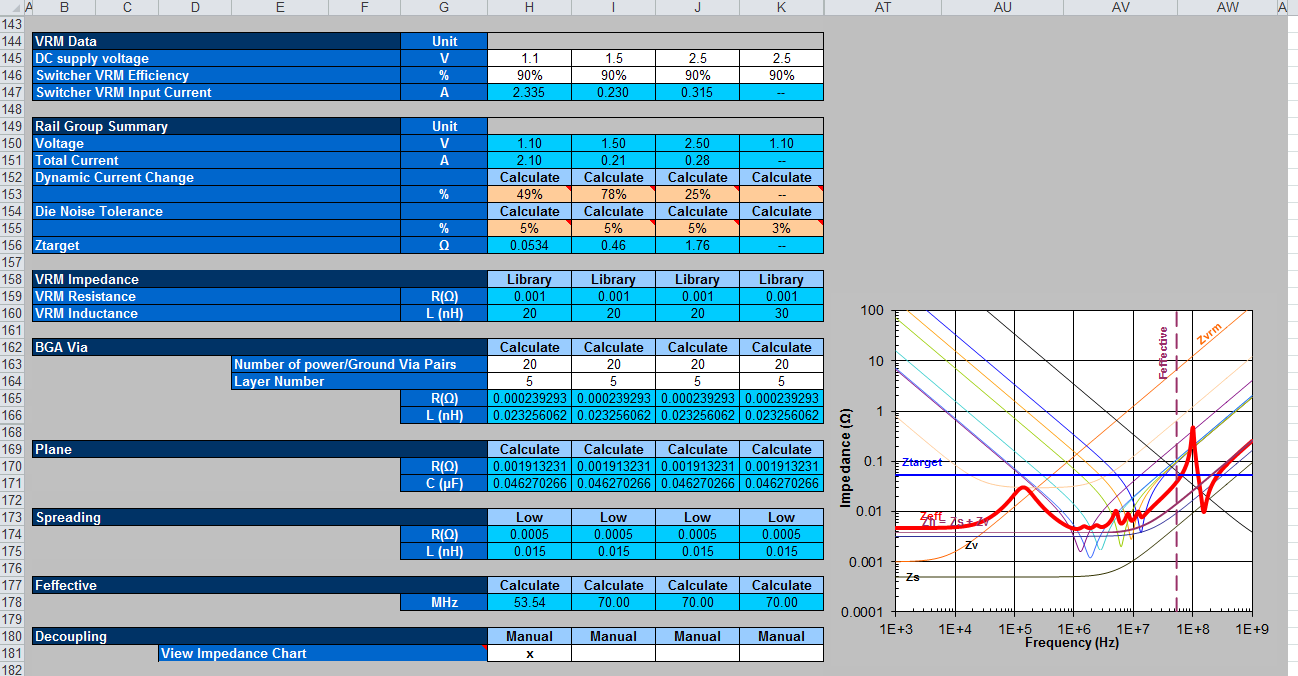

ステップ3: 電源デバイス、レギュレーターの選択、Viaの数、抵抗値、基板層の数などを選択

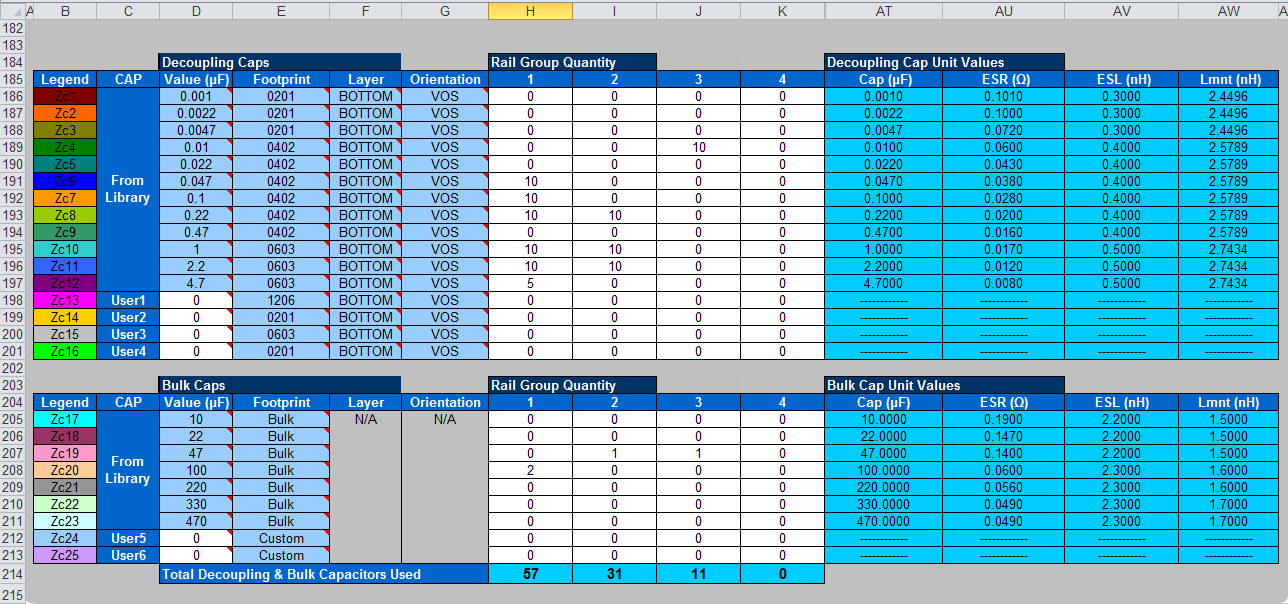

ステップ4: キャパシターの数を入力

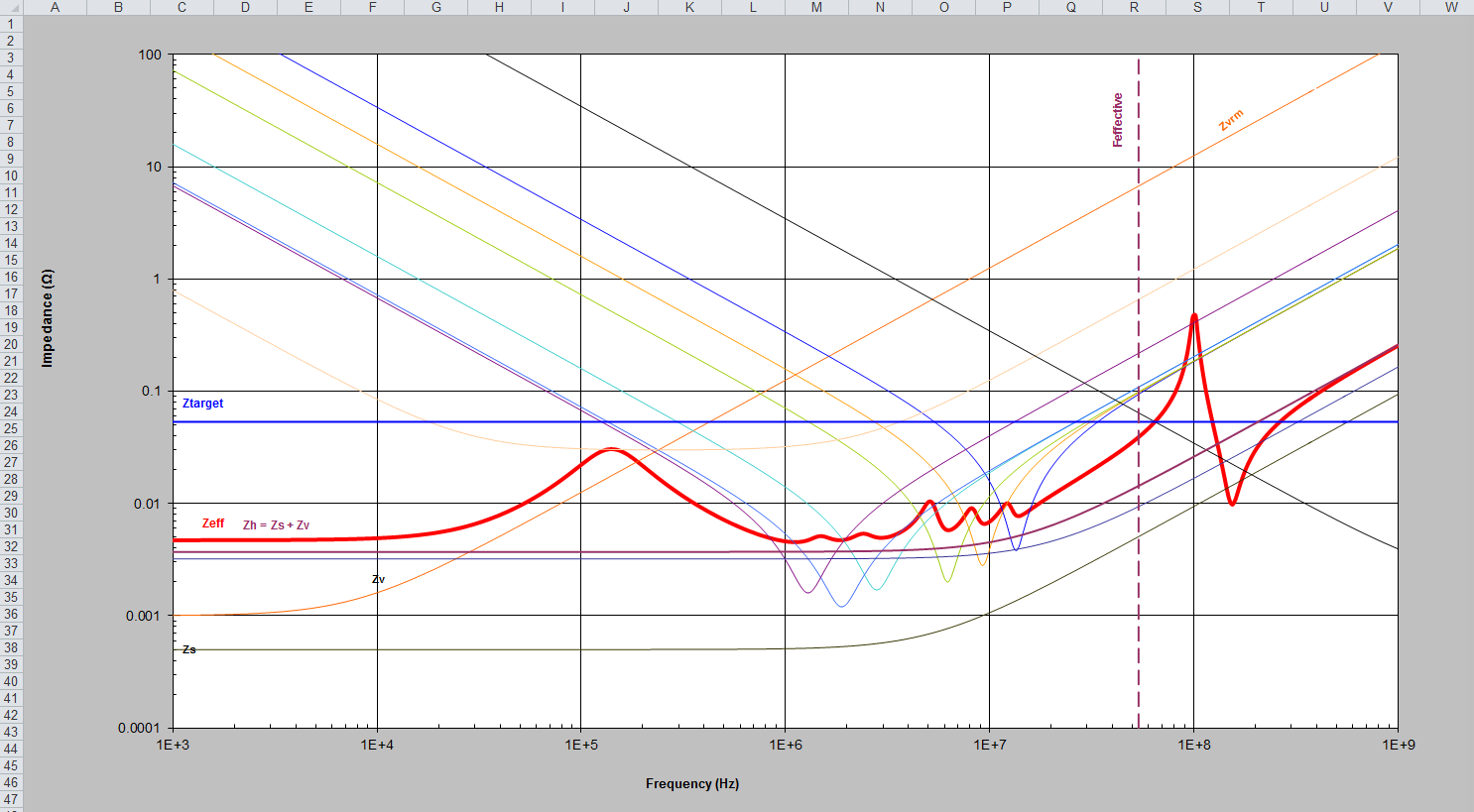

ステップ5: PDNツール上の対数グラフ(縦軸:インピーダンス 横軸:周波数)を確認しZeff値が規定を満たすようキャパシター数を調整

インテル社が提供しているPDNツールを使うことにより手軽にデカプリングコンデンサーの容量、数、形状の目安を算出することで、 FPGAを搭載するアプリケーションの電源回路設計に活用していただければ益々の効率化を図ることができます。

- PDNツールの設定方法の例については以下動画を確認 YouTubeのビデオ(英語)