旧タイトル『DS-5 活用テクニック~トレース機能の使い方』のアップデート版です。

インテル® SoC FPGA 向けのソフトウェア統合開発環境として標準採用される Arm 純正ツールが Arm® DS-5 for Intel® SoC FPGA Edition (DS-5) から Arm® Development Studio for Intel® SoC FPGA Edition (Arm® DS) へと変更になりました。Arm® DS は DS-5 の後継製品となっており使い勝手は大きくは変わりません。このシリーズ記事の内容も Arm® DS / DS-5 両方に適用できるものが大半ですが、違いがある箇所はその旨明記する形でアップデートしています。

***

この記事では、インテル® SoC FPGA 向けのソフトウェア統合開発環境として利用可能な Arm® DS / DS-5 の使い方に関する補足情報を記載します。

今回は、Arm® DS / DS-5 を使用してインテル® SoC FPGA デバイス上で実行しているソフトウェアの命令トレースを取得する方法を紹介します。トレース機能で CPU の命令実行履歴をトレースすることにより、不具合など事象発生に至るまでのソフトウェアの詳細動作を時系列を遡って確認することができます。

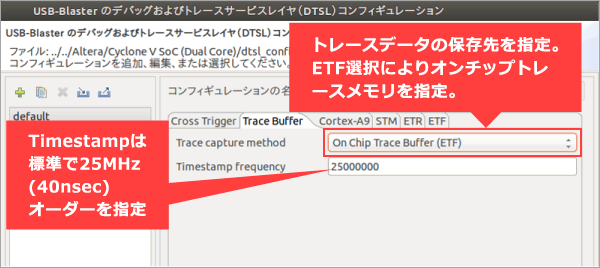

なお、この記事で紹介する方法では、トレースデータの保存先に Embedded Trace FIFO (ETF) と呼ばれるオンチップのトレース専用メモリー(サイズ32KB)を使用します。追加の機材やハードウェアを用意することなく、JTAG デバッグが行えるターゲット環境のみでご利用いただけます。この記事で扱っていないオプション設定など、トレース機能に関する詳細情報については、Arm® DS / DS-5 のマニュアルを参照してください。

Arm® Development Studio ドキュメント・ページ(Arm® Developer サイト)

DS-5 ドキュメント・ページ(Arm® Developer サイト)

トレース機能の有効化(DTSL コンフィギュレーション)

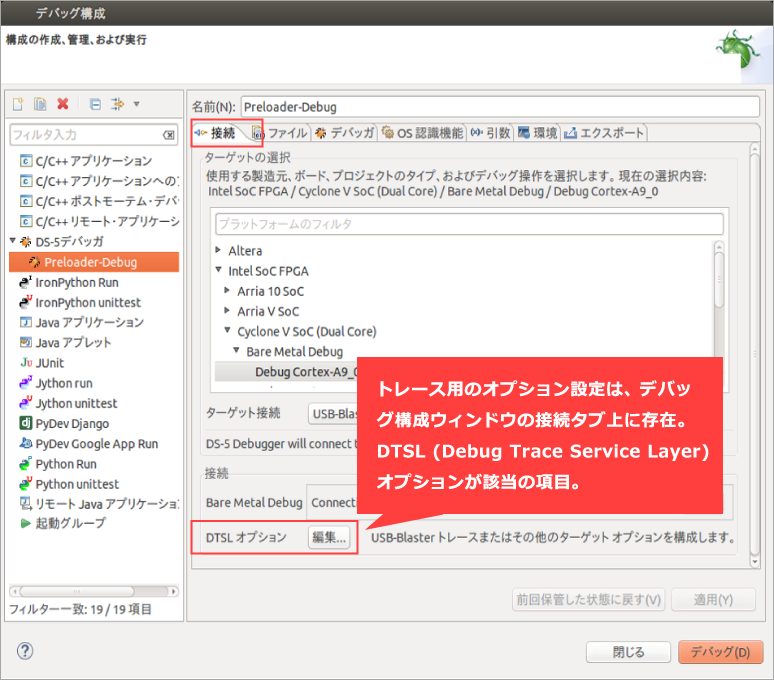

Arm® DS / DS-5 のトレース機能を使用するためのオプション設定は、デバッグ・コンフィギュレーション(デバッグ構成)の [接続] タブ上に用意されている DTSL (Debug Trace Service Layer) オプションから行います。既存のデバッグ・コンフィギュレーション設定に、DTSL オプションの編集を加えるだけでトレース機能が使用可能になります。

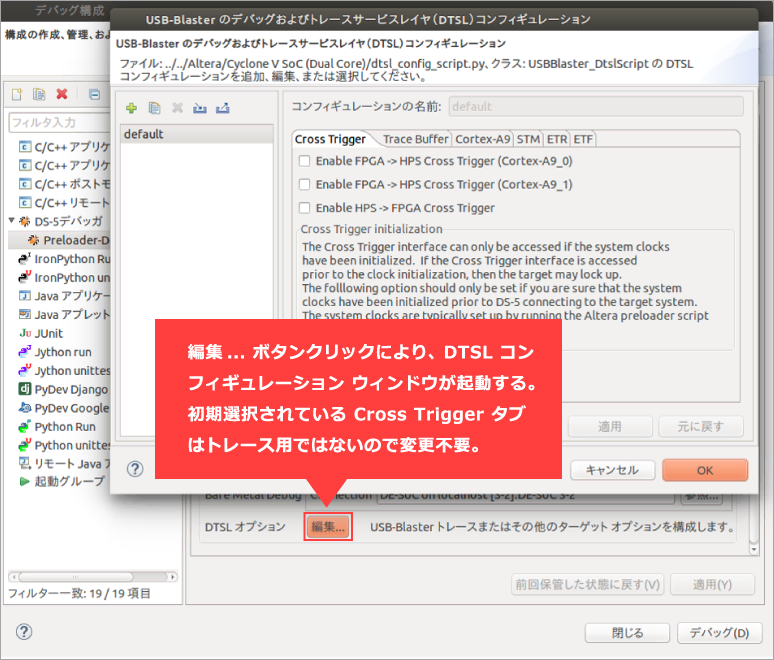

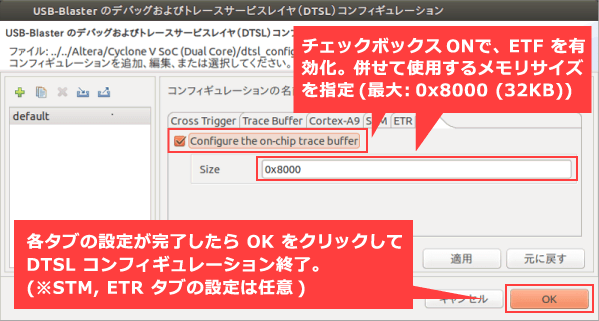

DTSL コンフィギュレーション起動

DTSL オプションの [編集...] ボタンをクリックすることで該当のオプション設定ウィンドウ(DTSL コンフィギュレーション)が起動します。初期選択されている [Cross Trigger] タブは、トレースとは別のデバッグ機能に関するオプション設定用となので編集不要です。その他のタブ上に用意されているオプションを編集することでトレース機能を有効化します。

[Trace Buffer] タブ

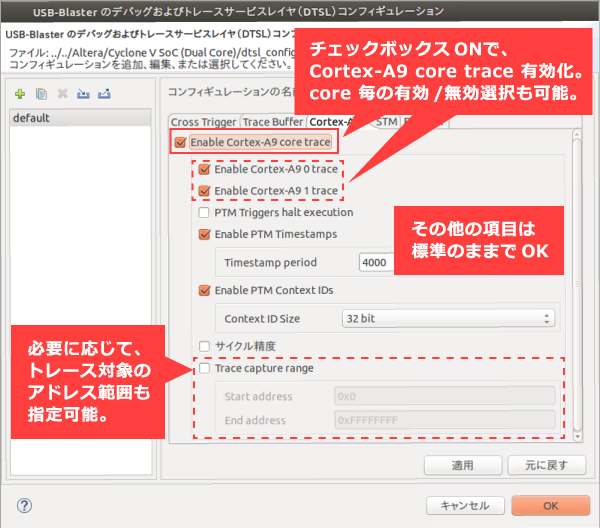

[Cortex-A9] タブ

[STM] タブ / [ETR] タブ

これらのタブは編集不要です。

[STM] タブでは System Trace Macrocell 有効/無効の選択が行えます。CPU の命令トレース以外のトレースイベントを記録したい場合に有効化します。[ETR] タブはトレースログの保存先に ETR を選択した場合のみ設定が必要となります。ETR の場合はトレースログの保存先が SDRAM になるので、オプション項目としてトレースログ保存先のアドレスなどが含まれます。

[ETF] タブ

全てのタブのオプション設定が完了したら [OK] ボタンをクリックして DTSL コンフィギュレーションを終了します。あとはデバッグ開始するのみです。

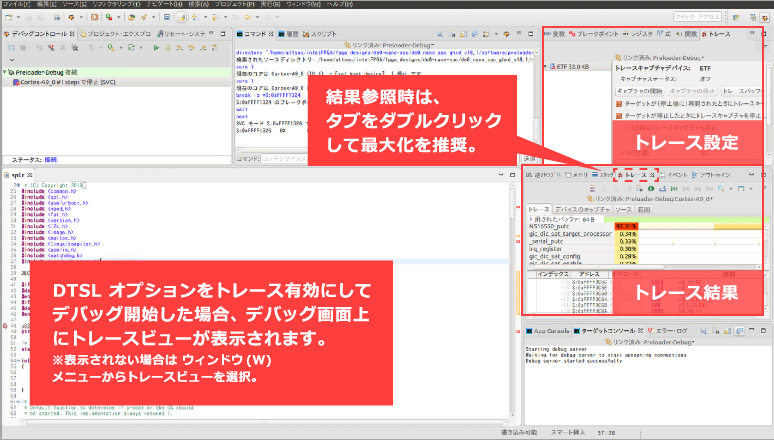

トレースビューの追加

Arm® DS の場合、標準の画面配置上にはトレース機能で使用するビューが表示されていません。Arm® DS の画面上部のメニュー『 Window → Show View → トレース 』より、トレースビュー(トレース結果の表示ウィンドウ)を追加してください。同様に『 Window → Show View → トレース制御 』よりトレース制御ビュー(トレース設定用のウィンドウ)も追加可能です。

トレースログの参照方法

デバッグ開始以降、CPU が動作停止(ブレイク)する毎にトレースビューの表示内容が最新のトレースログで更新されます。通常は以下のイメージのように、サブウィンドウとしてトレースビューが表示されます。

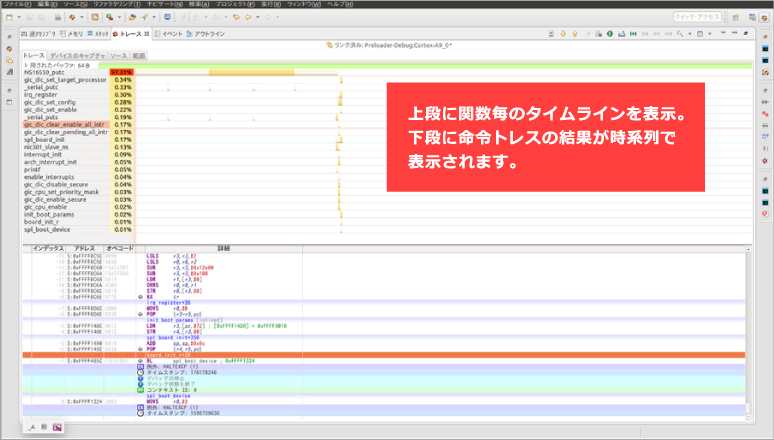

以下、トレースビューのタブをダブルクリックして最大化したイメージです。

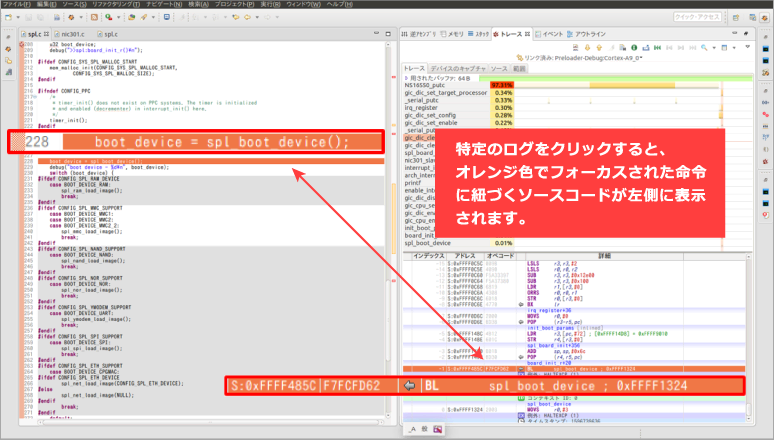

さらに、特定のトレースログをクリックすると以下のようにソースコードとの対比も可能になります。

以上、今回はトレース機能の使い方を紹介させて頂きました。簡単な設定のみで利用できるので、ぜひデバッグの際に活用してみてください。

おすすめ記事/資料はこちら

Arm DS 活用に関する記事一覧

SoC FPGA 関連の記事や資料

インテル® FPGA の SoC FPGA

インテル® FPGA の開発フロー/FPGA トップページ