こんにちは。

マクニカでインテル® FPGA 製品の技術サポートをしている インテル・F・ハナコ です。

Quartus® Prime でコンパイルを実行するときに、こんなことを考えたことがありませんか?

「パズルのピースをはめ込んでいくように、各エンティティを配置させたいな」

「あるエンティティだけを柵で囲って、配置が散乱しないようにしたい。」

そんなときには、Logic Lock(ロジック・ロック)と言う手法を使います。

Logic Lock は、エンティティのレイアウトをユーザー自ら指定することになるため、Quartus Prime コンパイラの作業効率もアップし、コンパイル時間の最適化が期待できます。また、インクリメンタル・コンパイル手法と併用することで、さらに生産性の向上を行うことができます。

ここでは、Logic Lock の基本的な手順をご紹介します。

Logic Lock のサポート環境

Logic Lock が使用できる環境を以下に示します。

| 対応する Quartus Prime |

Quartus Prime Pro Edition / Quartus Prime Standard Edition ※ Lite Edition はサポート対象外 |

| 対応する デバイス・ファミリ |

Quartus Prime Pro および Standard Edition がサポートするデバイス・ファミリ |

表1. Logic Lock のサポート環境

Logic Lock が有効な適用例

Logic Lock は、デザイン・フローのさまざまな場面で適用でき、デザインの生産性向上に役立ちます。例えば、

- ある下位エンティティのセルを点在させずにある程度まとまって配置させたい

- 担当するエンティティごとに配置エリアを決めておき、最終的に統合したときに配置のコンフリクト(衝突)を軽減したい

このようなときに、大きなメリットが得られます。

Logic Lock リージョン (領域) とは?

配置を指定したいエンティティに対して Logic Lock リージョン(領域)を作成し、デザインのレイアウトをコントロールします。

物理的な枠組みのため、周辺エンティティにデザインやレイアウトの変更があっても、Logic Lock リージョン指定されたエンティティの配置は枠組みを出てしまうことがない = 影響を受けることがありません。

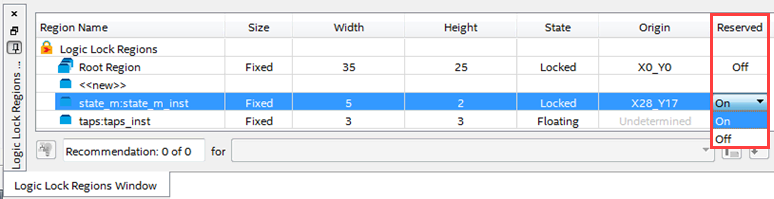

Reserved Logic Lock リージョン

指定した Logic Lock リージョンに割り当てたエンティティとノードのみを配置することができ、他のエンティティのリソースが混在して配置することを防止します。

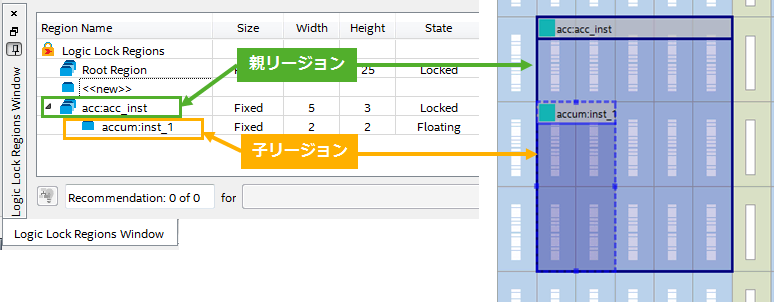

親リージョン/子リージョン(Standard Edition のみ)

Logic Lock リージョンは、親と子の関係(いわゆる “入れ子“)を構築できます。親リージョンを移動すると関連付けられている子リージョンも自動的に移動します。子リージョンは親リージョン内において、浮動配置あるいは固定配置を定義できます。

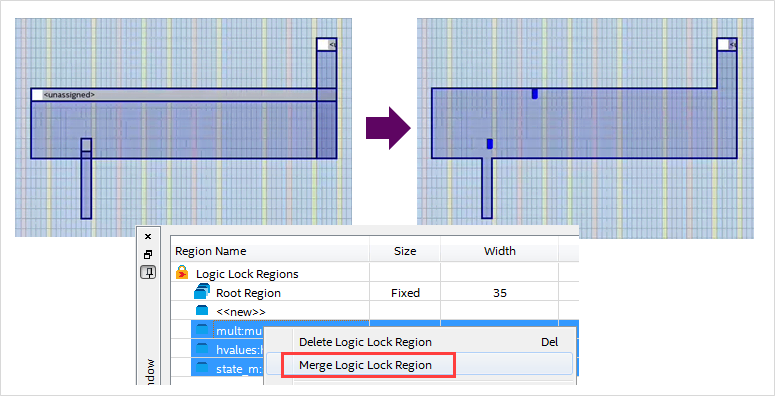

リージョンのマージ

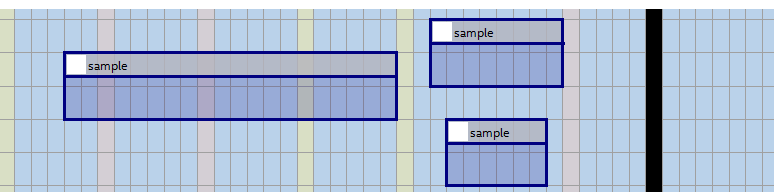

複数のリージョンをマージして矩形的な領域を指定することができます。

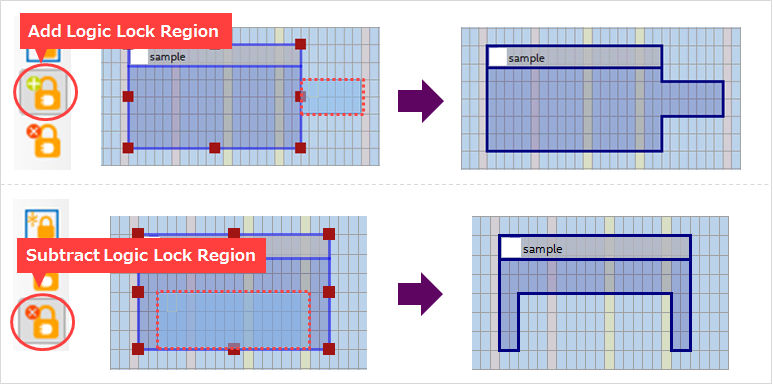

リージョンの形状のカスタマイズ

作成済みのリージョン形状に領域の追加や削除ができ、オリジナルで矩形領域を指定することができます。(Pro Edition のみ)

この機能を利用して、非連続な領域をリージョンに指定することが可能です。

Standard Edition の場合は Add/Subtract Logic Lock Region 機能は使用できませんが、 隣り合っていない非連続な複数のリージョンを Merge Logic Lock Region 機能により一つのリージョンに設定することで、上図のように非連続なリージョンを定義することが可能です。

Logic Lock リージョンを作成する

Quartus Prime プロジェクトの下位エンティティに対して Logic Lock を設定するには、Logic Lock リージョン を作成します。デザインの下位エンティティに対して領域の枠組みを指定し配置させるので、エンティティに必要なロジック・リソース数を把握しなければなりません。そのため、事前に Analysis & Synthesis 以上のプロセス を実行、完了しておきましょう。

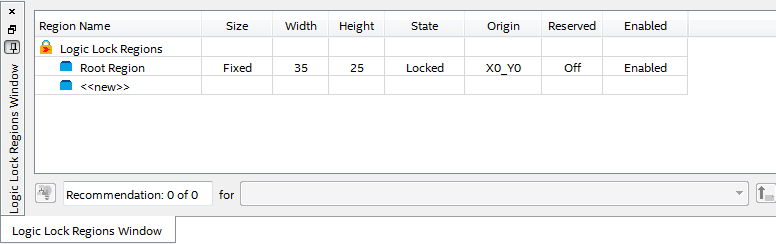

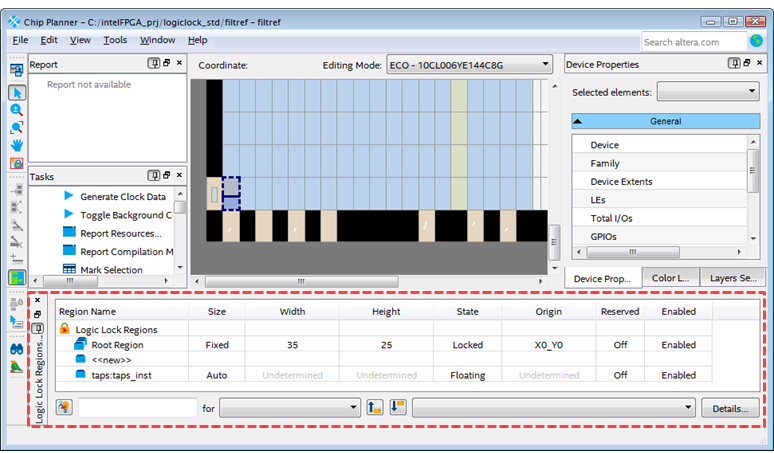

1. リージョンを作成するための Logic Lock Regions Window(Assignments メニュー)を表示させます。

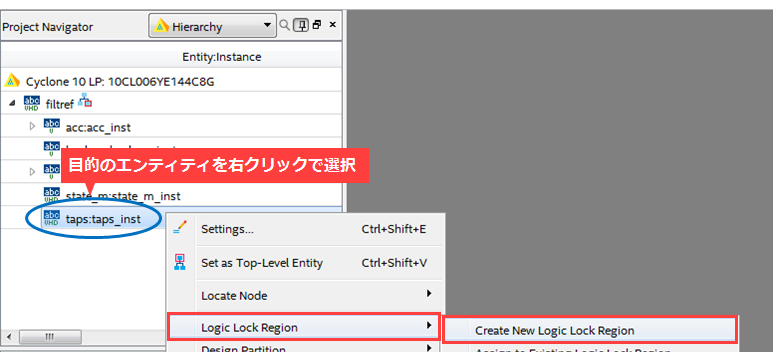

2. Project Navigator ウィンドウから Logic Lock 指定したいエンティティを右クリック > Logic Lock Region > Create New Logic Lock Region

を選択します。

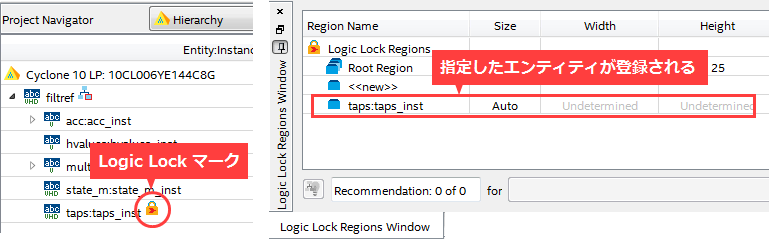

LogicLock Regions Window に指定したエンティティが登録され、Project Navigator ウィンドウ上にマークが付いたことを確認します。

3. Tools メニュー > Chip Planner を起動します。

ここからは、配置を意識した設定を行うため、Chip Planner 上で Logic Lock Regions Window を使用します。

もし Chip Planner に Logic Lock Regions Window が表示されていない場合には、

Chip Planner 上の View メニュー > Logic Lock Regions Window を選択してください。

4. リージョンに各種設定をします。

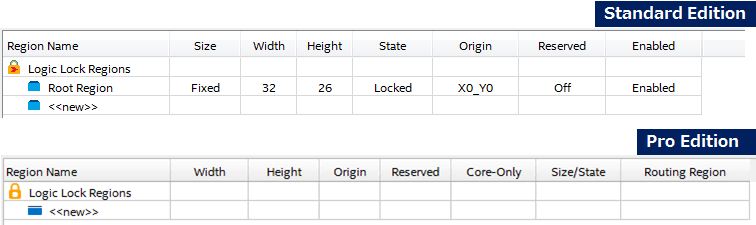

| カラム名 | 設定値 | 概 要 |

| Size (Standard のみ) |

Auto | Quartus Prime がエンティティのコンパイル結果に基づいてサイズを決定します。 |

| Fixed | ユーザーがリージョンのサイズを指定できます。 | |

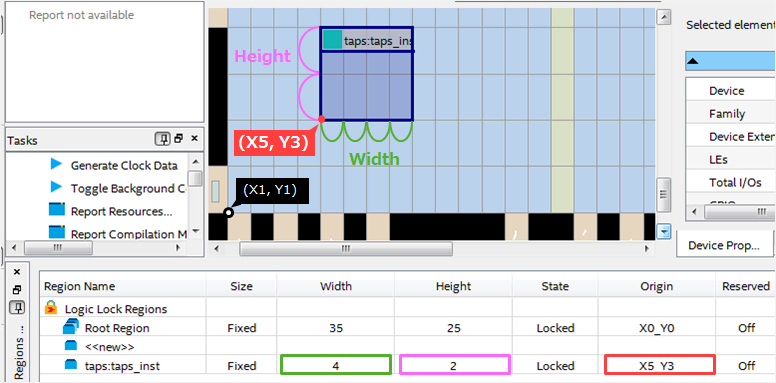

| Width | 列の数 | 領域の横幅を設定します。 |

| Height | 行の数 | 領域の高さを設定します。 |

| State (Standard のみ) |

Floating | Quartus Prime がデバイス上の領域の位置を決定します。Chip Planner 上でリージョンの境界は破線で表示されます。 |

| Locked | ユーザーが指定した位置に固定されます。ロックされたリージョンの Size は Fixed でなければなりません。Chip Planner 上でリージョンの境界は実践で表示されます。 | |

| Origin | 位置/ Undetermined |

Chip Planner 内での Logic Lock リージョンの位置を設定します。State カラムが Floating の場合は Undetermined と表示されます。 |

| Reserved | Off/On | リージョンから他のエンティティのリソースの配置を除外します。Pro の場合、Routing Region には適用できません。 |

| Enabled (Standard のみ) |

Enabled/Disabled | リージョン設定の有効/無効に指定します。 |

| Core-Only (Pro のみ) |

Off/On | リージョンからペリフェラルのリソース (I/O, HSSIO, PCIe, PLL など) を除外します。 |

| Size/State (Pro のみ) |

Fixed/Locked | ユーザーがリージョンのサイズと配置を指定します。 |

| Auto/Floating | Quartus Prime がリージョンのサイズと配置を決定します。 | |

| Routing Region (Pro のみ) |

Unconstrained (default) | フィッターがデバイス上で使用可能なルートを使用できるようにします。 |

| Whole Chip | Unconstrained(制限なし)と同じですが、プロジェクトの設定ファイル(.qsf)に制約を書き込みます。 | |

| Fixed with Expansion | 配置領域のアウトラインに従います。 ルーティング領域は、配置領域よりも大きい数の行/列でスケールされます。 | |

| Custom | リージョンの周囲にルーティング領域をカスタマイズで作成できます。ルーティング領域は Chip Planner 上で独立して移動することが可能で、さらに、Shiftキーにより配置と配線の領域の両方を選択し移動することも可能です。 |

表2. Logic Lock リージョンの属性

コンパイルを実行する

リージョンの設定が完了したら、コンパイルを実行します。(必要に応じてインクリメンタル・コンパイルを適用してください。)

Processing メニュー > Start Compilation

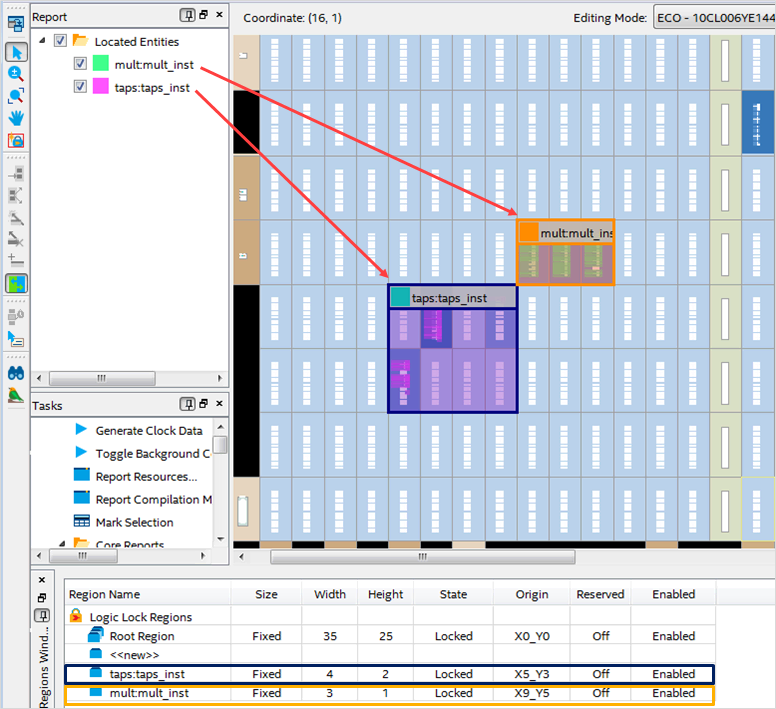

コンパイル結果を確認する

コンパイル完了後、コンパイル・レポートや Timing Analyzer でタイミング要求は満たされていることや、ChipPlanner で配置状態を確認します。

最後に

いかがでしたか?

エンティティ単位でリソースの配置に制約をしたいときには、Logic Lock を上手に活用してみてください。

おすすめ記事/資料はこちら

配置制約した下位エンティティを別プロジェクトへ適用する方法 (概要)

FPGA デザインの一部だけを再コンパイルする方法

インクリメンタル・コンパイルを使ってみよう

インテル® FPGA の開発フロー/FPGAトップページ