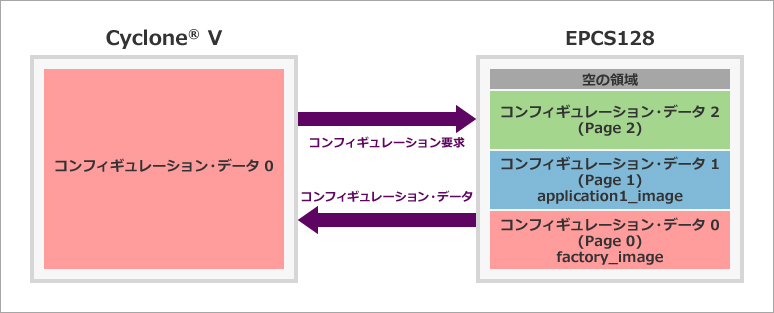

[#1]、[#2] と続いてご紹介してきた EPCQ/EPCQA/EPCS に格納した複数のコンフィギュレーション・データを FPGA が自動で切り替える制御動作を、HDL デザイン(ステートマシン回路)で作成する方法、今回はその [#3] です。

なお、これまでの内容は下記の記事をご覧ください。

FPGA のコンフィギュレーション・データを切り替える方法 HDL 編 [#1/3]

FPGA のコンフィギュレーション・データを切り替える方法 HDL 編 [#2/3]

ステップ2:Page 1 用デザインを作成

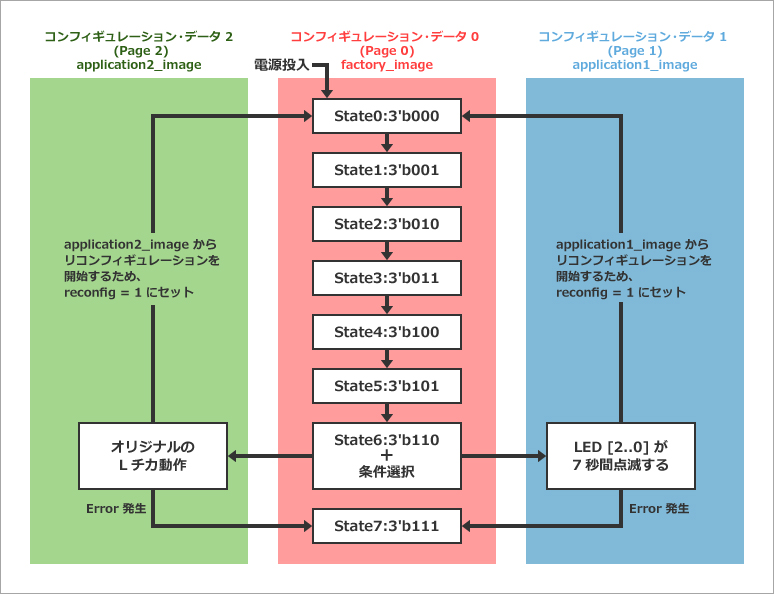

factory_image の遷移先である application1_image(Page 1 に格納)のデザインを作成およびコンパイルし、sof ファイルを生成します。

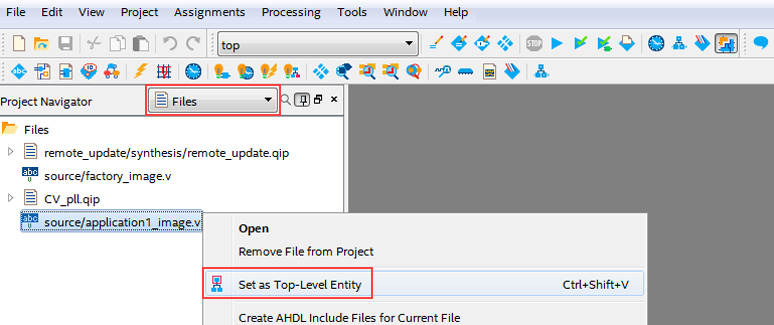

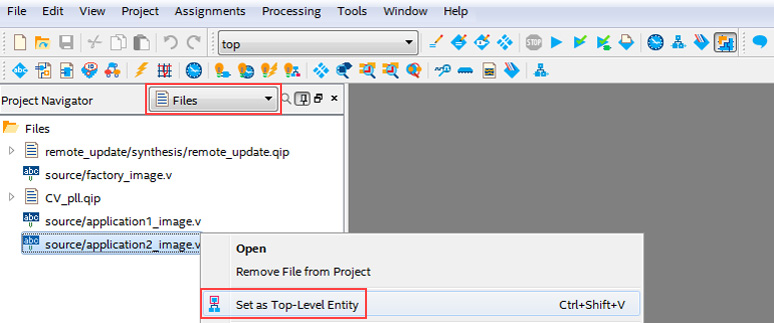

Project Navigator ウィンドウを Files ビューに切り替え、リストから application1_image.v を選択します。右クリック > Set as Top-Level Entity を選択し、プロジェクトの最上位階層モジュールを application1_image へ変更します。

application1_image.v ファイルを開き、以下の修正を行います。

- remote_update モジュールのdata_in のバス幅を24bitに変更

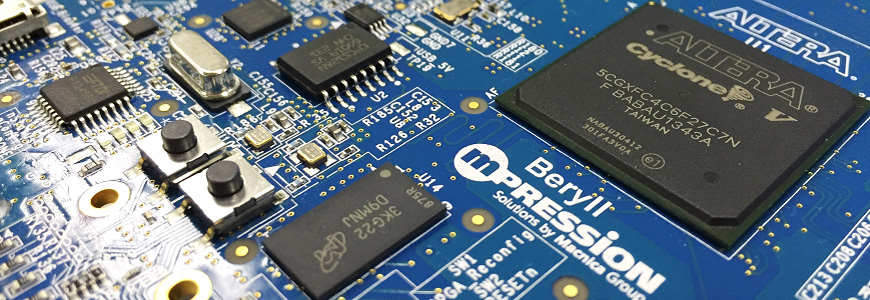

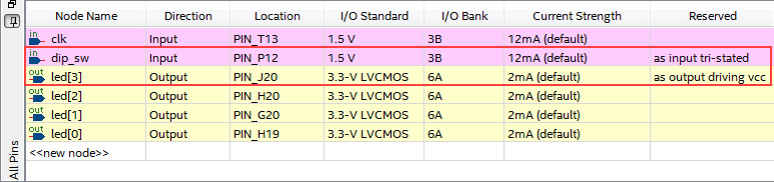

今回は、factory_image、application1_image、application2_image の3つの最上位階層モジュールに対して、プロジェクトを共有しながら作業を行っています(※)。つまり、ピン・レイアウトの制約が共通と言うことになります。そのため、Pin Planner を起動し、このプロジェクトではピン・アサインしていながらも application1_image デザインでは使用していない以下のピンに対して、Reserved Pin オプションを追加で設定します。なお、設定値は使用する評価ボードに応じて選択してください。以下はBeryll ボードに応じた内容です。

- dip_sw の Reserved 項を as input tri-stated に設定

- led[3] のReserved 項を as output driving vcc に設定

Processing メニュー > Start Compilation を実行し、application1_image をコンパイルします。タイミング検証を行い、要求仕様を満たすことを確認します。その後、生成された top.sof ファイルを app1_image.sof としてリネームします。

Programmer で FPGA に app1_image.sof を書き込み、動作を確認しておきましょう。

これで、コンフィギュレーション ROM の Page 1 に書き込む コンフィギュレーション・データ 1 が構築できました!

[ハナコのつぶやき その3. プロジェクトの構成について]

factory_image と application1_image や application2_image は別デザインなので、通常 Quartus® Prime のプロジェクトもそれぞれに用意し、作業しますが、このサンプル・プロジェクトは、Page 0、Page 1 のデザインにおいて動作仕様は異なっても、ともに同じ入出力ピン構成(ピン名、レイアウト etc.)を取っているため、プロジェクトに対する制約(オプション関連)を共有することができます。

そのため 今回のサンプルは、個々にプロジェクトを作成せずに同一プロジェクト内で最上位階層モジュールだけをセットし直しながらコンパイルやプログラミング・ファイル(*.sof)を生成するスタイルになっています。もし、自作で Altera Remote Update IP を用いたコンフィギュレーション・データの切り替えを行う場合は、ボードや動作するアプリケーションの仕様に応じて、プロジェクトを Page ごとに個別で作成してください。

ステップ3:Page 2 用デザインを作成

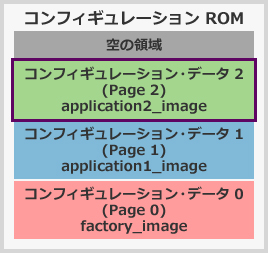

factory_image のもう一つの遷移先である application2_image(Page 2 に格納)のデザインを作成し、コンパイル、実機検証、sof ファイルのリネームを行います。

application2_image をどのような動作仕様にするかは皆さんにお任せしますが、application2_image の動作中に再び Page 0 のイメージに戻る(つまり、リコンフィギュレーションさせる)仕様にするために、Altera Remote Update IP へ reconfig = 1 を発行するようにします。(※ application1_image.v を参考にしてください。)

デザインを作成後、Project メニュー > Add/Remove Files in Project によりプロジェクトに追加登録します。

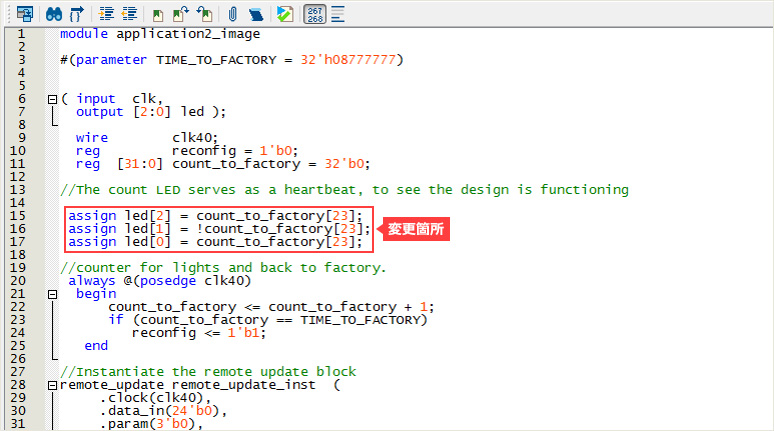

今回は application1_image.v を少しだけリメイクしてLチカの点灯仕様を変更し、application2_image.v を作成してみました。

例えばこんな感じ。(下図参照)

(※ application1_image.v の led[2:0] 点灯パターンを変更しただけ。)

Project Navigator ウィンドウを Files ビューに切り替え、リストから application2_image.v を選択します。

右クリック > Set as Top-Level Entity を選択し、プロジェクトの最上位階層モジュールを application2_image へ変更します。

Processing メニュー > Start Compilation を実行し、application2_image をコンパイルします。

タイミング検証を行い、要求仕様を満たすことを確認します。

その後、生成された top.sof ファイルを app2_image.sof としてリネームします。

Programmer で FPGA に app1_image.sof を書き込み、動作を確認しておきましょう。

これで、コンフィギュレーション ROM の Page 2 に書き込む コンフィギュレーション・データ 2 が構築できました!

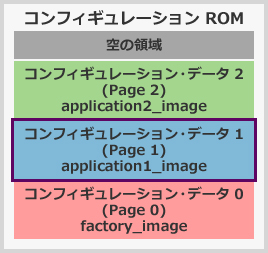

ステップ4:コンフィギュレーション ROM 用のプログラミング・ファイルを作成

3つのコンフィギュレーション・データを混合して、対象のコンフィギュレーション ROM 用のプログラミング・ファイルを作成します。

File メニュー > Convert Programming Files を選択し、ダイアログボックスを起動します。

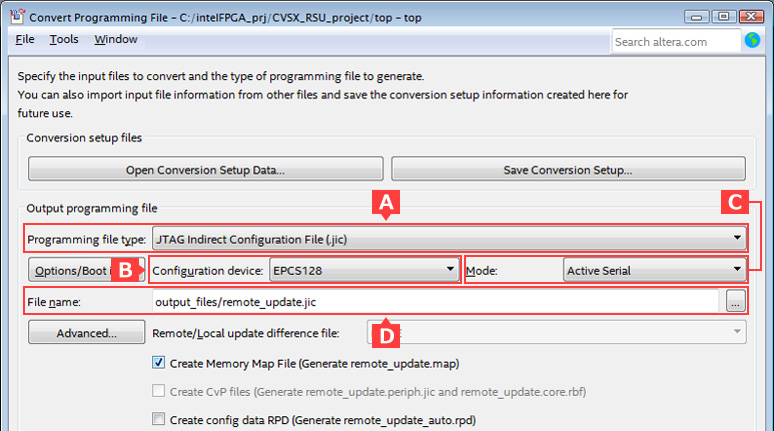

Output programming file セクションにおいて、生成するファイルの内容を設定します。

[A] Programming file type:使用するボードの接続構成に応じたコンフィギュレーション ROM 用プログラミング・ファイルのフォーマットを選択(.pof あるいは .jic)

[B] Configuration device:プログラミングをするコンフィギュレーション ROM

[C] Mode:使用するボードの接続構成に応じたモードを選択

[D] File name:生成するプログラミング・ファイルの保存フォルダおよびファイル名を指定

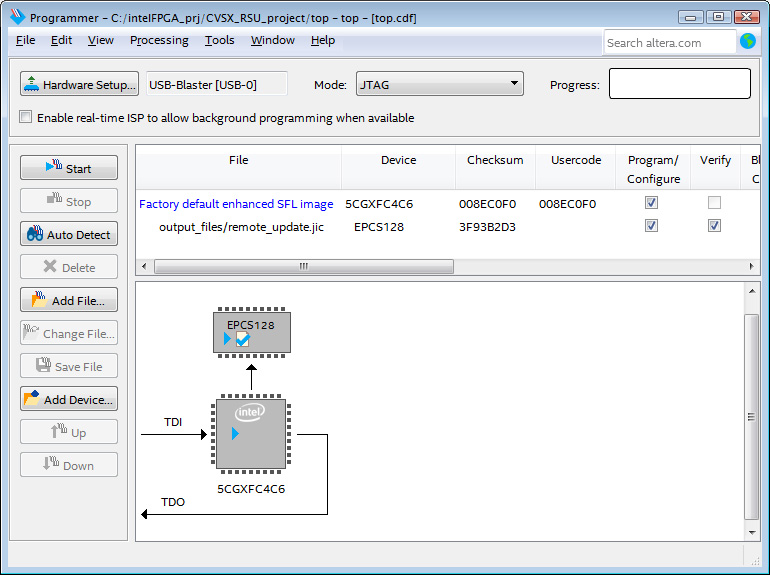

今回使用する評価ボード Beryll は、コンフィギュレーション ROM に対するプログラミング仕様が JTAG Indirect Configuration であるため、以下のように設定します。

[A] Programming file type:JTAG Indirect Configuration File (.jic)

[B] Configuration device:EPCS128

[C] Mode:Active Serial

[D] File name: output_file/remote_update.jic (※ フォルダのパスやファイル名は自由です。)

Create Memory Map File オプションについては、同一ページの [ハナコのつぶやき その5] をご覧ください。

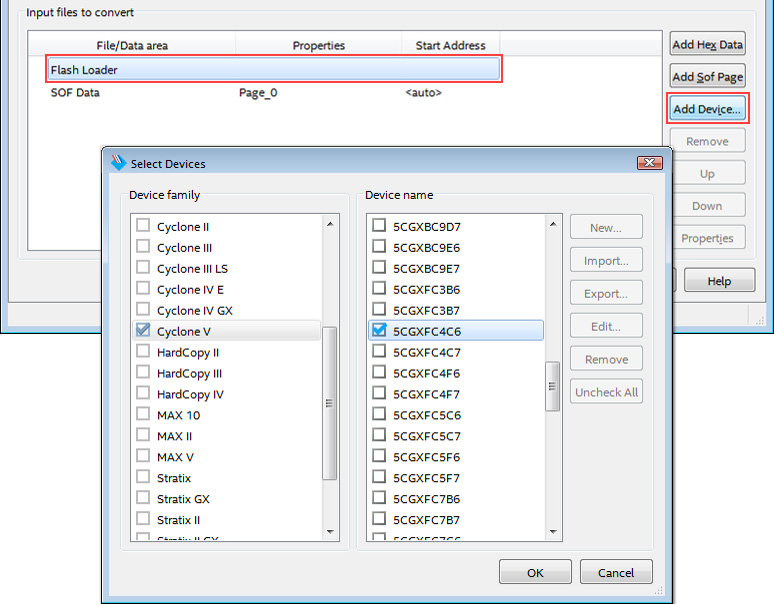

続いて、Input files to convert において、Flash Loader と元データの SOF ファイルをセットします。(※ 生成するフォーマットが .pof の場合には、Flash Loader 行はありません。)

Flash Loader 行を選択後、Add Device ボタンをクリックして FPGA の型番を選びます。

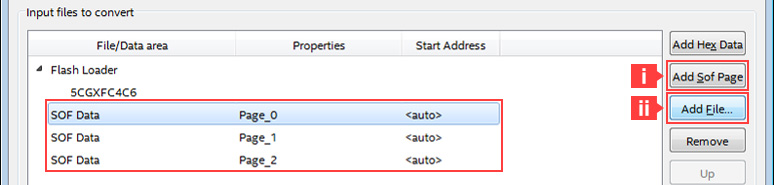

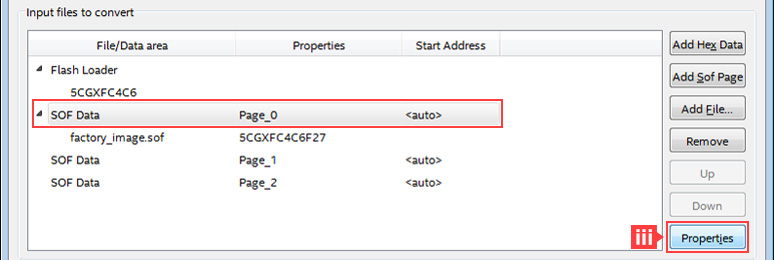

Add Sof Page ボタンをクリックして、SOF Data 行を追加します。(下図 i )今回は、3つのページを用意します。

次に、Page_0 の SOF Data 行を選択し、Add file ボタンをクリックし(下図 ii )、格納する factory_image.sof を設定します。

Page_0 の SOF Data 行を選択し、Properties ボタンをクリックします。(下図 iii )

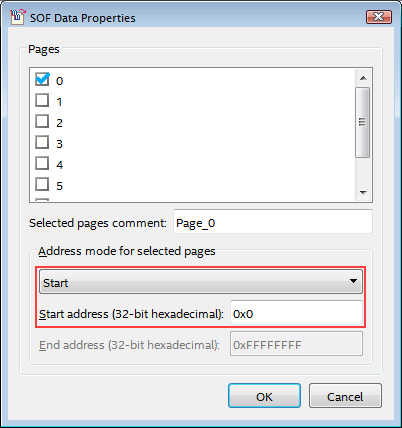

SOF Data properties ダイアログボックスにおいて、Page 0 の Start アドレスを指定します。

- Address mode for selected pages : Start

- Start address : 0x00000000

ここで、End アドレスも指定する場合には、Address mode を Block にし、Start address と End address を入力してください。

[ハナコのつぶやき その4. sof ファイルの圧縮について]

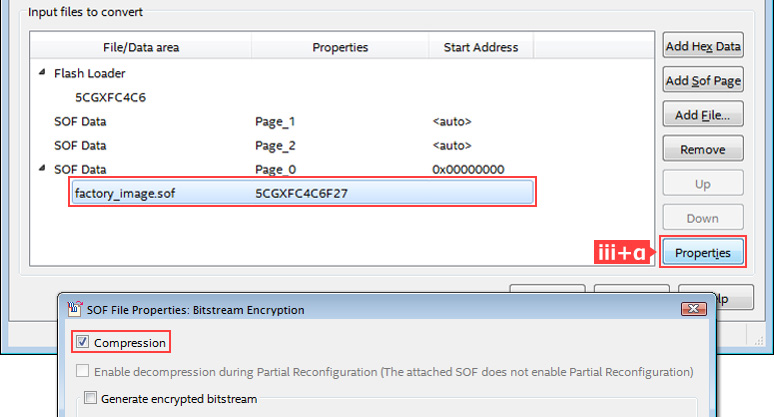

"SOF Data" にセットした各 sof ファイルを圧縮してプログラミング・ファイルを生成することができます。ファイル名を選択し、Properties ボタンをクリックします。(下図 iii+α )必要な場合は、プロパティ画面にある Compression オプションを有効にしてください。

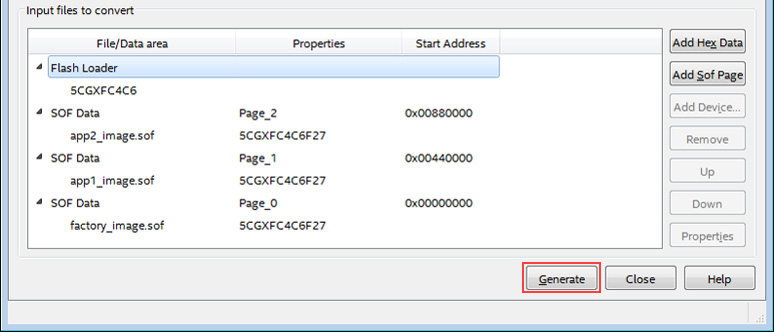

同様に、Page_1 に app1_image.sof、Page_2 に app2_image.sof をセットし、factory_image.v で定義した Start アドレスを設定します。

Generate ボタンをクリックし、Successfully とメッセージが表示されたらファイルが生成完了です!

[ハナコのつぶやき その5. メモリのアドレス・マップ・ファイルについて]

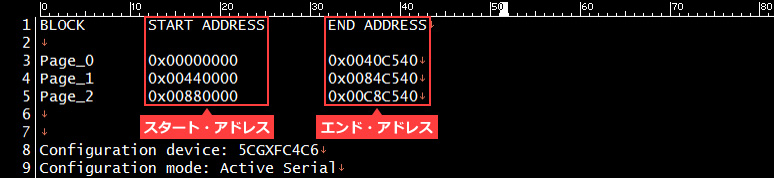

Create Memory map File オプションを有効にしてプログラミング・ファイルを生成すると、同時に、メモリのアドレス・マップ・ファイル(.map)が生成されます。map ファイルはテキスト・エディタで開けます。

ここには、プログラミング・ファイル作成時に指定した各 Page におけるデータのスタートおよびエンド・アドレスが記録されています。

下図は、スタート・アドレスのみを指定(Address mode for selected pages : Start)した際の map ファイルです。この場合 END ADDRESS には格納したデータに使用したアドレスの終了番地が表示されます。

ステップ5:コンフィギュレーション ROM にプログラミングを実行

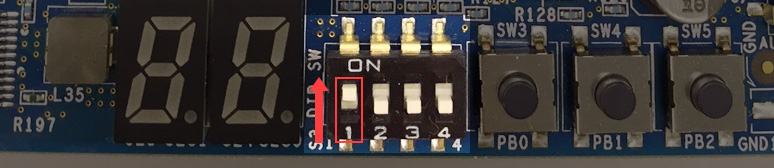

事前に Beryll ボードの DIP スイッチの向きを確認し、初期イメージの遷移先に application1_image が選択されるようにしておきます。

Programmer (Tools メニュー)を起動し、必要な設定(Hardware Setup、Mode 選択、プログラミング・ファイルのセットなど)を行い、Start ボタンよりプログラミングを実行します。

ステップ6:実機で動作を確認

Beryll ボードは、nCONFIG、nSTATUS、CONF_DONE、INIT_DONE の各ピンが抵抗を介してプルアップされていて、かつ LED も接続しているため、コンフィギュレーションの状態を簡単に目視することができます。そこも併せて動作確認します。

Beryll ボードの回路図はこちらから入手できます。

Beryll - Cyclone® V GX ベーシックボード

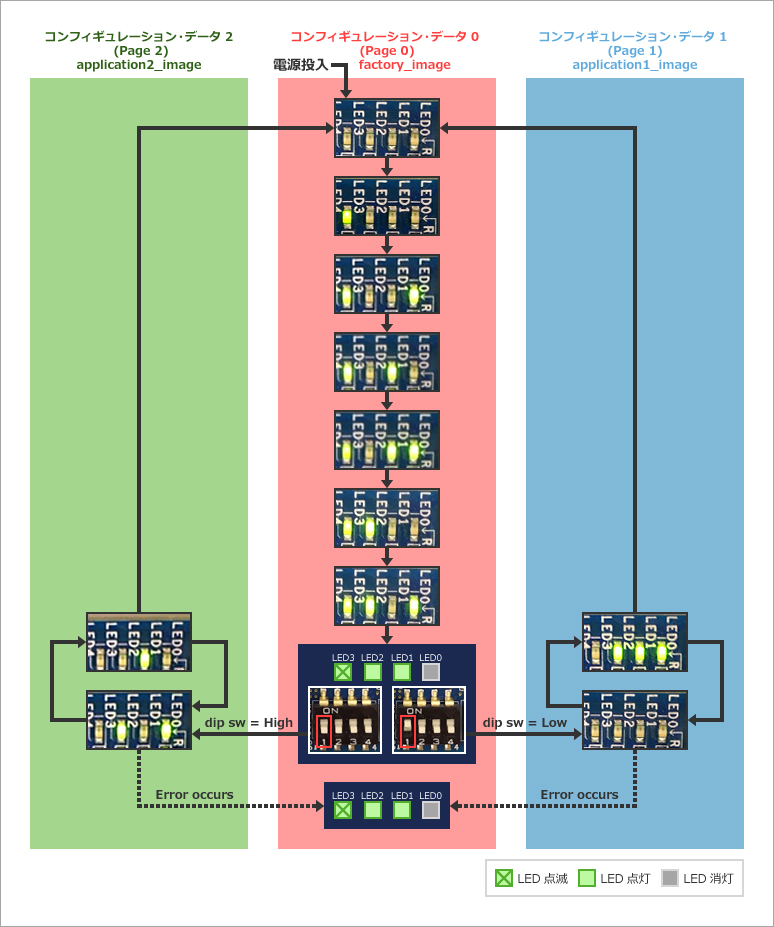

Beryll ボードの電源を投入!

はじめ、Page 0 に格納した factory_image が動作します。

その後、Altera Remote Update IP へのリコンフィギュレーション命令の箇所まで来ると、ユーザー I/O に接続された LED は消灯し、同時に CONF_DONE、INIT_CONF に接続された LED も一度消灯します。

そして自動的に再コンフィギュレーションが行われ、CONF_DONE、INIT_CONF の LED は再点灯し、Page 1 に格納した application1_image の動作へ移行したことが確認できます。

application1_image が動作し、Altera Remote Update IP へのリコンフィギュレーション命令まで来ると、先ほどと同様に CONF_DONE、INIT_CONF、ユーザー I/O の LED は消灯し、自動的に再コンフィギュレーションが行われ、CONF_DONE、INIT_CONF の LED は再点灯。factory_image へ遷移したことが確認できます。

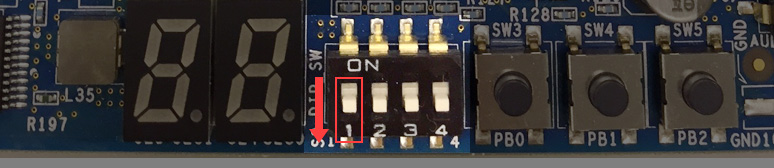

ここで、遷移先を application2_image に変更するため、DIP スイッチの向きを変えます。

すると、factory_image の動作から再コンフィギュレーションが行われ、Page 2 に格納した application2_image の動作へ移行し、Altera Remote Update IP へのリコンフィギュレーション命令まで来ると、factory_image へ遷移したことが確認できます。

できました!成功です!

なお今回、Lチカ程度の単純動作であるためエラーステートは発生せず、エラーを示す LED 点灯はありませんでした。

また、State 6 を示す LED 点灯は、Altera Remote Update へのリコンフィギュレーション命令と同時であるため目視できるレベルではなく撮影はできませんでしたが、DIP スイッチの状態に応じて、指定のイメージ動作であることを確認できました。

最後に

このように、サンプル・デザインを参考に Altera Remote Update IP を組み込んで制御すれば、簡単にコンフィギュレーション・データを切り替える仕様を構成することができます。

皆さんもお試しください。

おすすめ記事/資料はこちら

FPGA のコンフィギュレーション・データを切り替える方法 HDL 編 [#1/3]

FPGA のコンフィギュレーション・データを切り替える方法 HDL 編 [#2/3]

FPGA のコンフィギュレーション・データを切り替える方法 HDL 編 [#3/3]

FPGA / CPLD の一般的な開発フロー