[#1] に続きご紹介している、EPCQ/EPCQA/EPCS に格納した複数のコンフィギュレーション・データを FPGA が自動で切り替える制御動作を、HDL デザイン(ステートマシン回路)で作成する方法、今回はその [#2] です。

なお、これまでの内容は下記の記事をご覧ください。

FPGA のコンフィギュレーション・データを切り替える方法 HDL 編 [#1/3]

ステップ1:Page 0 用デザインを作成

Page 0 に書き込むためのデザインを作成し、コンパイル、実機検証、sof ファイルのリネームを行います。

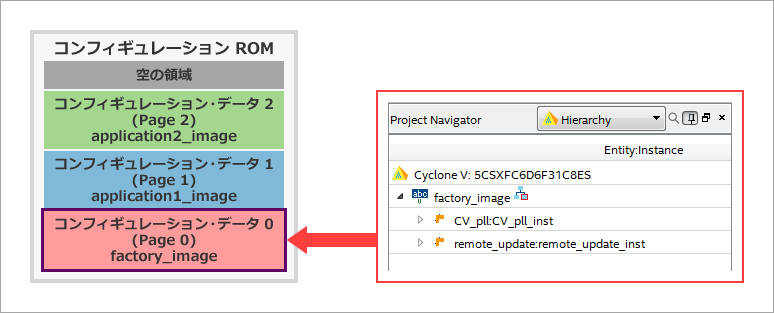

現在 Project Navigator ウィンドウにセットされているサンプル・プロジェクトの最上位デザインが、factory_image であることを確認します。

1. サンプル・プロジェクトの設定を評価ボードに応じて編集

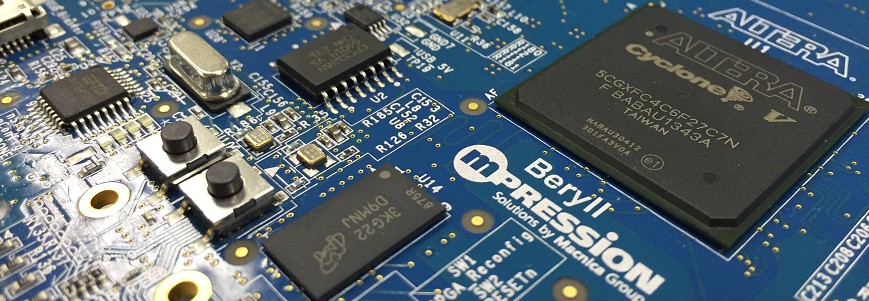

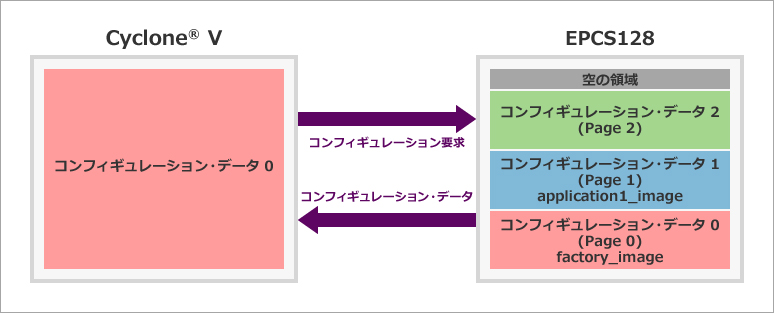

今回は Cyclone® V (5CGXFC4C6F27C7) と EPCS128 が搭載された Mpression 製の Beryll ボードを使用します。

サンプル・デザインのプロジェクトは Cyclone® V SoC Development Kit (5CSXFC6D6F31C6N、EPCQ256 搭載) 向けに構成されているので、Beryll ボードに対応させるため、制約設定に対して若干の修正を行います。

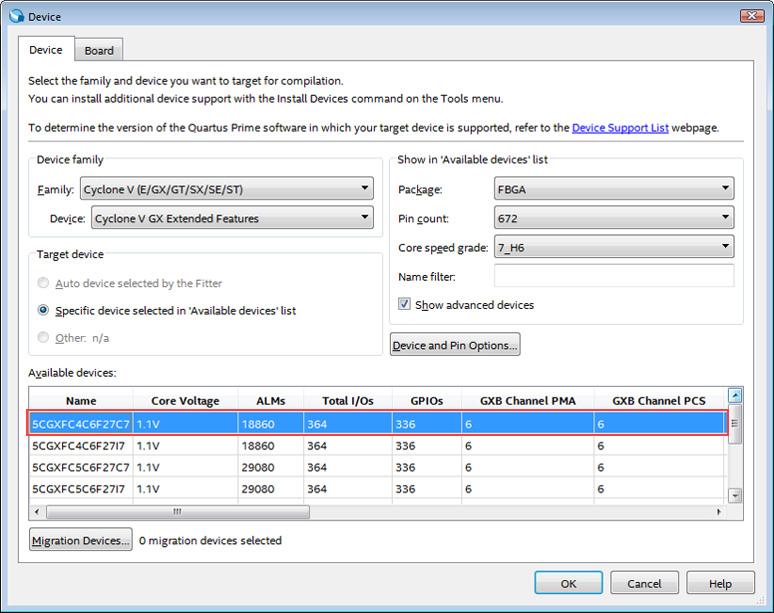

1-1. デバイスの型番を変更

Assignments メニュー > Device において、5CGXFC4C6F27C7 に変更します。その際、ピン・レイアウト情報を削除するかを問われますが、今回は評価ボードが異なるためピン・レイアウトも変更するので、Yes(アサイン情報を削除する)を選択してください。

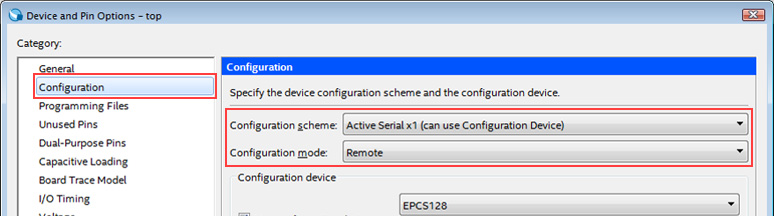

1-2. コンフィギュレーション・モードの設定

Device ダイアログボックス内の Device and Pin Options ボタンをクリックし、Configuration カテゴリにおいてConfiguration scheme を選択し、Configuration mode を Remote に指定します。今回使用する EPCS128 の場合、Configuration scheme は Active Serial x1 (can use configuration Device) を選択します。

また、Configuration device 欄を設定する必要はありません。今回必要なプログラミング・ファイルは、複数のコンフィギュレーション・データを混合するため、別途 Convert Programming Files 機能で作成します。

※ その他、Unused Pins や Voltage カテゴリなどのオプションは使用する評価ボードの仕様に応じて変更してください。

2. サンプル・デザインを編集

このプロジェクトは、2つの IP コア(CV_pll、remote_update)と最上位階層(factory_image)の3ファイルで構成されています(下図参照)。今回使用する評価ボード、およびコンフィギュレーション ROM の構成に適応させるため、各デザイン・ファイルを編集します。

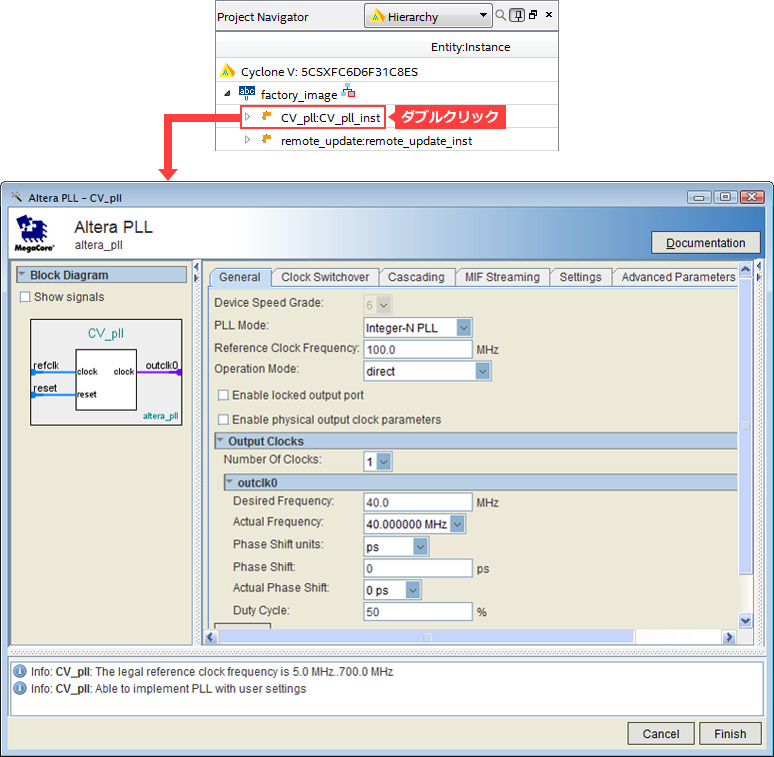

2-1. PLL 回路(CV_pll)のパラメータを変更

Project Navigator ウィンドウにおいて、CV_pll モジュールをダブルクリックし、パラメータ設定のウィンドウを表示します。

評価ボードにおいて、オシレータから FPGA に入力しているクロックの周波数を、Reference Clock Frequency に入力します。今回使用する Beryll ボードの場合、周波数の異なる4つのオシレータが FPGA に接続されていますが、そのうち今回は 33MHz を PLL の入力クロックとして適用させてみます。

PLL の出力クロック周波数は、サンプルに合わせて 40MHz のままにします。

Finish ボタンをクリックし、デザインを更新します。 もしパラメータに変更がない場合でも、使用する Quartus® Prime のバージョンに適用したデザイン・ファイルにするため、Finish ボタンで更新してください。

Generation Successful と表示されたら Exit ボタンでウィンドウを閉じます。

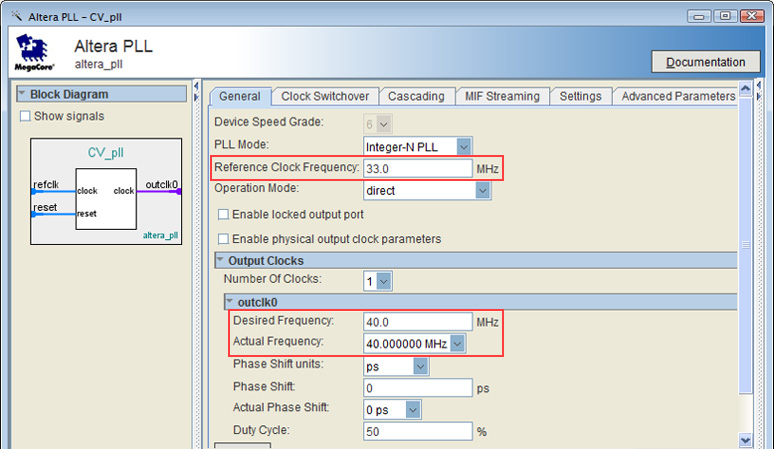

2-2. Altera Remote Update IP(remote_update)のアップデート

サンプル・プロジェクトで使用されている Altera Remote Update IP は、"ALTREMOTE_UPDATE メガファンクション" と言う旧式の IP です。ALTREMOTE_UPDATE のパラメータを更新して使用することもできますが、今回は(今後、新規のプロジェクトで使用することを考慮して)新しい Altera Remote Update IP に更新します。

つまり今回は、作成する Altera Remote Update IP の名前を、既存の ALTREMOTE_UPDATE と同じ名前で生成して上書きすることで対応させます。

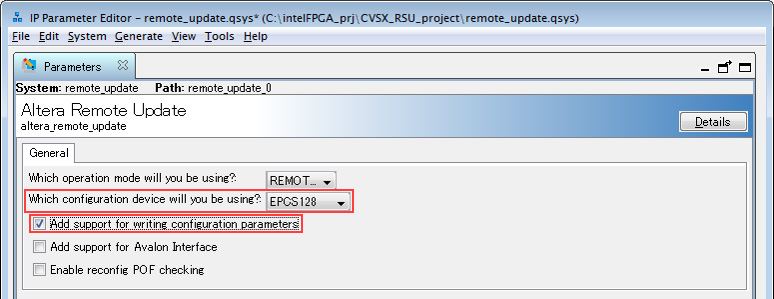

Tools メニュー > IP Catalog から Altera Remote Update を検索し、ダブルクリックします。

New IP Variation ウィンドウにおいて、これから作成する IP の名前および保存するフォルダのパスを指定します。ここでは、既存の remote_update.v と置き換えるため、Entity name は remote_update と入力します。

Which configuration device will you be using? において、評価ボードで使用するコンフィギュレーション ROM を指定します。今回は EPCS128 を選択します。

同時に、Add Support for writing configuration parameters オプションを有効(On)にします。

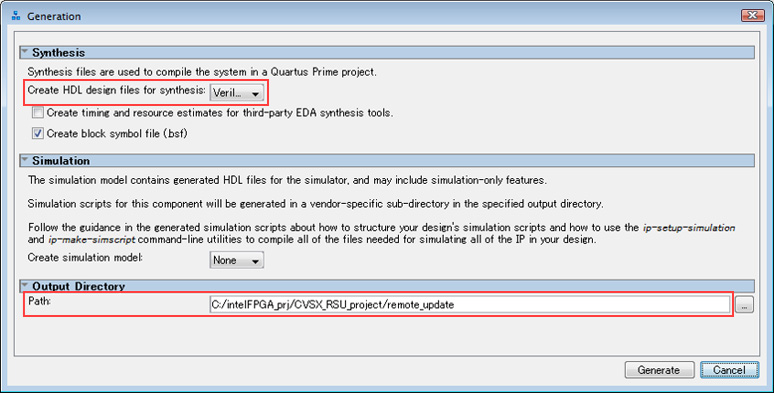

Generate HDL ボタンをクリックし表示された Generate ダイアログボックスにおいて、Synthesis セクションで指定する言語を Verilogにします。(Quartus® Prime は言語混在に対応しているため、VHDL で生成しても問題はありません。)

Output Directory セクションの Path はデフォルトのままにします。

Generate ボタンをクリックし、デザイン・ファイルを生成させます。ファイル生成が完了したら、Finish ボタンをクリックし、ウィンドウを閉じます。

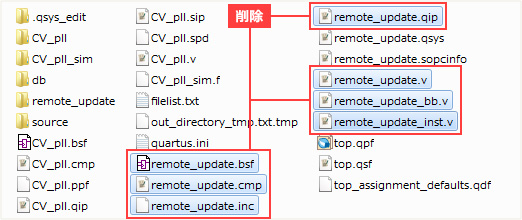

ここで、既存の remote_update ファイルと先ほど作成した remote_update ファイルが競合しないように、作業フォルダと Quartus® Prime の設定を整理します。

エクスプローラで作業フォルダを開き、remote_update の名前が付いたファイルを確認します。(ここでは、作業フォルダ内の remote_update フォルダは対象外です。)

.qsys、 .sopcinfo ファイル以外の remote_update ファイルを削除します。

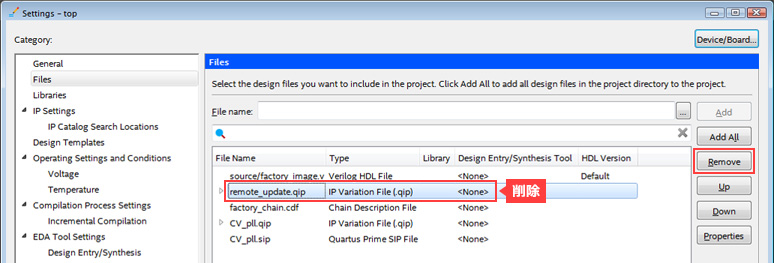

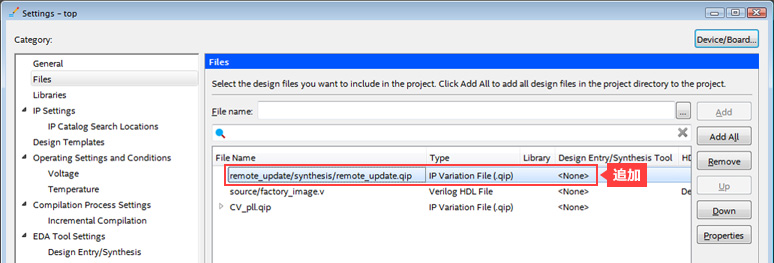

その後、Quartus® Prime の Project メニュー > Add/Remove Files in Project を選択します。

まず、既存の remote_update.qip(remote_update.v)を削除します。

続いて、File name 欄の右側にあるブラウズ・ボタンをクリックし、先ほど新規に生成した remote_update を登録するため、作業フォルダ内 > remote_update フォルダ内 > synthesis フォルダ内にある remote_update.qip を選択します。

Settings ウィンドウを OK ボタンで閉じます。

2-3. Altera Remote Update IP の制御回路を編集

サンプル・デザインを今回の仕様に合わせるため、Page 0に格納する factory_image.v を編集します。

編集ポイントは3つ!

ポイント1. コンフィギュレーション ROM に格納する各イメージの開始アドレスを今回の仕様に合わせて変更する

ポイント2. コンフィギュレーション ROM がサンプルと異なるため、Altera Remote Update IPへ接続するデータのバス幅を修正する

ポイント3. 遷移するコンフィギュレーション・イメージを選択する動作を追加する

以下に、この3つの編集例をあげます。

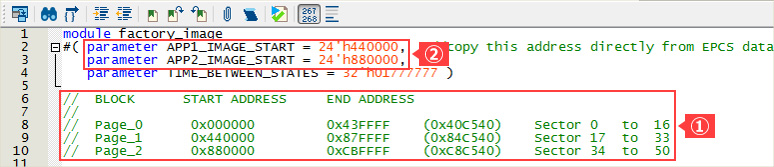

[ポイント1] コンフィギュレーション ROM に格納する各イメージの開始アドレスを今回の仕様に合わせて変更する

Page 0 のイメージから遷移するコンフィギュレーション・データが格納されているコンフィギュレーション ROM の開始アドレスを、Beryll ボード用に変更します。

今回使用する 5CGXFC4C6F27C7 (Cyclone® V) のコンフィギュレーション・データの非圧縮 Raw バイナリ・ファイル(.rbf)サイズは、33,958,560 ビットです。よって factory_image のコンフィギュレーション・データ(非圧縮)は、EPCS128 のセクター0~16(H’000000 ~ H'43FFFF)を使用します。同様に、application1_image、application2_image のコンフィギュレーション・データは、下図①と換算できます。

続いて下図②のように、2行目の parameter 宣言のパラメータ名を application1_image 用として APP1_IMAGE_START にリネームし、3行目に application2_image 用の parameter 宣言として APP2_IMAGE_START を追加します。

さらに、各パラメータ値を、各 Page の開始アドレスに編集します。今回は EPCS128 を使用するので、アドレス幅を32ビットから24ビットへ変更してください。(※ この後、代入先の Altera Remote Update のデータ入力 data_in を24ビットに変更するため。)

[参考資料]

EPCS デバイス

Serial Configuration (EPCS) Devices Datasheet

EPCQ デバイス

Quad-Serial Configuration (EPCQ) Devices Datasheet

EPCQA デバイス

EPCQ-A Serial Configuration Device Datasheet

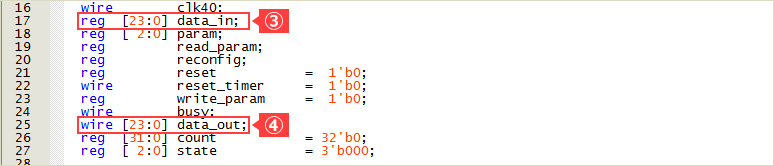

[ポイント2] Altera Remote Update IPへ接続するデータのバス幅を修正する

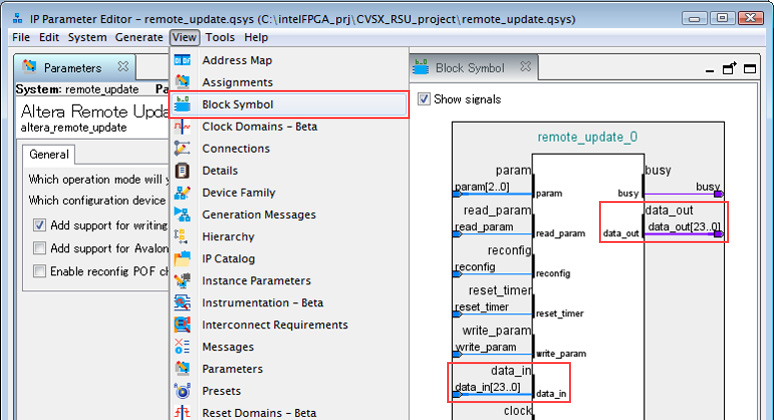

Altera Remote Update IP (remote_update) のデータ入力 data_in、データ出力 data_out は、EPCS128 を使用する場合 3バイト・アドレッシング・モードなので24ビットです。(サンプル・プロジェクトでは EPCQ256 がターゲットのため、4バイト・アドレッシング・モードで32ビットだった。)

下図③、④のように、reg および wire 宣言の data_in および data_out のバス幅を24ビットに変更します。

データのバス幅を簡単に確認する方法は、同ページ内 [ハナコのつぶやき その2] をご覧ください。

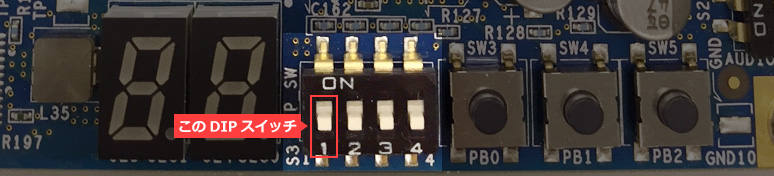

[ポイント3] 遷移するコンフィギュレーション・イメージを選択する動作を追加する

factory_image から application1_image と application2_image どちらへ遷移するかを確定する条件として、今回は Beryll ボード上の DIP スイッチを活用します。

そのため、入力ピンを追加します。(下図⑤参照)

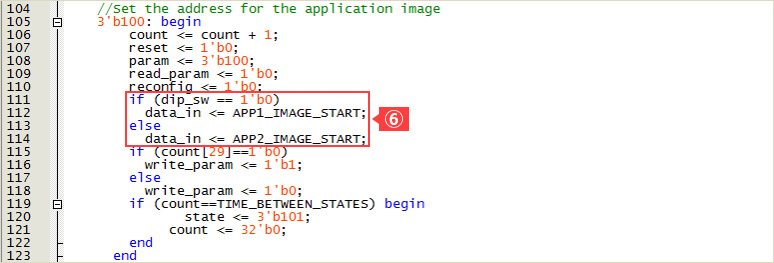

また、遷移するための条件文を追加します。例えばこんな感じ。(下図⑥参照)

(※ dip_sw が 0 のとき、data_in には APP1_IMAGE_START(つまり 24'h440000)が代入され、dip_sw が 1 のとき、data_in には APP2_IMAGE_START(つまり 24'h880000)が代入される。)

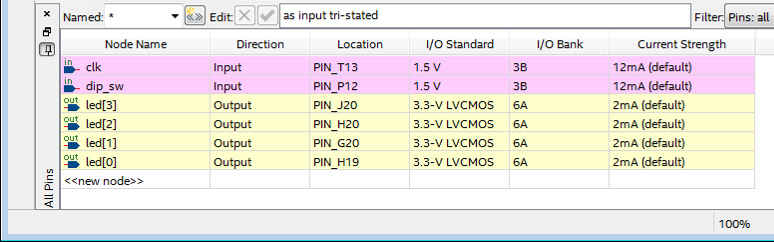

2-4. ピン・レイアウトを変更

評価ボード、および編集したデザインに合わせ、Pin Planner でピン・レイアウトを変更します。同時に、ボードに応じて I/O 規格も変更します。以下は、Beryll ボードを使用した場合の一例です。(今回の編集例の場合は入力ピンが追加されているので、事前に Analysis & Elaboration を実行しておきます。)

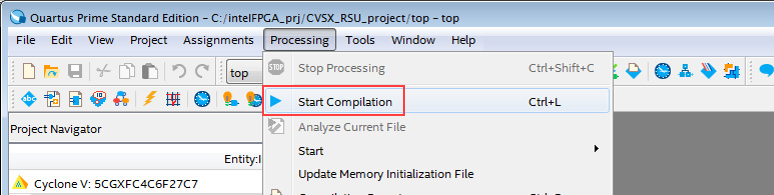

3. コンパイルを実行、sof ファイル名を変更

Processing メニュー > Start Compilation を実行し、factory_image をコンパイルします。

タイミング検証を行い、要求仕様を満たすことを確認します。

その後、生成された top.sof ファイルを factory_image.sof としてリネームします。

Programmer で FPGA に factory_image.sof を書き込み、動作を確認しておきましょう。

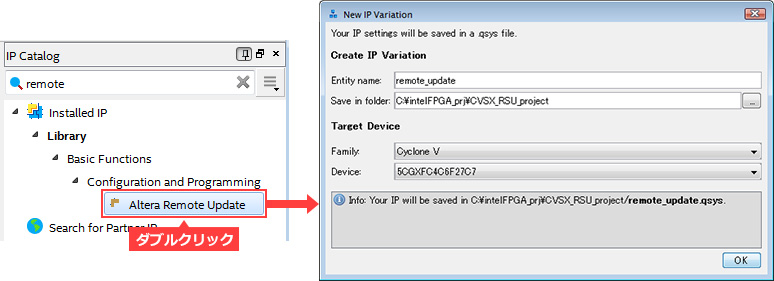

[ハナコのつぶやき その2. Altera Remote Update IP のデータ幅を確認する方法]

Altera Remote Update IP のデータ入力 data_in、データ出力 data_out のビット幅を、先に紹介した参考資料の Datasheet から調べるのはちょっと面倒。そんなとき、簡単に確認する方法をご紹介します。

IP Catalog で Altera Remote Update IP を作成する際に Which configuration device will you be using? で使用するコンフィギュレーション ROM を指定しますが、そのときに View メニュー > Block Symbol を選択するとイメージ図が表示できます。そのdata_in、data_out のバス幅を確認してください。

次は遷移先のデザインを構築

これで、コンフィギュレーション ROM の Page 0 に書き込む コンフィギュレーション・データ 0 が構築できました!

続いて、Page 1、Page 2 に書き込むコンフィギュレーション・データを作成しましょう。(下記 #3 へ続く)

FPGA のコンフィギュレーション・データを切り替える方法 HDL 編 [#3/3]

おすすめ記事/資料はこちら

FPGA のコンフィギュレーション・データを切り替える方法 HDL 編 [#1/3]

FPGA のコンフィギュレーション・データを切り替える方法 HDL 編 [#2/3]

FPGA のコンフィギュレーション・データを切り替える方法 HDL 編 [#3/3]

FPGA / CPLD の一般的な開発フロー