こんにちは。

マクニカでインテル® FPGA 製品の技術サポートをしている インテル・F・ハナコ です。

今回は、EPCQ/EPCQA/EPCS に格納した 複数のコンフィギュレーション・データをFPGAが自動で切り替える制御動作を、HDLデザイン(ステートマシン回路)で作成する方法 についてご紹介します。

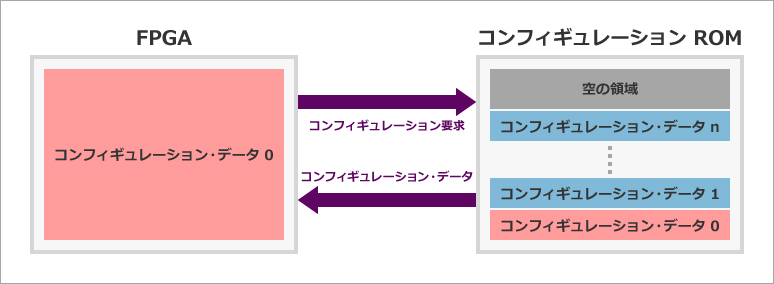

FPGA は、外部からコンフィギュレーション・データを受信することで初めて動作します。

そのコンフィギュレーション・データの授受をボード上で行わせるには、そのデータを格納した ROM の実装が必要です。

採用する FPGA のファミリと使用する ROM によりコンフィギュレーション・スキームは様々ありますが、一番シンプルな方法は、インテル® FPGA 専用のコンフィギュレーション ROM(EPCQ、EPCQA、EPCS)を使用する アクティブ・シリアル(AS: Active Serial)コンフィギュレーションです。

[参考資料]

FPGA の各ファミリがサポートするコンフィギュレーション・スキームの対応表

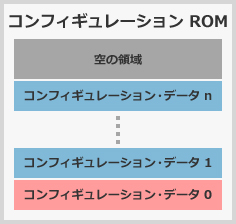

通常 EPCQ、EPCQA、あるいは EPCS には、対向する FPGA 用のコンフィギュレーション・データを1つ格納しますが、複数保存することもできます。このように EPCQ/EPCQA/EPCS の領域を使用することで、以下のメリットがあります。

- EPCQ/EPCQA/EPCS の空き領域を有効活用できる

- ボードごとに別々のコンフィグレーション・イメージを書き込む必要がなくなり工数を削減できる

- ボードの状況に応じて FPGA の動作を切り替えることができる

このような仕様をメーカーでは、通称 ”リモート・システム・アップデート機能” と呼んでいます。

なおこの記事は、Quartus® Prime の基本操作のフローが簡略化されていますので、必要に応じて下記ページの各種ドキュメントをご覧ください。

FPGA / CPLD の一般的な開発フロー

対象デバイス・ファミリ

- FPGA:Cyclone® V、Cyclone® IV、Arria® V、Arria® II、Startix® V、Stratix® IV

- コンフィギュレーション ROM:EPCQ、EPCQA、EPCS

コンフィギュレーション・データの切り替え仕様

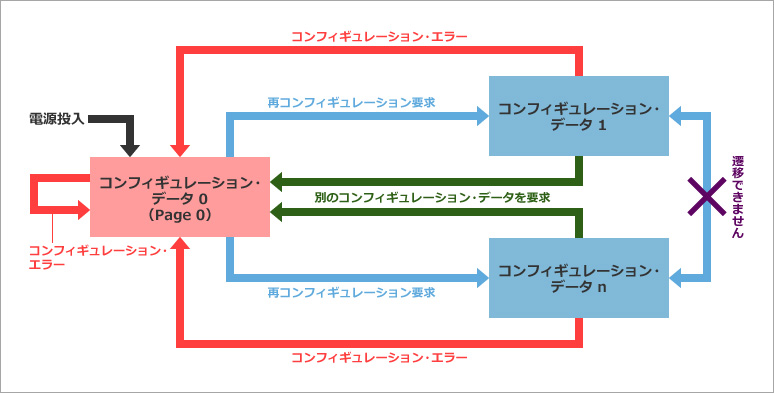

電源を投入後、対象の FPGA はまず EPCQ/EPCQA/EPCS の Page0(開始アドレス位置 0x000000)に格納されたデータをコンフィギュレーションします。その後、必要に応じて別の Page に格納されたデータへアクセスさせ、再びコンフィギュレーションを行います。

このときにコンフィギュレーションが失敗した場合、FPGA は自動的に Page0 のデータをコンフィギュレーションし、復旧します。

なお、対象の FPGA において、Page 0 に格納されたコンフィギュレーション・データ以外のコンフィギュレーション・データ間の遷移はできません。例えば、コンフィギュレーション・データ 1 のアプリケーションからコンフィギュレーション・データ n のアプリケーションへ遷移させる場合は、一度 Page 0 のコンフィギュレーション・データ 0 のアプリケーションに遷移する必要があります。

このように、コンフィギュレーション・データの切り替え動作を FPGA に行わせるには、Altera Remote Update IP を使用します。この IP は、無償で利用できるファンクションで、Quartus Prime Lite Edition でも使用可能です。

[参考資料]

Altera Remote Update IP Core User Guide

今回使用する FPGA および評価ボード

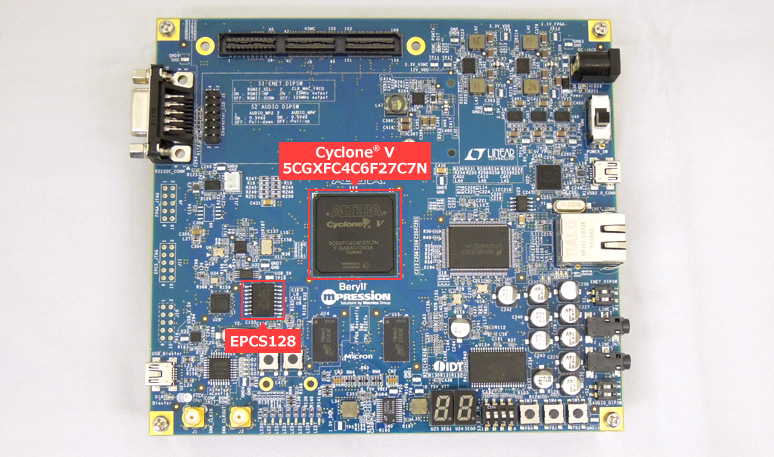

対象の FPGA とコンフィギュレーション ROM が搭載されたボードであれば対応可能です。今回は Cyclone V (5CGXFC4C6F27C7) と EPCS128 が搭載された Mpression 製の Beryll(ベリル)を使用します。

サンプル・デザインをダウンロード

ここから、サンプル・デザインを用いて簡易的に説明します。

サンプル・デザインは、インテル® PSG(プログラマブル・ソリューションズ事業本部)が運営するDesign Store で入手できます。

[サンプル・デザインの入手方法]

FPGA のサンプル・デザインを無料で手に入れよう

[ダウンロードするサンプル・デザイン]

Remote System Upgrade (RSU) Design Example(for Cyclone V SoC Development Kit)

※ このサンプル・デザインは Cyclone® V SoC 向けに作成されています。デザインに含まれている 各 IP (AlteraPLL、Altera Remote Update)のパラメータも Cyclone® V 向けに構成されているため、このプロジェクトを別のファミリで使用する場合には、IP を新規で作成し直すことを推奨します。

[ハナコのつぶやき その1. プロジェクトをデフォルトのまま利用したいユーザーは]

今回はこのサンプル・デザインに少々手を加え、サンプル・デザインのターゲット・デバイス以外の FPGA およびコンフィギュレーション ROM でも採用できるように解説をしています。

サンプル・デザイン(Cyclone® V SoC Development Kit 対応)のままご利用になる場合には、Design Store 上のサンプル・デザインのページで入手できるドキュメント 「Remote System Upgrade Design Example User Guide」 をご覧ください。

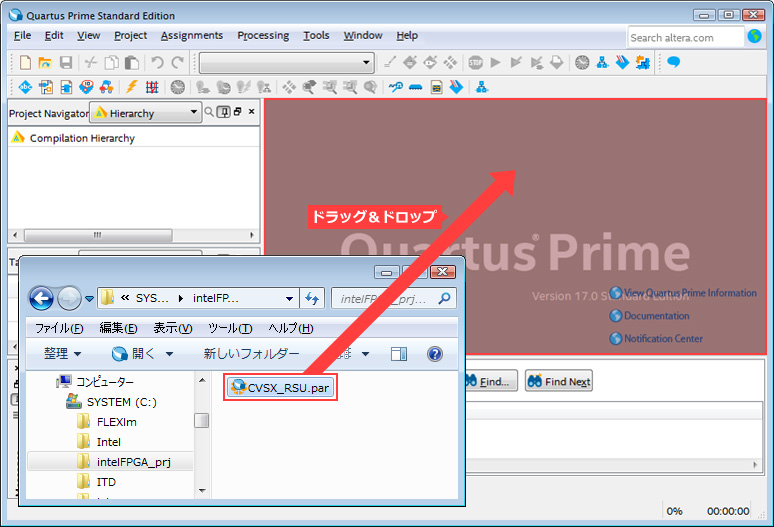

Quartus® Prime にサンプル・デザインのプロジェクトをセット

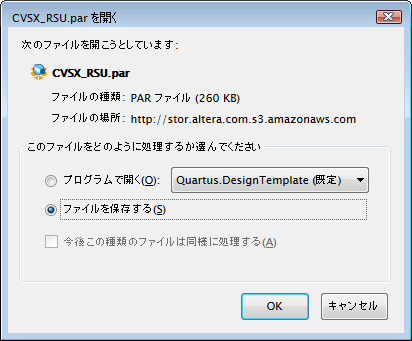

Design Store からダウンロードした par ファイルを展開します。展開方法は、下記 TIPS を参考にしてください。

FPGA のサンプル・デザイン .par ファイルの展開方法

(後半で紹介されていハナコ流の展開方法だと簡単です。)

サンプル・デザインの概要

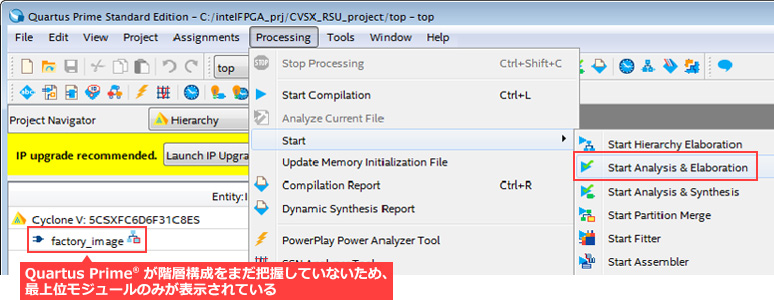

サンプル・デザインの概要を確認するため、Analysis & Elaboration を実行します。

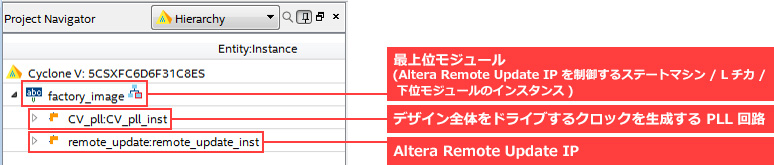

その後 Project Navigator を見ると、factory_image モジュールの下位に、CV_pll と remote_update が存在していることがわかります。各モジュールの概要は、下記のとおりです。

また、プロジェクトの作業フォルダ内にある source フォルダには、現在最上位階層モジュールとしてセットされているfactory_image.v と、もう一つのコンフィギュレーション・データの最上位階層モジュールである application_image.v が保存されています。

各ソースを見ると、factory_image のデータをコンフィギュレーション ROM の Page 0 に格納し、application_image のデータを Page 1 に格納して、切り替える構成になっていることがわかります。

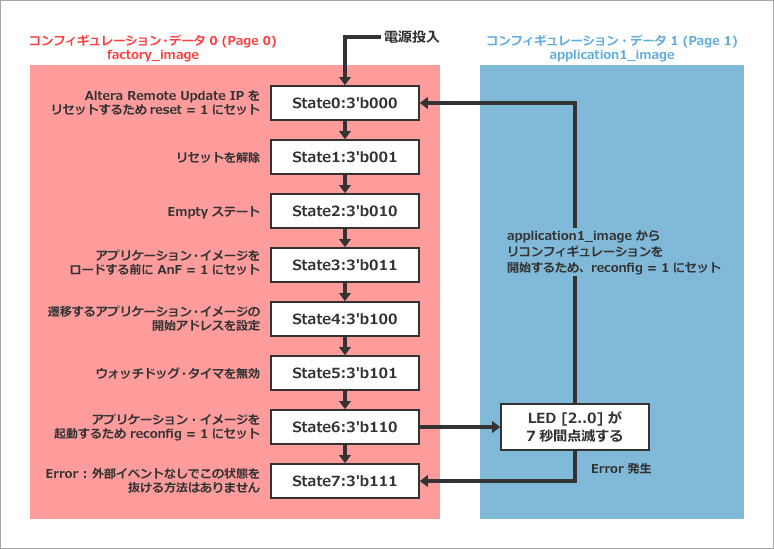

サンプル・デザインの動作仕様を下図に示します。

詳細は、Design Store 上のサンプル・デザインのページで入手できるドキュメント 「Remote System Upgrade Design Example User Guide」 で確認してください。

factory_image.v は Altera Remote Update IP (remote_update) を制御して application_image.v へ移行するためのステートマシンが構成されています。その際のフローは上図 State 0 ~ State 6 の7ステップで、State 7 にエラーを示すステートを用意しています。

State 0(Altera Remote Update IP をリセットするため reset = 1 にセット)

→ State 1(リセットを解除)

→ State 2(Empty ステート)

→ State 3(アプリケーション・イメージをロードする前に AnF = 1 にセット)

→ State 4(遷移するアプリケーション・イメージの開始アドレスを設定)

→ State 5(ウォッチドッグ・タイマを無効)

→ State 6(アプリケーション・イメージを起動するため reconfig= 1 にセット)

State 3 の AnF は Application not Factory の略で、アプリケーション・イメージに対してリコンフィギュレーション・トリガをする前に AnF ビットを 1'b1 に設定する必要があります。その後、アプリケーション・イメージのデータが格納されているメモリの開始アドレスを指定します。

AnF ビットを設定するには、ユーザー・ロジックが param = 3'b101、data_in = 24'h000001 および write_param = 1'b1をAltera Remote Update IP へ発行するようにします。

application_image.v は、LED[2:0] を7秒間同時に点滅し続け、Page 0 のコンフィギュレーション・イメージへジャンプする構成になっています。

各デザインにおける LED の表示状況は下図のとおりです。

|

各デザインの LED 点灯デザイン |

||||||

|

State # (LED [2..0]) |

Functions |

LED 3 |

LED 2 |

LED 1 |

LED 0 |

Image Status |

| State 0 (3’b000) |

reset =1, reset RSU IP |

|

|

|

|

factory_Image |

| State 1 (3’b001) |

release reset |

|

|

|

|

|

| State 2 (3’b010) |

empty state |

|

|

|

|

|

| State 3 (3’b011) |

AnF=1 |

|

|

|

|

|

| State 4 (3’b100) |

Set application_image start address |

|

|

|

|

|

| State 5 (3’b101) |

disable watchdog |

|

|

|

|

|

| State 6 (3’b110) |

reconfig=1, boot application Image |

|

|

|

|

application_image |

|

LED[2…0] blink for 7 seconds |

|

|

|

|

||

| State 7 (default) |

Hold |

|

|

|

|

Error |

![]() LED点滅 /

LED点滅 / ![]() LED点灯 /

LED点灯 / ![]() LED消灯

LED消灯

サンプル・プロジェクトの切り替え仕様を変更

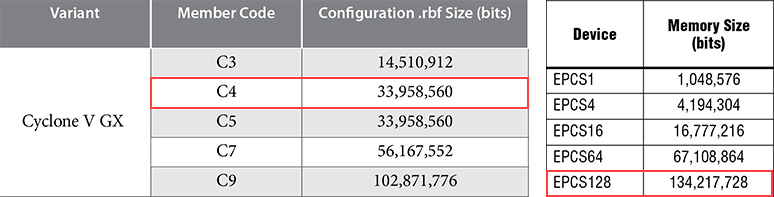

サンプルでは、5CSXFC6D6ES(Cyclone® V)のコンフィギュレーション・データを EPCQ256 に2イメージ格納しています。

今回の評価ボード Beryll は、5CGXFC4C6F27C7 と EPCS128 が搭載されています。5CGXFC4C6F27C7 のコンフィギュレーション・データの非圧縮 Raw バイナリ・ファイル(.rbf)サイズは、33,958,560 ビットです。一方、EPCS128 の容量は、134,217,728 ビットです。

[参考資料]

Cyclone® V Device Datasheet (Configuration Specifications > Configuration Files を参照)

Serial Configuration (EPCS) Devices Datasheet

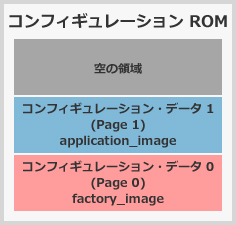

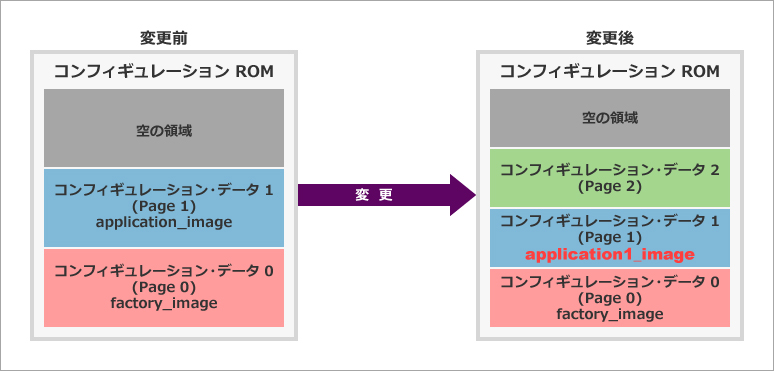

つまり、非圧縮のコンフィギュレーション・データならば3つ格納できる計算です。今回は、サンプル・プロジェクトにおけるコンフィギュレーション ROM の構成を下図のように変更します。

この構成に適用させるため、既存の application_image.v のファイル名を application1_image.v へ変更し、モジュール名を application_image から application1_image へ編集しておきます。

さらに、Project メニュー > Add/Remove Files in Project において、source/application1_image.v ファイルを追加し、source/application_image.v ファイルを削除してください。

また、新規で追加するコンフィギュレーション・データ2のデザインは、後にオリジナルで自作します。

これからの作業の流れ

以下の6ステップで作業を行います。

ステップ1:Page 0 用デザインを作成

ステップ2:Page 1 用デザインを作成

ステップ3:Page 2 用デザインを作成

ステップ4:コンフィギュレーション ROM 用のプログラミング・ファイルを作成

ステップ5:コンフィギュレーション ROM にプログラミングを実行

ステップ6:実機で動作を確認

ではまず、ステップ1です。

Page 0 に書き込むためのデザインを作成し、コンパイル、実機検証、sof ファイルのリネームを行います。(下記 #2 へ続く)

FPGA のコンフィギュレーション・データを切り替える方法 HDL 編 [#2/3]

おすすめ記事/資料はこちら

FPGA のコンフィギュレーション・データを切り替える方法 HDL 編 [#1/3]

FPGA のコンフィギュレーション・データを切り替える方法 HDL 編 [#2/3]

FPGA のコンフィギュレーション・データを切り替える方法 HDL 編 [#3/3]

FPGA / CPLD の一般的な開発フロー