こんにちは。

マクニカで Altera® FPGA の技術サポートをしている アルテラ ハナコ です。

このページでは、Altera® FPGA に Nios® V を入れて L チカさせる方法 をご紹介しています。

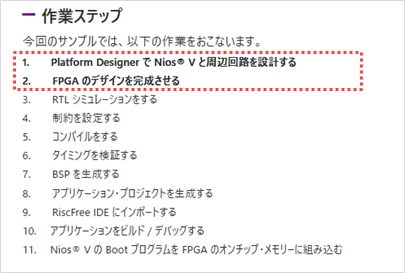

これまで、下記 作業ステップのうち 操作 1 ~ 6 までを実施してきました。(詳細は Part 1: ハードウェア開発 をご覧ください。)

今回 Part 2: ソフトウェア開発 では、操作 7 ~ 11 をご紹介します。

Nios® V の開発フロー (再掲)

作業ステップ (再掲)

1. Platform Designer で Nios® V と周辺回路を設計する

2. FPGA のデザインを完成させる

3. RTL シミュレーションをする

4. 制約を設定する

5. コンパイルをする

6. タイミングを検証する

<※ 今回は 以降の作業からご覧ください。>

7. BSP を生成する

11. Nios® V の Boot プログラムを FPGA のオンチップ・メモリーに組み込む

<Notes> Quartus® Prime の細かな操作は、Altera® FPGA の開発フロー をご覧ください。

なお 操作7、操作8 および 操作10 (ビルドのみ) は、Part 1: ハードウェア開発 "3. RTL シミュレーションをする" 内で一部実施済みですが

ここでは、ハードウェア開発とソフトウェア開発が別の設計者である可能性を考慮し、操作フローを紹介します。

Part 1 のフローに沿い実施済みの人は、Part 2 の各作業内容を確認した上で "スキップ or 実施" を自身で判断してください。

![]() また ページ後半では、Nios® V の Boot プログラムを変更した場合に便利な "時短アップデート方法" もご案内しています。必見ですよ!

また ページ後半では、Nios® V の Boot プログラムを変更した場合に便利な "時短アップデート方法" もご案内しています。必見ですよ!

7. BSP を生成する

事前に Quartus® Prime プロジェクトフォルダー内に、ソフトウエア開発用のワークスペース (フォルダー) を手動で作成します。

このサンプルでは、software フォルダーを作成します。

さらに、software フォルダー内に、アプリケーション・プロジェクト用フォルダー (app) と BSP 用フォルダー (hal_bsp) をそれぞれ作成します。

BSP (Board Support Package) を生成するため、Windows の スタート ➤ Altera <version.build_number> <Standard or Lite> Edition フォルダーを開き、Nios V Command Shell (Quartus Prime <version>) をクリックして、Nios V command shell を起動します。

Nios V command shell に下記コマンドを入力し、Quartus® Prime のプロジェクトフォルダーをカレントディレクトリーに指定します。

cd C:\AlteraFPGA_prj\niosv_sample

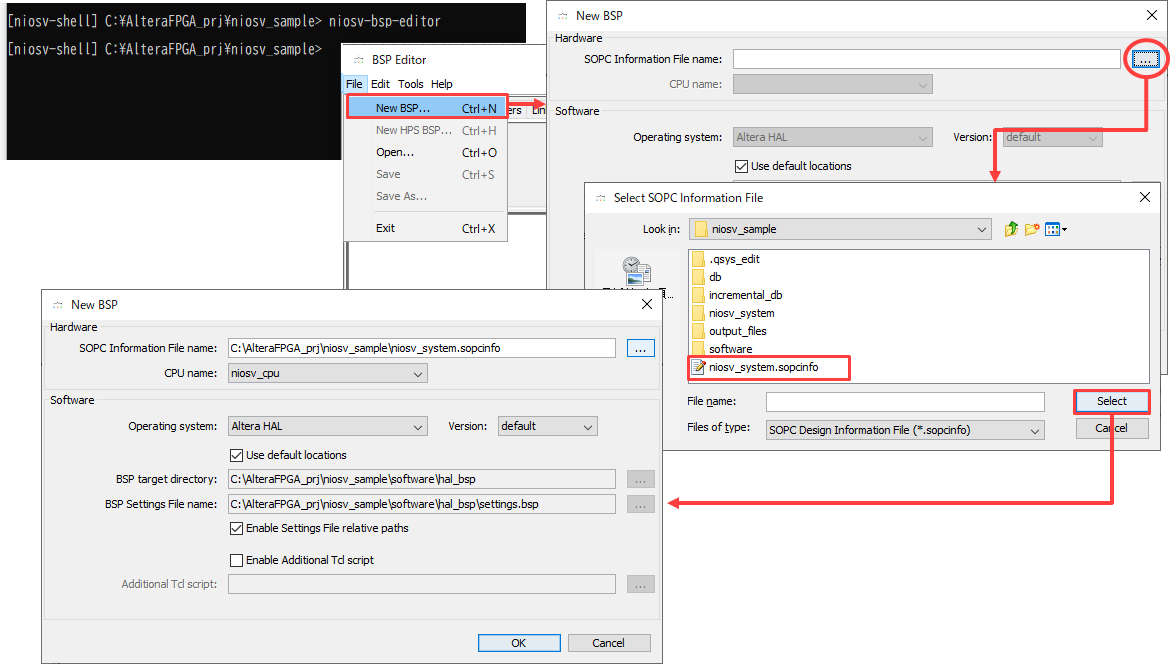

Nios V command shell に下記コマンドを入力し、BSP Editor を起動します。

niosv-bsp-editor

BSP Editor の File メニュー ➤ New BSP… を選択後、SOPC Infomation File Name 欄横のボタンを押下し、使用するハードウェア情報 (.sopcinfo ファイル) を BSP Editor に指定します。その後 New BSP ウィンドウの [OK] ボタンをクリックします。

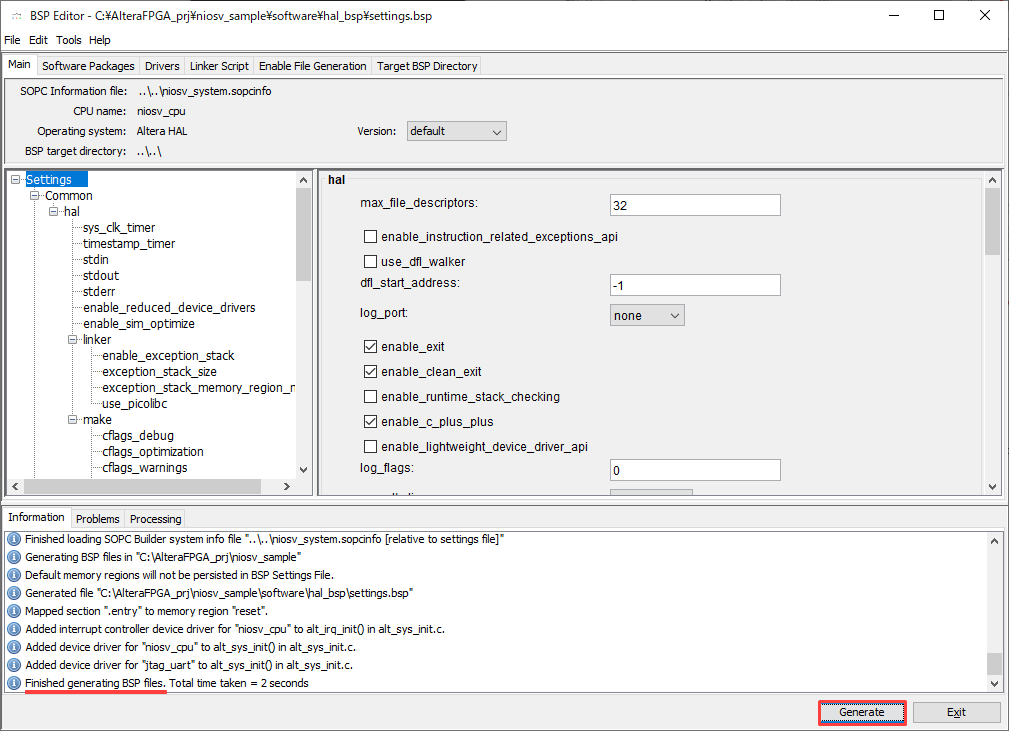

BSP Editor の GUI が表示されます。今回のサンプルでは編集はおこなわず、GUI 右下の [Generate] をクリックします。

Information タブに Finished generating BSP files. が表示されたのを確認後 [Exit] します。

8. アプリケーション・プロジェクトを生成する

あらかじめ作成しておいた Nios® V の Boot プログラム (C ソースファイル) を 先ほど作成した software/app フォルダーへ移動します。

このサンプルでは、ファイル名を presspb_led_niosv.c として保存します。

次に Nios V Command Shell へ 次のコマンドを入力します。

# アプリケーション・プロジェクト・ファイルの生成

niosv-app --bsp-dir=software/hal_bsp --app-dir=software/app --srcs=software/app/presspb_led_niosv.c --elf-name=presspb_led_niosv.elf

# アプリケーション・プロジェクトの構築

cmake -G "Unix Makefiles" -DCMAKE_BUILD_TYPE=Debug -B software/app/build/Debug -S software/app

Nios V command shell に下記コマンドを入力し、シェルウィンドウを閉じます。

exit

9. RiscFree IDE にインポートする

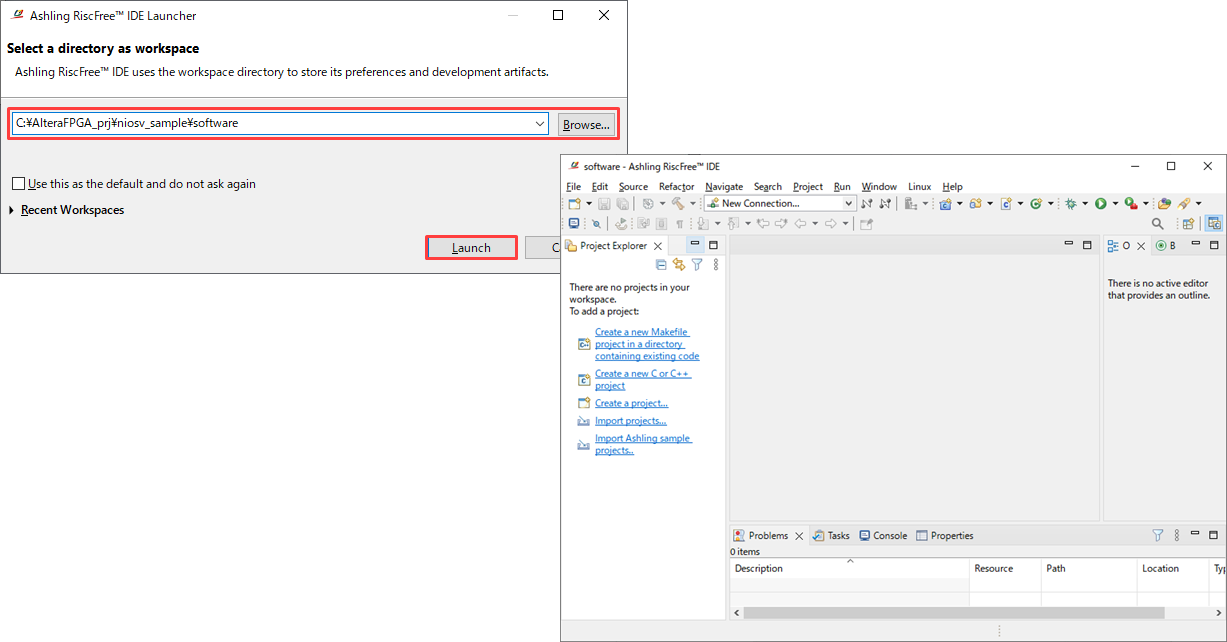

Windows の スタート ➤ Altera <version.build_number> <Standard or Lite> Edition フォルダーを開き、Ashling RiscFree IDE for Altera (Quartus Prime <version>) をクリックして、RiscFree IDE を起動します。

[Browse] ボタンでソフトウェア開発用のワークスペース software フォルダー を指定し、[Launch] ボタンをクリックします。

RiscFree IDE の GUI が起動します。

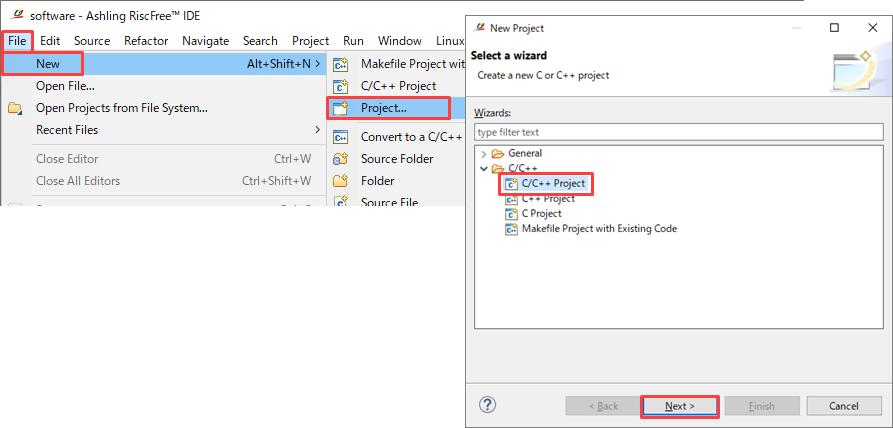

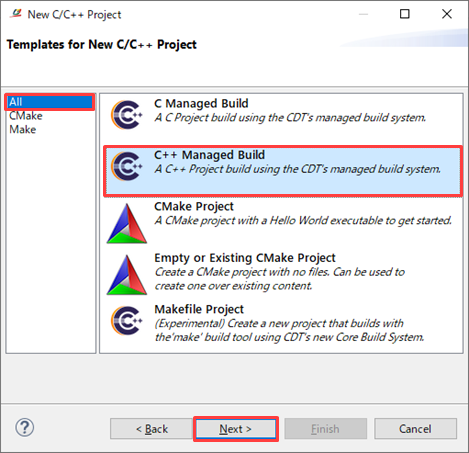

RiscFree IDE の File メニュー ➤ New ➤ Project を選択し、表示されたウィンドウから C/C++ Project (C/C++ フォルダー内) を選択後に [Next] ボタンをクリックします。

表示された New C/C++ Project ウィンドウの左枠から All を選択し、右枠から C++ Managed Build を選択後、[Next] ボタンをクリックします。

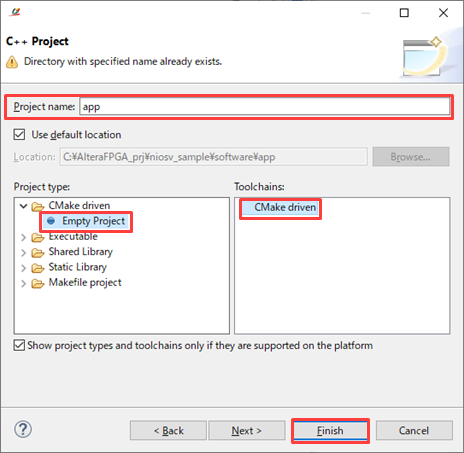

表示された C++ Project ウィンドウにおいて 次の項目を設定します。

Project name: app

Project type: CMake driven > Empty Project

Toolchains: CMake driven

10. アプリケーションをビルド / デバッグする

10-1. アプリケーションをビルド

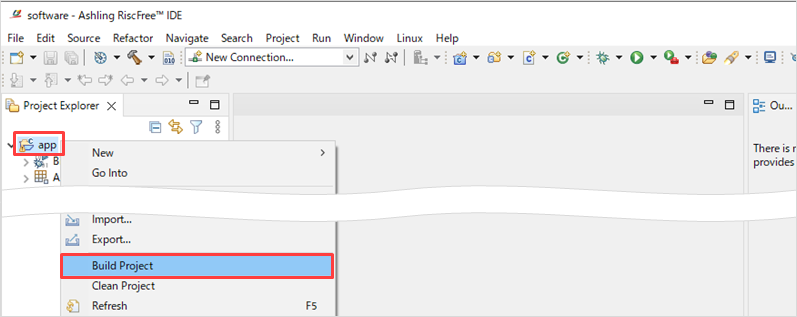

アプリケーション・プロジェクトをインポート後、app プロジェクトを右クリック選択し、Build Project を実行します。

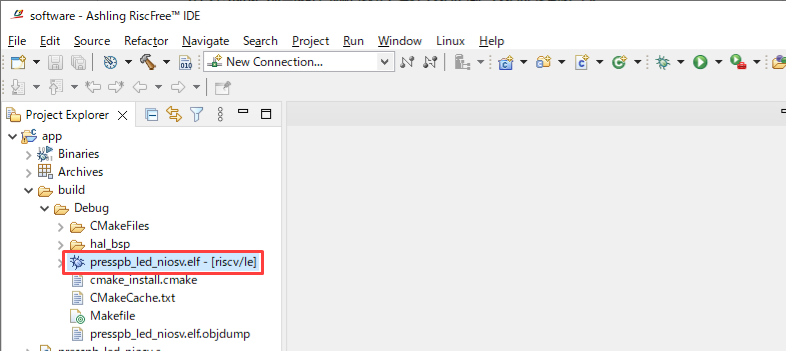

C ソースコードのビルドが完了し、実行ファイル .elf が生成されます。

10-2. アプリケーションをデバッグ

Build Project により生成された elf ファイルを評価ボード上の FPGA で実行し、動作を確認します。

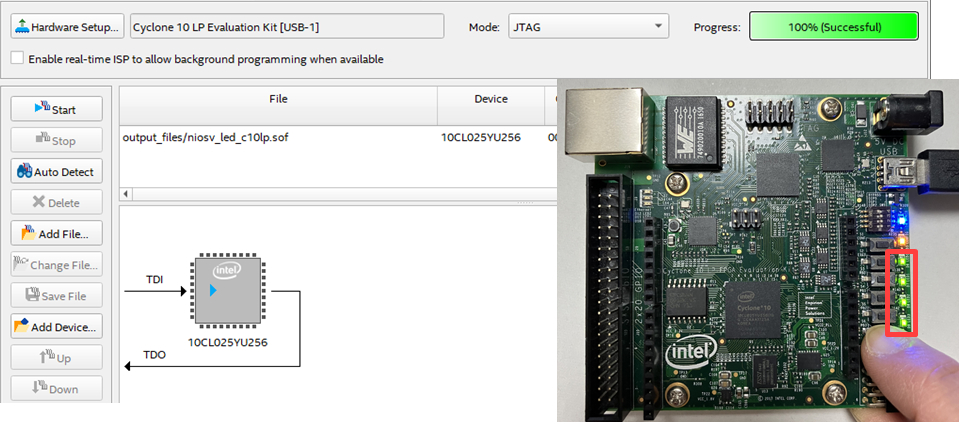

10-2-1. FPGA のコンフィグレーション

FPGA に ハードウェア用のプログラム sof ファイルをダウンロードします。

<Notes>

Cyclone® 10 LP 評価キット利用者は、事前に DIP スイッチ SW1 のうち SW1.4 を On にセットしてください。

また、このボードは USB-Blaster II 用のデバイスドライバーをインストールしてご利用ください。

[参考情報] USB-Blaster II ドライバーのインストール

Cyclone® 10 LP Evaluation Kit に付属しているケーブルにおいて、mini USB (Type-B) を評価ボードに接続し、次に USB ケーブル のうち黒いコネクターをパソコンへ接続します。ボードに電源が供給されます。

Quartus® Prime の下記メニューから Programmer を起動します。

Tools メニュー ➤ Programmer

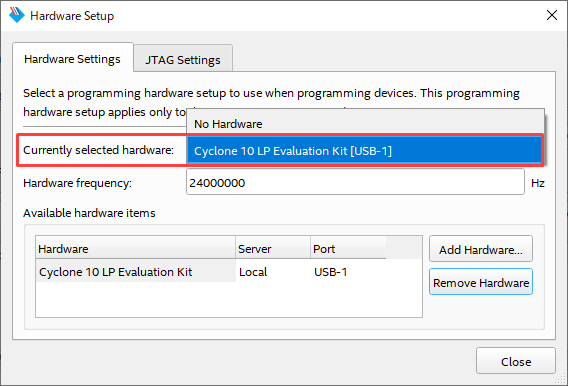

Programmer ウィンドウの Hardware Setup ボタンをクリックし、Cyclone 10 LP Evaluation Kit を選択します。

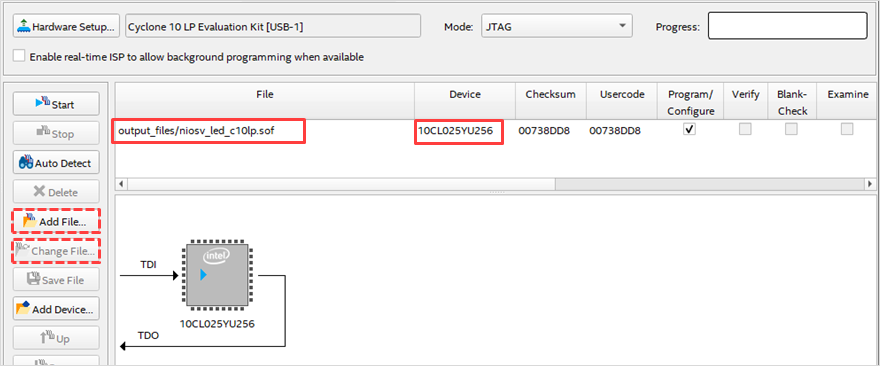

Programmer ウィンドウの Mode プルダウン・リストより、 JTAG を選択します。

File 欄には Quartus Prime のコンパイルで生成した の niosv_led_c10lp.sof ファイルがすでに登録され 、Device 欄には プロジェクトで指定した FPGA の型番 (今回のサンプルは 10CL025YU256) が表示されています 。

<Notes>

もし sof ファイルが未登録の場合は、 Add File ボタンをクリックし、 //Quartus® Prime プロジェクトフォルダー/output_files/niosv_led_c10lp.sof を選択後、Open ボタンをクリックして File 欄に登録してください。あるいは、別の sof ファイルが登録されている場合には、そのファイルを選択後に Change File ボタンをクリックして //Quartus® Prime プロジェクトフォルダー/output_files/niosv_led_c10lp.sof を指定し直してください。

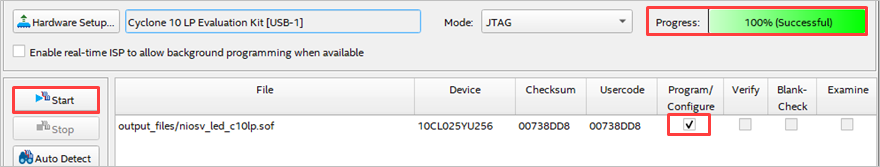

Programmer ウィンドウ内 niosv_led_c10lp.sof 行の右側にある Program/Configure オプションにチェックを入れ、[Start] ボタンをクリックして

ハードウェア用プログラムをダウンロードします。

Progress バーが 100% になり、Quartus® Prime の Messages ウィンドウ (System タブ) に Info: Successfully performed operation(s) のメッセージを

確認できたら、ダウンロードは完了です。

10-2-2. Juart-terminal 登録

RiscFree IDE は、UART のターミナルである JTAG コンソールをもっていないため、外部の Tool を登録して JTAG コンソールを使用します。

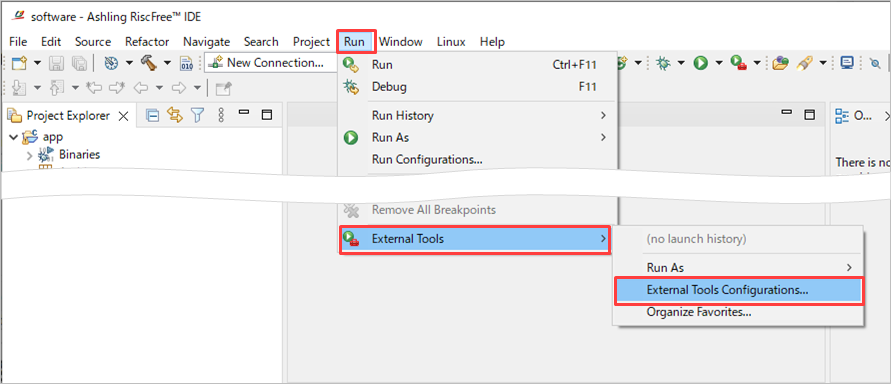

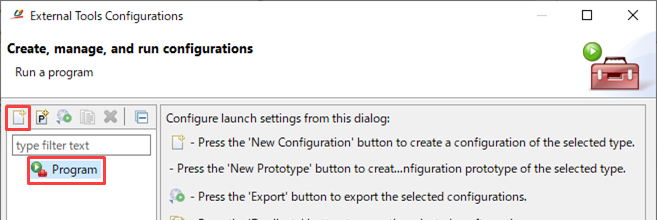

以下のメニューから External Tools Configurations を起動します。

Run メニュー ➤ External Tools Configurations...

External Tools Configurations 画面左側の Program をハイライト選択し、左上の New launch confiurations アイコンをクリックします。

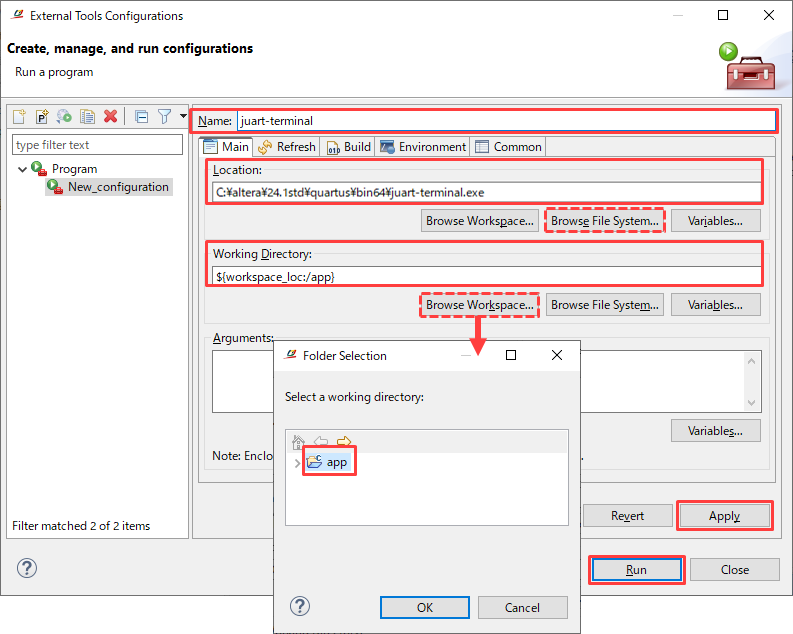

表示された GUI において、juart-terminal を登録します。

Name: juart-terminal

Location: juart-terminal.exe の絶対パス ([Browse File System...] ボタンを活用)

例) C:\altera\24.1std\quartus\bin64\juart-terminal.exe

Working Directory: [Browse Workspace...] ボタンをクリックし、Folder Selection ウィンドウで app を選択

External Tools Configurations の右下にある [Apply] ボタンにより情報を登録し、[Run] ボタンをクリックして実行します。

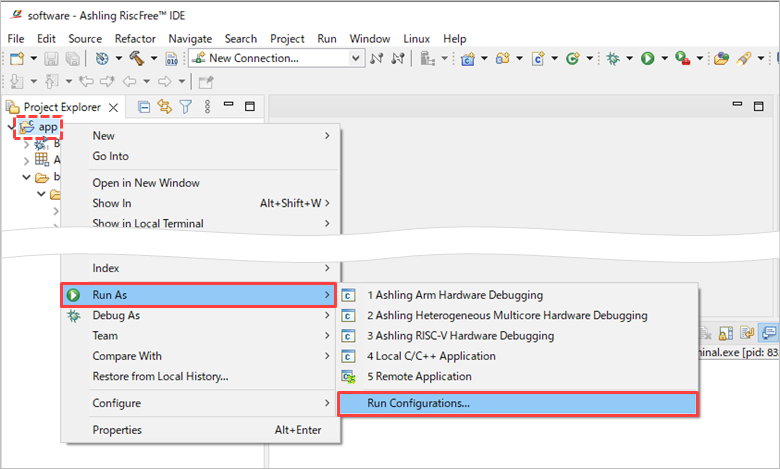

10-2-3. Run Configuration 起動

Cyclone® 10 LP Evaluation Kit 上の FPGA にソフトウェア用プログラムの elf ファイルをダウンロードするため、app プロジェクトを右クリックし以下のメニューを選択します。

Run As ➤ Run configurations...

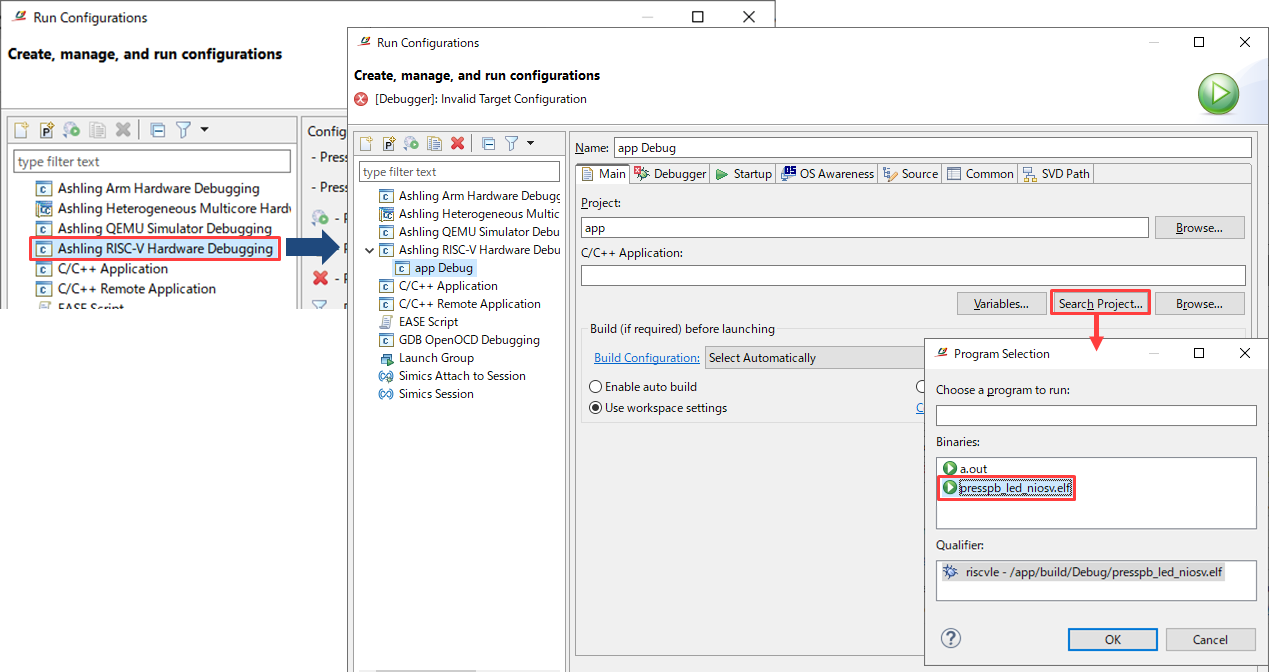

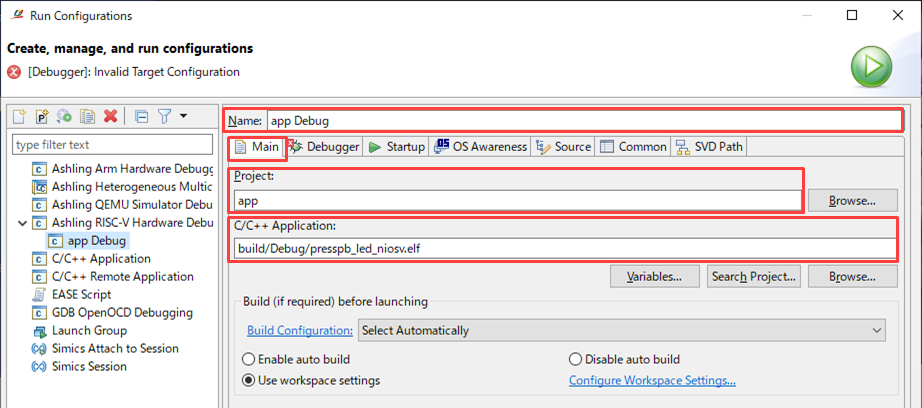

Run configurations ウィンドウにおいて、Ashling RISC-V Hardware Debugging をダブルクリックします。

Main タブ内の [Search Project...] ボタンをクリックし、Program Selection ウィンドウから presspb_led_niosv.elf を選択して [OK] ボタンをクリックします。

Main タブにおいて、次の内容が反映されていることを確認します。

Name: 任意名を入力 (今回のサンプルでは app Debug)

Project: app

C/C++ Application: build/Debug/presspb_led_niosv.elf

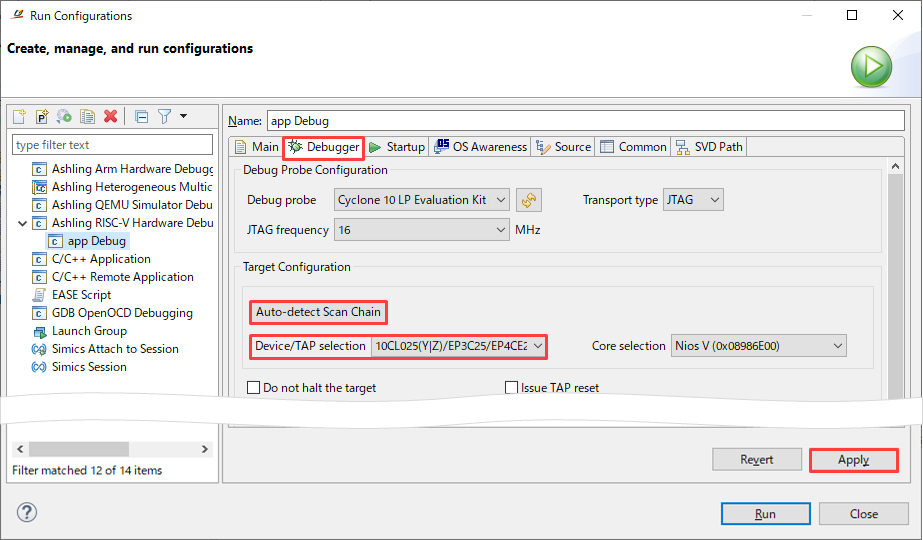

Debugger タブに切り替え、[Auto-detect Scan Chain] ボタンをクリックし、Device/Tap selection 欄に 10CL025(Y|Z) が検出されたことを確認できたら、右下にある [Apply] ボタンをクリックします。

10-2-4. Run As 実行

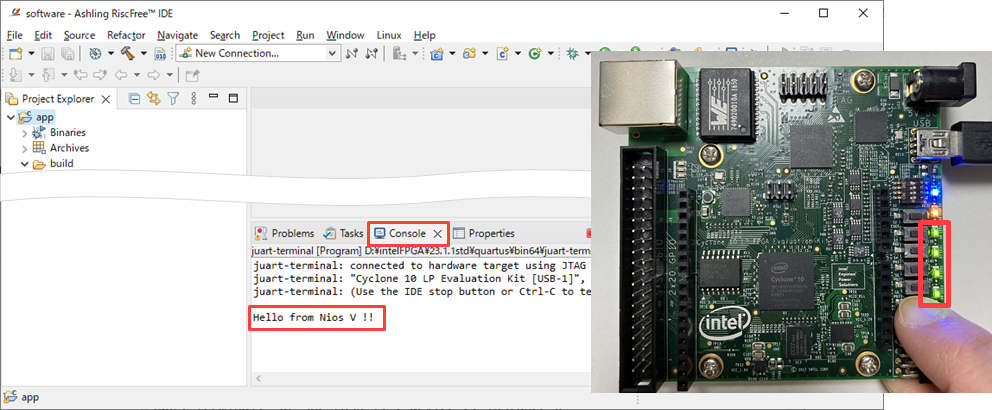

Run Configuration ウィンドウの右下にある [Run] ボタンをクリックします。

プログラムが実行されると、RiscFree IDE の Console に alt_printf 関数で指定した "Hello from Nios V !!" が表示されます。

また、評価ボード上のプッシュボタン [PB3] を押下すると4つの LED は点灯し、[PB3] を離すと LED はすべて消灯することが確認できます。

動作確認を終えたら、RiscFree IDE の Console にある ■ ボタンをクリックし、プログラムを終了します。

RiscFreeIDE の File メニュー ➤ Exit を選択し、RiscFree IDE の作業を終了します。

11. Nios® V の Boot プログラムを FPGA のオンチップ・メモリーに組み込む

ソフトウェア・プログラムが期待どおりに動作したので、この Boot プログラムを FPGA のオンチップ・メモリーに組み込んでみましょう。

11-1.Nios® V の Boot プログラムを hex ファイルに変換

Windows の スタート ➤ Altera <version.build_number> <Standard or Lite> Edition フォルダーを開き、Nios V Command Shell (Quartus Prime <version>) をクリックし、再び Nios V command shell を起動します。

Nios V command shell に下記コマンドを入力し、Quartus® Prime のプロジェクトフォルダーをカレントディレクトリーに指定します。

cd C:\AlteraFPGA_prj\niosv_sample

次に 下記コマンドを入力し、elf ファイルを hex ファイルに変換します。

elf2hex app/build/<user_applicatio>.elf -o <hex_output_file>.hex -w <On-Chip RAM のデータ幅> -b <On-Chip RAM の ベースアドレス> -e <On-Chip RAM の エンドアドレス>

例)

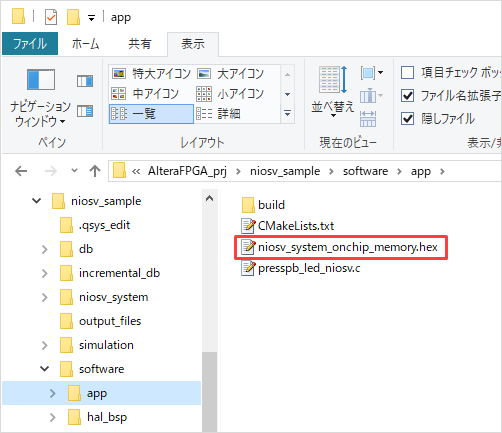

elf2hex software/app/build/Debug/presspb_led_niosv.elf -o software/app/niosv_system_onchip_memory.hex -w 32 -b 0x00010000 -e 0x00019FFF

<Notes>

Platform Designer で作成した On-chip Memory の初期値設定がデフォルト (Initialize

memory content = On) の場合は、hex ファイル名は niosv_system_onchip_memory.hex にしてください。

もし、Enable non-default initialization file = On でデフォルト以外のファイルを指定している場合は、

elf2hex コマンドの -o を 目的のファイル名およびパス先で指定してください。

例) elf2hex software/app/build/Debug/presspb_led_niosv.elf -o ocram_init/niosv_boot.hex -w 32 -b 0x00010000 -e 0x00019FFF

11-2. meminit.qip を作成し、Quartus® Prime のプロジェクトに登録しコンパイル

<Notes>

Platform Designer で作成した On-chip Memory の初期値設定が デフォルトではないファイルを指定している (つまり Enable non-default initialization file = On) 場合は、meminit.qip の作成は不要です。そのため、作業①~③ はスキップしてください。

![]()

① 先ほど作成した Nios® V 用 Boot プログラムの hex ファイルを FPGA 内蔵メモリー (Nios® V システムの On-Chip Memory) の初期値として反映させるため、

下記制約をテキストファイルに記入します。

set_global_assignment -name SEARCH_PATH $::quartus(qip_path)

② ファイル名を meminit.qip とし、Nios® V 用 Boot プログラムの hex ファイルと同フォルダーに保存します。

③ Quartus® Prime の下記メニューにより、プロジェクトに meminit.qip を

追加登録します。

Project メニュー ➤ Add/Remove Files in Project

④ Quartus® Prime でコンパイルを実行します。

Processing メニュー ➤ Start Compilation

コンパイルが完了すると、Nios® V の Boot プログラムを含んだ .sof が生成されます。

11-3.FPGA に書き込み、実機検証

Quartus® Prime の Programmer を起動して .sof を書き込みます。

評価ボード上のプッシュボタン [PB3] を押下すると4つの LED は点灯し、[PB3] を離すと LED はすべて消灯することが確認できます。

これで、sof ファイルに Nios® V の Boot プログラムが組み込まれました!

FPGA のコンフィグレーション用 ROM 向けにプログラミングファイルが必要な場合は、Quartus® Prime の Convert Programming Files で この sof ファイルをもとにファイルを生成してご利用ください。

以上で、 Nios® V の L チカ作業は終了です。

Nios® V Boot プログラム 時短アップデート方法

FPGA のハードウェア側のデザインには変更がなく Nios® V の Boot プログラム (つまり On-Chip Memory の初期値データ) のみを更新させる場合、Quartus® Prime の再コンパイル実行が必要です。しかし、フルコンパイルせずに On-Chip Memory の初期値データだけをアップデートさせる方法があるんです!

なお、この時短方法は 以下 3点 の条件を満たしていることが前提です。

・ Platform Designer で作成した On-chip Memory の初期値を、Memory Initialization パラメーターで設定していること

・ Project メニュー ➤ Add/Remove Files in Project において meminit.qip が登録してあること (※ Initializememory content = On の場合のみ)

・ Quartus® Prime でフルコンパイルを実行していること

① Nios® V の Boot プログラム内容を変更します。

② Windows の スタート ➤ Altera <version.build_number> <Standard or Lite> Edition フォルダーを開き、

Nios V Command Shell (Quartus Prime <version>) をクリックし、Nios V command shell を起動します。

③ 下記コマンドを入力し、Quartus® Prime のプロジェクトフォルダーをカレントディレクトリーに指定します。

cd C:\AlteraFPGA_prj\niosv_sample

④ 下記コマンドを入力し、C ソースコードのビルドを実行し .elf を生成します。

make -C software/app/build/Debug

⑤ 下記コマンドを入力し、elf ファイルを hex ファイルに変換します。

elf2hex app/build/<user_applicatio>.elf -o <hex_output_file>.hex -w <On-Chip RAM のデータ幅> -b <On-Chip RAM の ベースアドレス> -e <On-Chip RAM の エンドアドレス>

例) elf2hex software/app/build/Debug/presspb_led_niosv.elf -o software/app/niosv_system_onchip_memory.hex -w 32 -b 0x00010000 -e 0x00019FFF

<Notes>

Platform Designer で作成した On-Chip Memory の初期値設定において、Enable non-default initialization file = On によりデフォルト以外のファイルを指定している場合は、

elf2hex コマンドの -o を 目的のファイル名およびパス先で指定してください。

例) elf2hex software/app/build/Debug/presspb_led_niosv.elf -o ocram_init/niosv_boot.hex -w 32 -b 0x00010000 -e 0x00019FFF

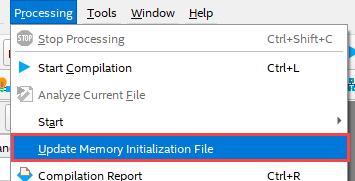

⑥ Quartus® Prime の下記メニューにより、FPGA 内蔵メモリーの初期値データ部分のみを更新します。

Processing メニュー ➤ Update Memory Initialization File

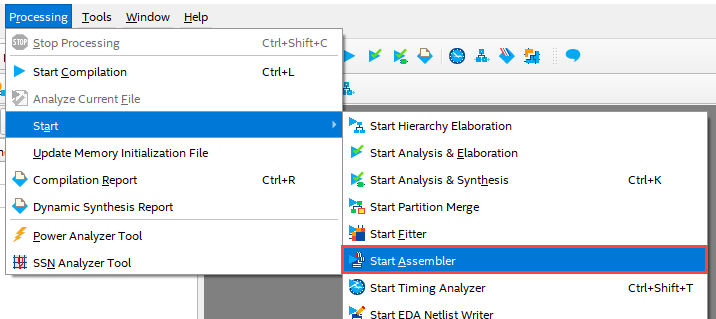

⑦ Quartus® Prime の下記メニューにより、FPGA 内蔵メモリーの初期値データ部分が更新された .sof ファイルが生成されます。

Processing メニュー ➤ Start ➤ Start Assembler

生成 (更新) された .sof を用いて、.pof や .jic を再生成してください。

![]() 今回のサンプルデザインは、わかりやすくシンプルな構成でしたが

今回のサンプルデザインは、わかりやすくシンプルな構成でしたが

ハードウェア側の論理回路や Nios® V システムをもっともっと拡張して作成すれば、さまざまな可能性が広がります。

みなさんも ぜひ挑戦してみてください。

サンプルプロジェクト

サンプルとして、今回の L チカ デザインの 作業ステップ 1~2 までを実施した Quartus® Prime プロジェクトの qar ファイルをアップロードします。

参考にしてください。

<Notes>

・ このサンプルプロジェクトは、Quartus® Prime Standard Edition 24.1 で作成しています。

・ Platform Designer で niosv_system.qsys を開き、Generate HDL を実行してから作業してください。

おすすめ記事/資料はこちら

FPGA のオンチップ・メモリーで Nios® II をブートさせてみよう

おすすめオンラインセミナーおよびワークショップはこちら

Agilex™ 5 FPGA で Nios® V を動かしてみよう ("オンラインセミナーを受講したい" を参照)

Nios® V プロセッサー 入門 コース ("トレーニングを受講したい" を参照)