電源ドック技術担当の佐々木です。

このコラムでは、色々なお客様サポートの中で複数回遭遇した、電源に関する不具合事例をご紹介していきたいと思います。

お客様から問い合わせフォーム経由で質問がありました。

多電源・低電圧化による現象

最近のデバイスは FPGA に限らず、多電源が必要になっていて本当に設計が難しくなっています。

どういったところが難しいですか?

まず、低電圧大電流化が進んでいて、ますます精度を要求されるところです。

そうですね。第14回のコラム にもありますが、基板上の配線抵抗や 0(ゼロ)Ω 抵抗でも問題になることがありますね。

はい、その他にも電源シーケンスの要求が厳しくなっています。

確かに、基板上に色々なデバイスが搭載されていると、昔のように抵抗とコンデンサーの時定数で シーケンス制御することも難しく、マイコンやシーケンサーを使用する必要がありますね。

そうなんです。

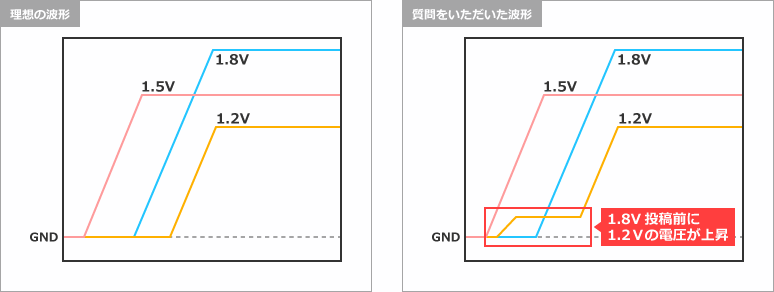

で、今回お聞きしたいことですが、デバイスが要求する電源シーケンスを守って電源を立ち上げているはずなのに、マイコンや FPGA などのデバイスの I/O ピンから電圧が漏れ出てくることがあります。

その結果、要求の電源シーケンスを守ることができません(下図参照)。

なるほど。これについては気にする必要はありませんよ。

電圧をモニターするとシーケンスを守れていないように見えますが、外部から与えている電源のシーケンスはデバイスの要求を満たしていますから。

え?!そうなんですか?

はい、デバイスが要求しているのは供給される電圧シーケンスの規定であって、デバイスの I/O などから漏れ出てきた電圧は無視できます。

そうなんですか!それなら良かったです。

ではなぜ、I/O などから電圧が漏れ出てくるのでしょうか?デバイスの品質として問題は無いのでしょうか?

電源が全て立ち上がるまではデバイス内部の論理は確定していないため、デバイスの内部は、P-N ジャンクションで作られる抵抗・ダイオードの塊です。

そのため、抵抗値が低いジャンクションを経由して I/O に電圧が見えることがあります。

品質に問題はありませんので、心配せずにお使いください。

なるほど、わかりました。

今回のポイント

電源シーケンスを守っていれば、I/O ピンからの漏れ電圧は気にしなくて良い。

質問フォームに寄せられたご意見のご紹介

[質問 1]

FPGA に対して問題ないという事ですが、1.2Vを供給する電源の入力電圧がゼロの状態で電源の出力端子に電圧が印加されると思います。こちらは問題ないのでしょうか?

[回答]

FPGA 側からの漏れ電流・電圧による印加であれば電力的に問題になることは無いと考えています。

理由としましては、FPGA の抵抗値が数KΩ 以上あって、電流値も mA オーダ以下に制限されるからです。

そのため、DC/DC 側の FET などがダメージを受けることは無く、問題にはなりません。

[質問 2]

どの DC/DC コンバーターにも、入力電圧ゼロの時に出力側に電圧印加可能でしょうか?

[回答]

故意の電圧印加は NG ですが、FPGA や CPU などの漏れ電流による電位上昇分が印加される分には問題ありません。

問題になる例としては、電圧が無い状態で DC/DC の出力に大容量のコンデンサーが接続してある場合です。

この場合、コンデンサーには大きな電荷が残っているので DC/DC 側に逆流して DC/DC の Low Side 側の FET を破損する可能性があります。