電源ドック技術担当の佐々木です。

このコラムでは、色々なお客様サポートの中で複数回遭遇した、電源に関する不具合事例をご紹介していきたいと思います。

お客様から「 FPGAのトランシーバーの通信エラーが出て困っている」との連絡が。

電源回路周辺のみのチェックで大丈夫?

数枚の基板でのみ、問題が発生しています。。

FPGA 周りの電源回路図や内部の論理設計なども見直しているのですが、原因が分からず行き詰っております。。。

まずは基板上のすべての電源電圧をチェックしてみましょう。

電源電圧をチェック

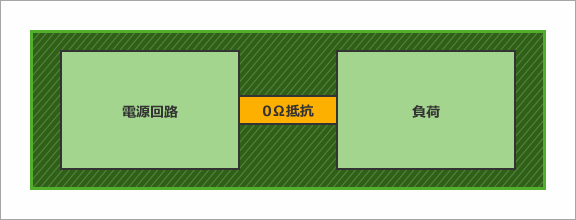

ん?この抵抗は何ですか?

これはデバック用に取り付けている 0(ゼロ)Ω 抵抗です。

これによって電源と負荷を切り離したり接続したりしています。

なるほど。

(これはあやしいな・・・)

では次に、トランシーバーに関係する電源の電圧を測定しましょう。

FPGA 直近の端子で電源電圧を測定していただけますか?

FPGA 直近の端子で電源電圧を測定

あ!電圧が 100mV もドロップしています!

これだと FPGA の要求スペックを満たしていません。。

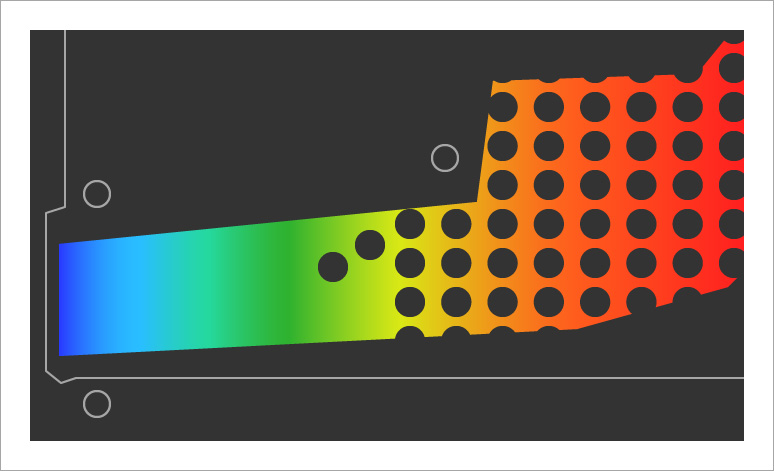

そうでしたか。この電源の内層パターンを見せていただけますか?

電源の内層パターンを確認

なるほど。

(これはあやしいな・・・)

電源パターンはできるだけ太くしているつもりなのですが、どこか問題はありますか・・・?

(ここにも問題があったか。。)

そうですね、問題が2つ見つかりました。

まず1つ目は、先ほどの0(ゼロ)Ω 抵抗のところです。この部分で配線が細くなっています。

2つ目はスルーホールの数です。

他の配線用に多くのスルーホールを開けていますが、これが原因で電源パターンが細くなっています(メッシュパターン)。

この2つが原因で抵抗値が上がり、電圧が下がってしまったようです。

ちょっとしたパターンの変化なのに、そんなにシビアな問題なんですか?

そうですね。

特にトランシーバー電源など、1.0V 以下の電源回路は配線パターンによる電圧降下の影響が大きいので、

あらかじめ降下分を見積もり、配線幅に問題がないかをチェックする必要があります。

そうなんですね。今後は気をつけるようにしたいと思います。

電源電圧降下の原因

0(ゼロ)Ω 抵抗とスルーホールにより、細くなってしまった配線パターン

今回のポイント

1.0V 以下の電源回路では、事前に電圧降下を見積もることが必要!

(それにより、電源要求を満たせるかどうかを判断する)