『豆知識:SSTL~その1』の続きになります。

スタブ抵抗により波形乱れが大きく改善されることを前回説明しました。

ところが、スタブの特性インピーダンスと I/O 端子の静電容量とは、一種の低域通過型(ローパス)のフィルタを形成します。

また、メモリパスには他の負荷も接続され、自分以外の負荷によっても全体的にローパスフィルタを形成しているので、高速化を阻害する要因となります。

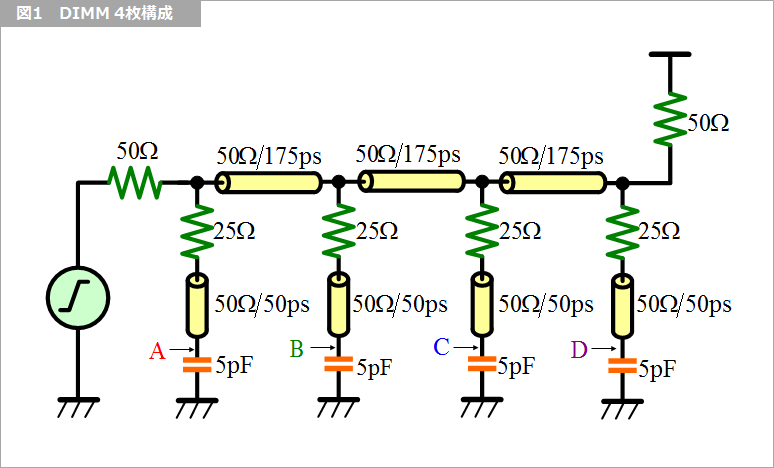

図1 は負荷が 4つ、すなわち、4本の DIMM の場合の SSTL 回路です。

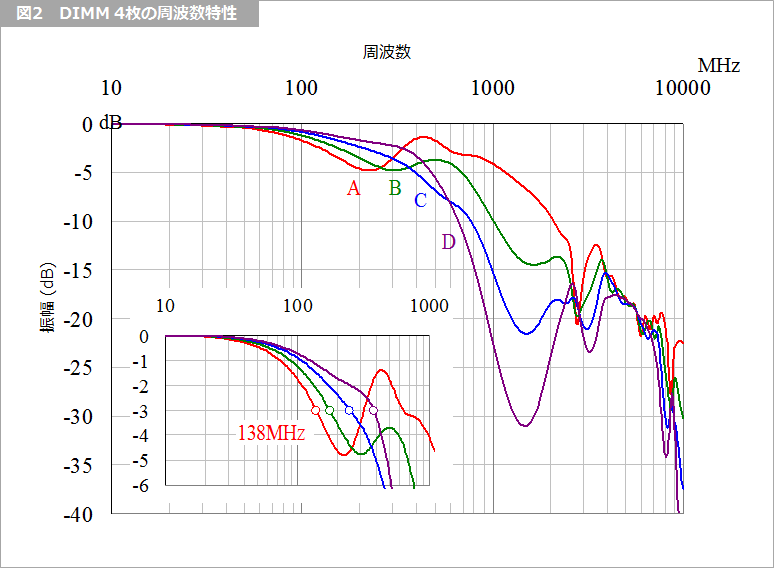

図2 に、Write 時のドライバからメモリの経路の周波数特性を示します。

4つの負荷のうち、ドライバに近い負荷 A の周波数特性が早く低下しています。周波数帯域は、一般に 3 dB 低下する周波数で定義します。同図で読み取ると、138 MHz です。

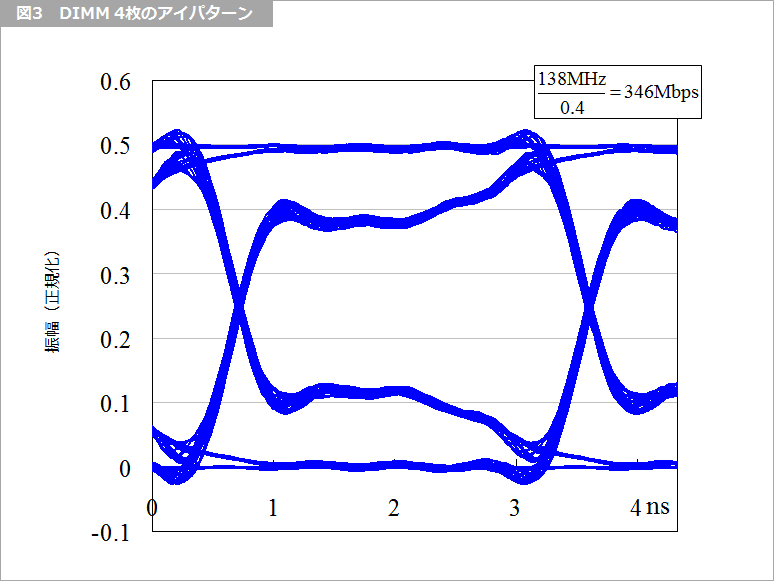

一般に、パルスの転送速度(Mbps)と周波数帯域(MHz)との間には MHz/0.4 = Mbps の関係があります。したがって、138 MHz ÷ 0.4 = 346 Mbps となり、図1 の回路では 346 Mbps あたりが転送速度の限界です。

図3 にこの転送速度のアイパターンを示します。

以上は、I/O 端子の静電容量が 5 pF の例ですが、DDR の初期はこの容量が 7 pF 程度でした。したがって、転送速度は 346 Mbps の 70 % 程度の 250 Mbps で、モジュール規格でいうと PC2100 程度が性能的には限界でした。IC のプロセスの微細化で端子容量は小さくなりましたが、転送速度を飛躍的に向上させるほどではありません。

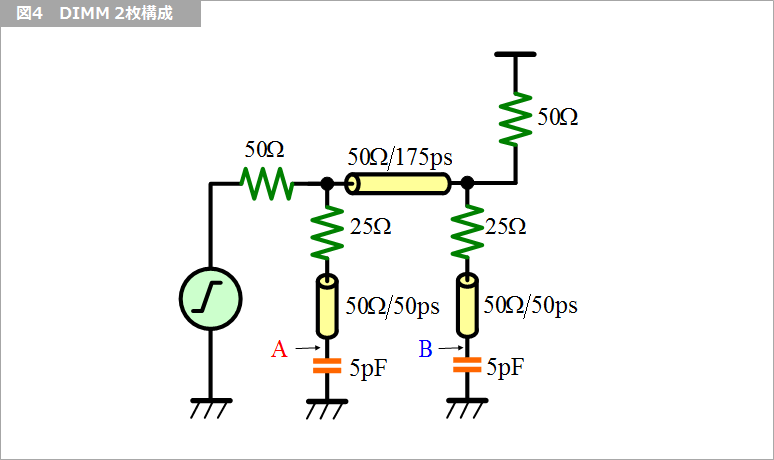

ここで登場したのがデュアルチャネル方式です。DIMM の枚数を 2枚に制限して 2チャネル構成とするもので、転送速度は単純に 2倍になります。また、DIMM の枚数を 2枚とすることにより、周波数帯域も向上します。

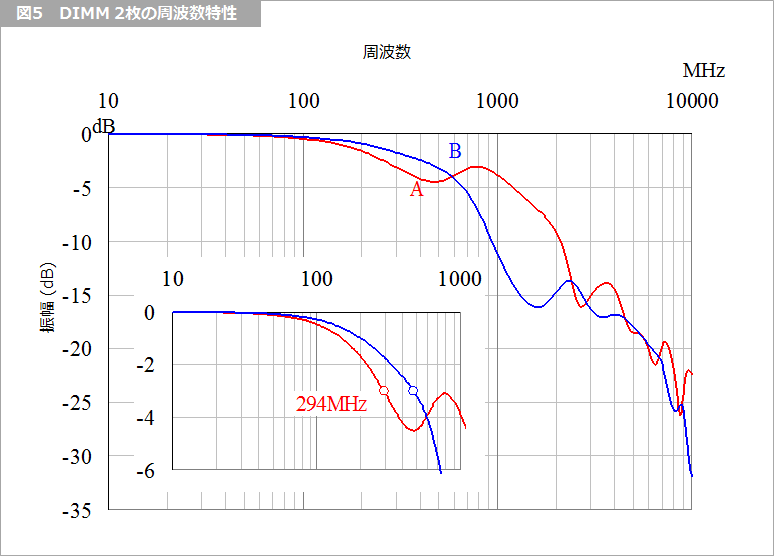

図4 の構成に対する周波数特性を 図5 に示します。

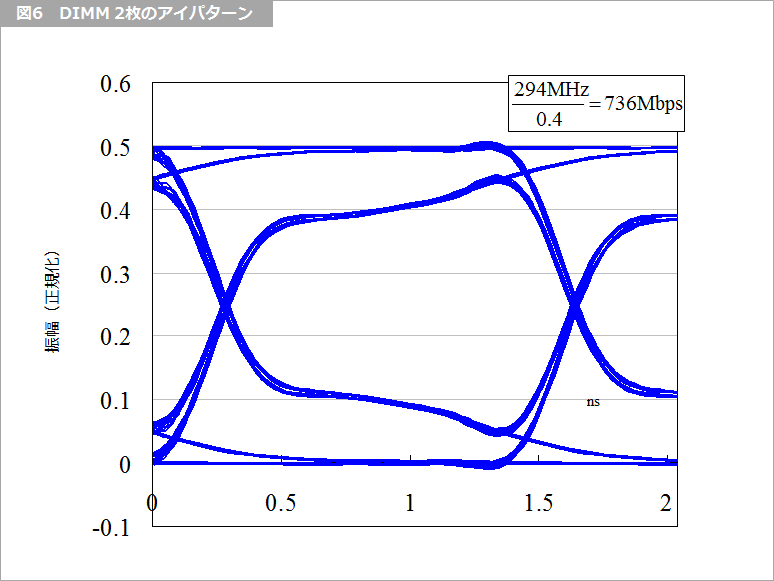

周波数帯域は 4枚構成の 138 MHz に対して、294 MHz と倍以上に向上しました。アイパターンを 図6 に示しますが、転送速度は単純計算で 736 Mbps まで向上しました。このほかにも IC プロセスの微細化により端子容量が小さくなると、転送速度が向上します。

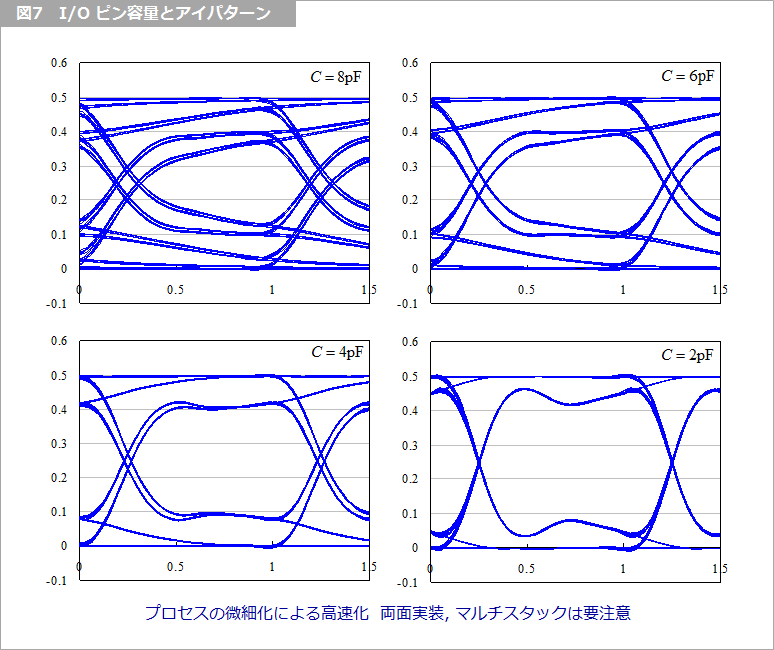

図7 には端子容量を 8 pF から 2 pF まで小さくしたときの 1 Gbps のアイパターンを示します。

メモリバスはスタブ抵抗を入れて波形乱れを格段に抑え、DIMM 4枚構成から 2枚構成のデュアルチャネル方式の採用により転送速度を向上させ、さらに、IC プロセスの微細化により転送速度を向上させてきました。

シグナルインテグリティとは直接関係はありませんが、次に登場した DDR3 は、チャネル当たりの転送速度はそのままにトリプルチャネル化により、デュアルチャネルの 1.5倍の転送速度を実現しました。

おすすめ記事/資料はこちら

======================================

碓井有三のスペシャリストコラムとは?

基礎の基礎といったレベルから入って、いまさら聞けないようなテーマや初心者向けのテーマ、さらには少し高級なレベルまでを含め、できる限り分かりやすく噛み砕いて述べている連載コラムです。

もしかしたら、他にも気になるテーマがあるかも知れませんよ!

こちら から他のテーマのコラムも覗いてみてください。