この記事では、リニアレギュレーターや LDO の基礎的な内容について解説していきます。今回は、アナログ・デバイセズ社の ADP1715 のデータシートをなどを参考に、一般的なリニアレギュレーターや LDO のノイズ除去特性に関する、電源電圧変動除去比 (PSRR) について解説していきます。

※ この記事は、データシートのほかに Practical Power Solutions(英文) の Section1 の前半にある内容を含めた記事となります。

リニアレギュレーターの PSRR 特性の効果

電源電圧変動除去比 (PSRR:Power Supply Rejection Ratio) は、入力電源からさまざまな周波数のリップル電圧が入ってきたときに、レギュレーターがどれだけリップルを除去(小さく)できるかを示す割合のことです。

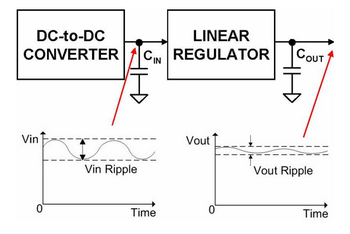

図1 のような電源構成をとった場合、前段の DC/DC コンバーターからのリップル (Vin Ripple) 電圧がリニアレギュレーターに入力されます。入力されたリップル電圧は、リニアレギュレーターの PSRR の特性によってノイズが除去(フィルタリング)され出力電圧リップル (Vout Ripple) は小さくなります。

PSRR の式と値

PSRR の式ですが、式1 のように入力電圧と出力電圧の比をとって対数表示にします。

PSRR 値は、大きい方がノイズ除去の特性が良いと言えます。ノイズ除去を期待してリニアレギュレーターを使用する場合は、PSRR 値が大きい製品を選定するようにしてください。

式1:PSRR の式

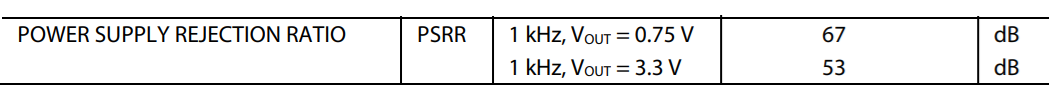

表1 は、ADP1715 の PSRR 値になります。3.3V 出力電圧設定の時に、周波数 1KHz の時の PSRR 値は 53 (dB) です。この場合、10mV の周波数 1KHz のリップル電圧が入力に印加されたとすると、式1 の計算式から出力電圧のリップルを求めると約 22uV となります。

PSRR の周波数特性

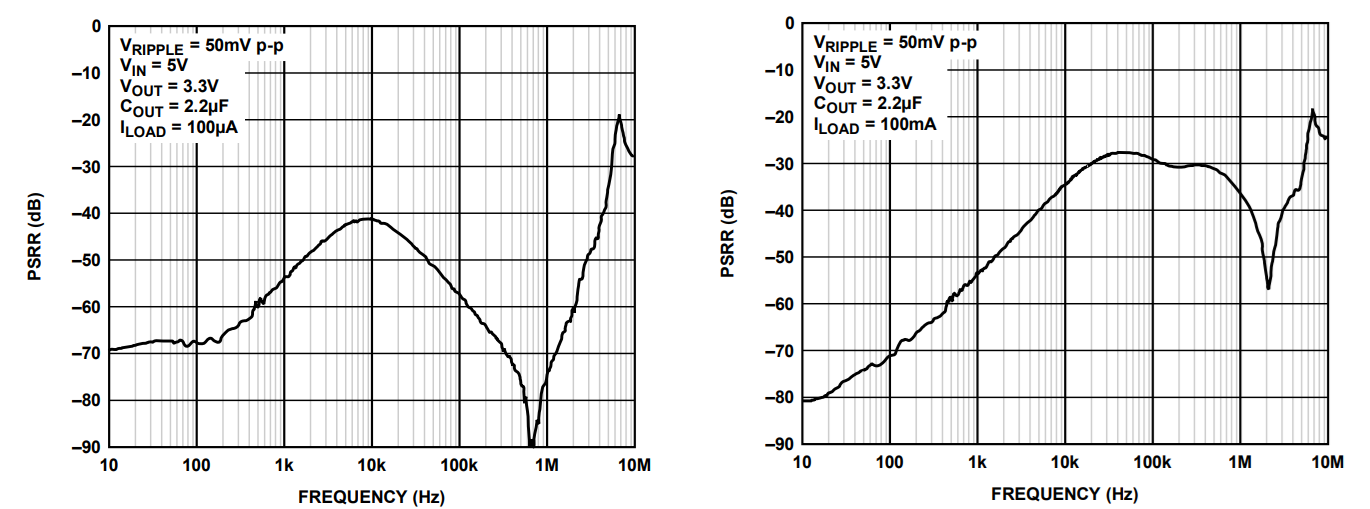

図2 は PSRR の周波数特性を表したグラフになります。2つのグラフ共に周波数が低い時には、PSRR が大きくフィルターの特性として効果大きく、周波数が高くなると PSRR 値が小さくなりフィルター効果が小さくなることがわかります。このように PSRR は、周波数特性を持つことに注意してください。

高い周波数の部分のノイズについては、リニアレギュレーターと負荷(FPGA やマイコン)間に配置するデカップリングコンデンサーを配置することが重要になります。

また、左と右のグラフは、リニアレギュレーターの出力電流が異なります。左側が ILOAD = 100uA で軽負荷に対して、右側は ILOAD = 100mA と負荷が重くなった場合の特性です。PSRR は、負荷電流が大きくなると低下する特性を持つことにも注意してください。

ADP1715 は、負荷が大きくなっても低周波数の PSRR は、0(ゼロ)になるなど極端に小さくなっていませんが、メーカーや製品によっては負荷電流を引くことによって PSRR が0(ゼロ)になってしまい、入力リップルをそのまま出力に出してしまうリニアレギュレーターも市場にはありますので注意してください。

おすすめセミナー/ワークショップはこちら

今回の技術記事にある、出力電圧誤差の見積もり方法やデジタル回路に与える影響などを知りたい方は、下記リンクのセミナー一覧の「デジタル回路設計者向け電源に関する基礎セミナー」の受講を検討ください(3-4ヵ月毎に開催)。

おすすめ記事/資料はこちら

LTspice 記事一覧:LTspiceを使ってみようシリーズ

アナログ機能ICに関する FAQ : FAQ リスト

技術記事一覧 : 技術記事

メーカー紹介ページ : アナログ・デバイセズ社

お問い合わせ

本製品に関して、ご質問などありましたら以下よりお問い合わせください。

アナログ・デバイセズ メーカー情報 Top へ

アナログ・デバイセズ メーカー情報 Top へ戻りたい方は以下をクリックしてください。