Altera® HLS コンパイラーが Quartus® Prime 開発ソフトウェア v17.1 から、すべてのエディション(Pro / Standard / Lite)で使用できるようになりました。これから HLS コンパイラーを使用するユーザー向けに、最適な情報を紹介します。

HLS コンパイラーとは?

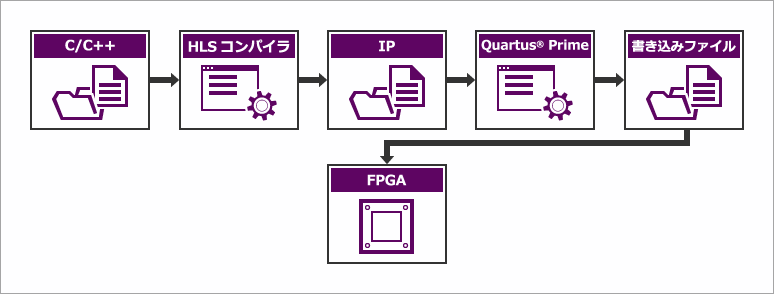

HLS コンパイラーとは、Altera® FPGA に対して最適化された High Level Synthesis (HLS) ツール、いわゆる高位合成ツールです。本ツールを使用することにより、C や C++ 言語のソフトウェア・プログラミング言語から Altera® FPGA へ実装するための回路(デザイン)を作成することができます。

今まではハードウェアの知識が必要だったデザインの作成を、ソフトウェア設計者でも作成できるようになったので、C や C++ の言語で記述されたフィルター処理や CPU では重かったソフトウェア処理部分を Altera® FPGA 向けの回路にオフロードさせ、システムの最適化がおこなえるようになりました。

HLS コンパイラーの資料

このページへアクセスすると、Altera® が用意している資料を見ることができます。

HLS コンパイラーの紹介ページ

(英語版 はこちら)

※ ドキュメントは「関連資料」(英語ページは「Document」)タブをクリックしてください。

以下の資料が用意されています。

- 製品概要

- 画像処理ホワイト・ペーパー

- 入門ガイド

- ユーザー・ガイド

- リファレンス・マニュアル

- ベスト・プラクティス・ガイド

- クイック・リファレンス・ガイド

- ホワイト・ペーパー「QRD 分解の最適化」

資料を複数紹介しましたが、どの順番で参照するのが良いか迷いますよね?HLS コンパイラーの使用方法を学ぶ上で、全体的なフローが理解できる資料の参照順序を紹介します。

1. 製品概要

HLS コンパイラーの製品概要です。ツールの大まかな全体像を理解することができます。

まずは、HLS コンパイラーを使用する上で必要な環境の構築方法について知ることが必要です。また、今後 HLS コンパイラーを用いる際に参考となる Example Design の内容を、事前に把握することも可能です。

HLS コンパイラーの環境構築方法については、こちらの記事をぜひご覧ください。

HLS コンパイラーの環境構築(Windows® 編)

2. ユーザー・ガイド

ツールのセットアップが終わったら、実際におこなうフローを学びます。ユーザー・ガイドでは HLS コンパイラーを使用してコンポーネントを作成し、合成や検証、シミュレーションの各手順を理解することができます。

Altera® FPGA 製品向けに設計する IP の合成や検証、シミュレーションの各手順を解説しています。合成時にシミュレーション用のテストベンチを作成することなど、検証やシミュレーション時の基本的なコマンドも含めた情報が記載されています。また、生成された IP を Quartus® Prime で使用するための手順や HLS コンパイラーの制限事項、レポートの概要説明も含まれています。

3. ベスト・プラクティス・ガイド

HLS コンパイラーにて、パフォーマンスを最適化する方法について習得することができます。具体的には、ループの最適化や最適なメモリー・アーキテクチャーの構成、コンポーネントのデータ型とコンバートの最適化によるパフォーマンスとロジック使用領域削減などです。

実際にコンポーネントを作成しても期待通りの性能になっていない場合は、資料に掲載されている最適化をおこないます。この資料では、ツールを使用してどこがボトルネックになっていて、どう最適化させるのかの一例を学ぶことができます。

最低限は上記の順序で資料を参照することにより、HLS コンパイラーの機能を一通り学ぶことが可能です。また、その他の資料にも有益な情報が記載されています。上記フローには記載していませんが、適時参照してください。

その他の資料については、以下のとおりです。

その他資料

画像処理ホワイト・ペーパー

画像処理を例として、HLS コンパイラーの設計フローを確認できます。アルゴリズムの説明や C++ 実装、そして 実際に HLS コンパイラーを使用してのハードウェア化、検証、最適化までの流れを解説しています。

HLS コンパイラーを使用する際に、どういうフローで実装すれば良いのかを具体例を用いて解説されているため、仕様検討から実装、最適化までの流れを知るためには最適な資料です。

入門ガイド

HLS コンパイラーを使用する上で必要なツールやライセンス設定、Example Design の紹介など環境構築に必要な情報が掲載されています。ツールをこれからご使用するユーザーにとても有益な資料です。

また、ライセンスによるトラブル・シューティングについても記載されているので、ライセンス設定が上手くできない場合にも参考になります。

リファレンス・マニュアル

コマンド・オプションやコンポーネント属性の指定などに困った時に参照します。

HLS コンパイラーのコマンド・オプションやコンポーネント、インターフェースの属性記述など実設計時に必要な情報が掲載されています。コンポーネント属性やインターフェースが決まり、ソース・コード編集時や HLS コンパイラーにおけるコマンド実行時に参照してください。

また、Appendix ではクリック・リファレンスとしてコマンドラインの引数やコンポーネント属性など一覧がまとまっています。引数やコマンドなどの検索にも使用できます。

ホワイト・ペーパー「QRD 分解の最適化」

固有値分解を例に、最適化の方法を理解することができます。

ベスト・プラクティス・ガイドで紹介している最適化の方法を使用し、QR 分解のコードのパフォーマンス向上の例を紹介しています。HLS コンパイラーを用いる上で、具体的な最適化の方法を実例を用いて理解することができます。

HLS コンパイラーを体験してみよう

このページで紹介した順番で資料を参照すれば、すぐに HLS コンパイラーの評価をおこなうことができます。

HLS コンパイラーを用いて、工数の削減やソフトウェア設計者がハードウェア設計をおこなう第一歩となれば嬉しいです。

環境構築の方法や簡易チュートリアルといった記事や資料を用意しています。ぜひ、HLS コンパイラーを使用してみてください。

おすすめ記事/資料はこちら

HLS コンパイラーの環境構築(Windows® 編)

HLS 簡易チュートリアル

High Level Synthesis 関連の記事や資料

Altera® FPGA の開発フロー/FPGA トップページ