PCIe SWとは

Peripheral Component Interconnect express(PCIe)、マザーボード上でこの名前を見たことがある人も少なくないかと思います。この規格を使用したPCIe Switchというものをご存じでしょうか?

PCIe SWは元をたどればCPUからメモリーへアクセスするための規格でしたが、現在ではサーバーやストレージに使用されることも多くなっています。また、高速通信に興味を示していなかった業界内でも、高精度のカメラや5Gの出現などと共にデータの大容量化が進むにつれ、高速通信に注目が集まっています。本記事ではPCIe SWの基本的な機能や特徴についてにフォーカスしながら順に解説していきます。

PCIeのアーキテクチャー

ここまでの解説では、PCIeにおけるRCとEPの関係やそれらを設定するConfig空間など全体像をイメージできるように解説をおこなってきました。第3回からは、PCIeSWに使用されている規格である、PCIeのアーキテクチャーについての解説をおこなっていきます。

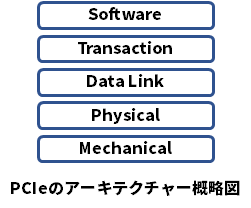

PCIeのアーキテクチャーはレイヤー構造をとっており、各階層に役割が明確に分けられています。ソフトウェア層ではドライバーやアプリケーション、トランザクション層はデータの送受信、データリンク層は通信相手との通信の管理を定義しています。このように役割毎に区切られた作りになっているため、製品仕様の変更や拡張がPCIに比べて容易であるとされています。

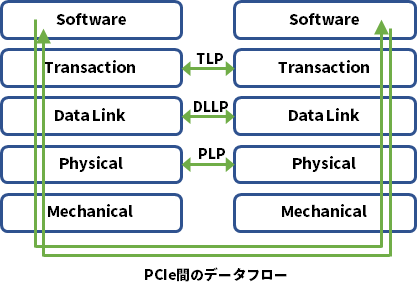

PCIeの通信ではパケットと呼ばれるデータ形にして取り扱います。このパケットは層毎にやり取りをおこなうため、送信時には下層を通過するにつれ情報が付加されていき、受信時には上層に行くにつれ情報の削除がおこなわれます。これにより対応する層毎にデータのやりとりをおこなうことが可能となります。

また、層毎のパケットはそれぞれ、Transaction Layer Packet(TLP)、Data Link Layer Packet(DLLP)、Physical Layer Packet(PLP)と呼称されます。

第3回ではPCIeのアーキテクチャーついて簡単に解説しました。第4回の記事でも引き続きPCIeSWに関連する基礎知識について解説していきます。

お問い合わせ

本記事に関してのお問い合わせ、ご質問は、以下のボタンからお願いします。

Microchip メーカー情報Topへ

Microchip メーカー情報Topページへ戻りたい方は、以下をクリックください。