PCIe Switch (PCIe SW)とは

Peripheral Component Interconnect express(略してPCIe)。この名前をマザーボードのコネクター部で見たことがある人も少なくないかと思います。この規格を使用したPCIe Switch(略してPCIe SW)というものをご存知でしょうか?

PCIeは元をたどればCPUからメモリーへアクセスするための規格でしたが、現在ではサーバーやストレージに使用されることが多くなっています。また、高速通信に興味を示していなかった業界でも、高精度のカメラや5Gの出現など、データの大容量化が進んだため高速通信への関心が高まっています。本記事ではPCIe SWの基本的な機能や特徴についてにフォーカスしながら順に解説していきます。

PCIeに関する予備知識

本題の機能や構成の解説を始める前に少しだけ補足します。PCIe SWは通信の規格ですので、Generation毎に通信速度が定義されています。Gen1=2.5, Gen2=5.0, Gen3=8.0, Gen4=16.0, Gen5=32.0Gbpsとなり、Gen6=64.0Gbpsの開発が進行しているという話もあります。Microchip社製のPCIe SWではGen3とGen4に関するお問い合わせが中心となっています。Gen毎に「対応レーン数(24, 68など)」や「FWのカスタマイズに対応しているか」など細かに性能差が設けられており、お客様のニーズにあった製品のご提供が可能です。本ページの下部にMicrochip社PCIe SW製品のページリンクの一例を記載しておりますので、ご興味のある方はそちらからご確認ください。

PCIe SWのルートコンプレックス(RC)とエンドポイント(EP)について

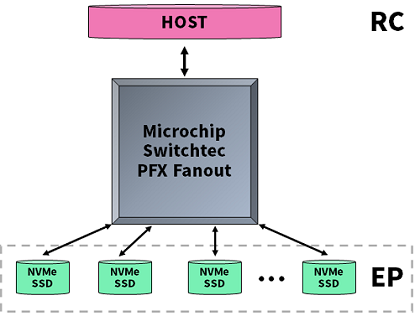

第一回ではPCIe SWを用いたdeviceの最も基幹となるRC(Root Complex)とEP(Endpoint)について解説していきます。PCIe SWはHostから発信したデータを下流のエンドデバイスに分配(Swiching)する機能が中心です。このときのHostをRC、End deviceをEPとして認識します。(下図参照)

RCが投げたデータをPCIe SWが受け取った後、各EPへ適宜スイッチングしながら伝達します。もちろんパケットのロスや化けたパケットなどあってはならないので、PCIe SWはパケットを保護する機能も備えています。

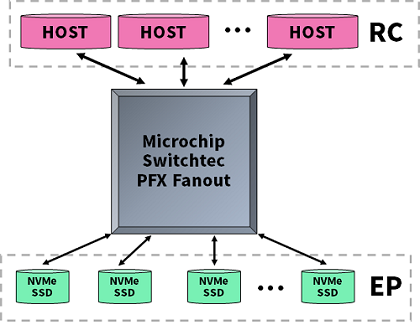

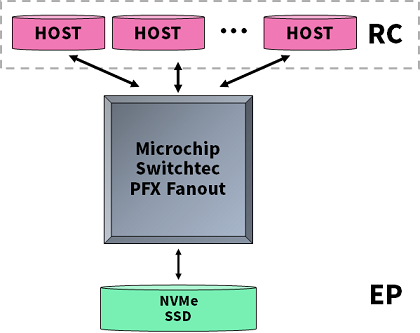

また、PCIe SWは一つのPCIe SWに対して複数のRCとEPを持つことができます。弊社で取り扱っているMicrohip社製のPCIe SWはRCからその他のRCへのアクセスも可能にしており、RC間の制御による冗長性の確保など利便性に長けています。RCはCPU、EPはSSDなどが使用されることを踏まえて総括しますと、単一または複数のCPUに対して複数(または単一)のSSDへデータを高速で分配する際にPCIe SWを用いるということになります。(下図参照)

第一回ではPCIe SWのRCとEPについて簡単に解説しました。第二回の記事ではPCIe SWのMemory空間とConfig空間について解説します。

メーカー製品ページリンク

お問い合わせ

本記事に関してのお問い合わせ、ご質問は、以下のボタンからお願いします。

Microchip メーカー情報Topへ

Microchip メーカー情報Topページへ戻りたい方は、以下をクリックください。