はじめに

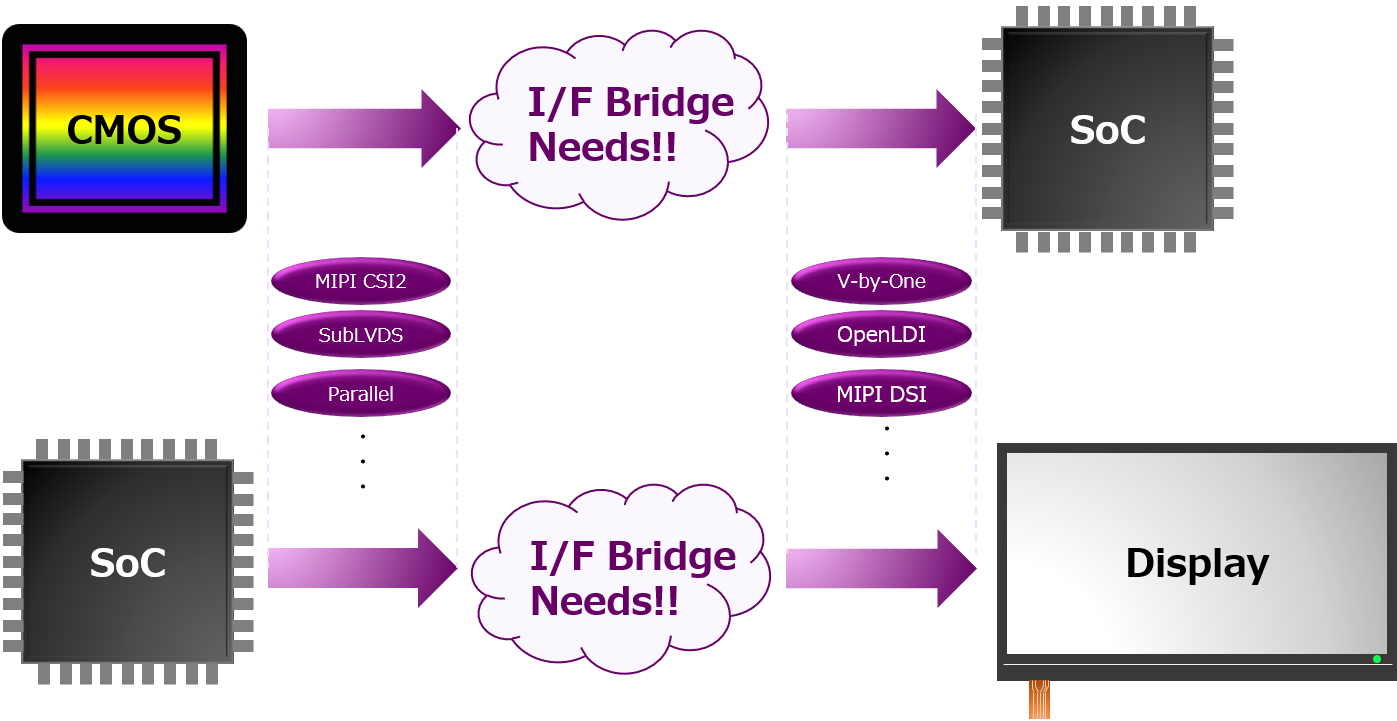

近年、カメラの高解像度化が進む中、撮像素子として使用されるCMOSセンサーの性能は飛躍的に向上しており、扱う映像伝送データ量の向上とともにCMOSセンサーの出力インターフェースも変化してきています。

デジタルカメラ、一眼レフ、業務用カムコーダー、医療用カメラ、車載カメラ、FAカメラといった幅広い分野に対して、MIPI I/F出力のCMOSセンサーの採用が進む中、CMOSセンサーに接続されるSoCやCPUなどにはMIPI I/Fがサポートされていない、又はMIPIポートが不足するケースが多く存在します。

業務用カムコーダ、一眼レフについては、サブモニター、背面ディスプレイ、電子ビューファインダーが搭載されており、これらで使用されているディスプレイもMIPI I/F対応のものが増えてきており、これらもSoC, CPUとのインターフェースと互換性が無い為に、直接接続できません。

これらの理由から、CMOSセンサー、ディスプレイを扱う製品では下図のようなCMOSセンサーとSoC間、SoCとディスプレイ間のインターフェース変換の必要性が増えてきています。

こういったインターフェース変換が必要な場合に便利なのが、FPGAを使用したインターフェース変換です。

特に、Lattice FPGAでは、MIPI I/Fを中心にCMOSセンサー、ディスプレイ側の相互インターフェース変換を得意とするデバイスを豊富に取り揃えており、FPGAならではの柔軟性を生かしたソリューションを多数持っています。本ページでは、インターフェース変換を主としたLattice FPGA活用例を紹介していきます。

本記事では、下記4つのケースをピックアップして紹介していきます。

2. インターフェース変換+画像処理を実施したい

3. 複数系統の映像信号を並列処理させたい

1. 複数のCMOSセンサーを接続したい

近年増加している複眼カメラを想定したケースでは、映像処理を行うSoC, CPUに複数のMIPIポートが搭載されていない為に、直接CMOSセンサーを接続できないケースが多くあります。Lattice FPGAでは下図のようにMIPI I/F複数チャンネルを1チャンネルのMIPI I/Fに束ねるアグリゲーション機能を実現できるため、複数のCMOSセンサーの接続が可能となります。尚、各CMOSセンサーの識別はVC(バーチャルチャネル)情報によって識別が可能です。

Lattice FPGAでは、業界最速のMIPI I/F Max2.5Gbps/laneまでをサポート可能なデバイスも取り揃えておりますので、複数の高解像度CMOSセンサーを接続して、MIPI I/Fアグリゲーションさせることが可能となります。

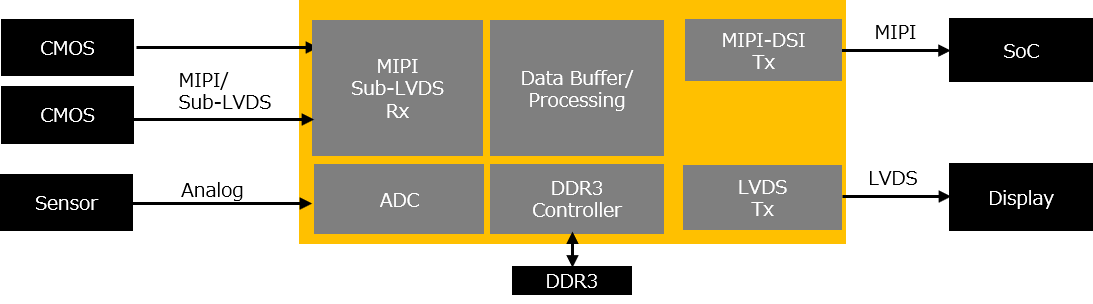

また、DSP、DDRメモリインターフェースを搭載したFPGAもあるので、下図のようにMIPI I/Fのアグリゲーションと同時に画像処理機能を実装することで、後段のSoC, CPUの負荷を減らすことも可能です。

※下図ブロックの黄色部分がLattice FPGAとなります。

①Lattice FPGAによるMIPI I/Fアグリゲーションの構成例

2. インターフェース変換+画像処理を実施したい

CMOSセンサーからのインターフェースを変換するだけではなく、同時に画像処理を実現するケースです。

インターフェース変換と同時に画像処理を実現するケースは1項でも触れましたが、この例は画像処理をメインとしたケースとなり、SoC, CPUで実現していた画像処理機能のすべてをFPGA内部に取り込み、チップ点数を減らすソリューションとなります。

Lattice FPGAの場合は、インターフェース変換と同時に画像処理を実現するケースにおいて、小型パッケージ+低消費電力のFPGAをご提案することが可能です。

また、LVDS, Sub-LVDS, SLVSなどのクロック並走型のインターフェースはもちろん、クロック埋め込み型の高速伝送インターフェースにも対応可能なFPGAもございますので、幅広い分野での提案が可能となっています。

※下図ブロックの黄色部分がLattice FPGAとなります。

②Lattice FPGAによるインターフェース変換+画像処理の構成例

3. 複数系統の映像信号を並列処理させたい

下図のように2つのCMOSセンサーから入力された映像信号をFPGA内部で分岐させて、片方のチャンネルを後段SoCへ入力、もう片方のチャンネルをディスプレイに接続するといった、複数チャンネルの映像信号を並列に変換、処理させることが可能です。

インターフェース変換では専用チップが使用されるケースもありますが、このような複数系統の並列に変換、処理をワンチップで実現するにはFPGAが最適です。

SoCの仕様変更や、接続しているディスプレイの仕様変更が生じたとしても、FPGAであれば大規模な基板改版を行うことなく、FPGA内部回路を変更するのみで、柔軟に対応することが可能です。

Lattice FPGAの場合、MIPI I/F、及びその他インターフェースRx, Tx部のリファレンスデザイン、IPが多数リリースされておりますので、突然の仕様変更があった場合でも工数をかけることなく実装可能なケースがあります。

※下図ブロックの黄色部分がLattice FPGAとなります。

③Lattice FPGAによる複数系統映像信号の並列処理構成例

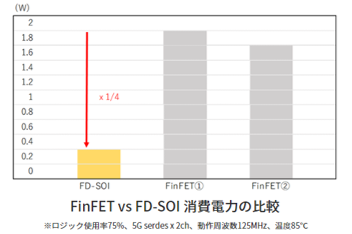

4. 消費電力は抑えつつ高速通信を行いたい

LatticeはFD-SOIというプロセスを採用したNXシリーズという新しいFPGAを随時開発しており、映像/画像系のI/F SLVS-ECやCoaXPressの高速通信を行いながらも低発熱を実現可能です。

下図のようにCMOSセンサーから入力された映像信号をFPGA内部で処理を行い、後段SoCへ入力するといった、MAX10Gbps高速通信とデータ処理を低消費で実現可能です。

SoCの仕様変更、入手性などの影響や、機能アップに伴うCMOSセンサーの仕様変更が生じたとしても、FPGAであれば大規模な基板改版を行うことなく、FPGA内部回路を変更するのみで、柔軟に対応することが可能です。

また、他社のFinFETと同じ条件で消費電力を比較すると、約1/4の低消費電力を実現可能です。

※下図ブロックの黄色部分がLattice FPGAとなります。

④Lattice FPGAによる高速通信構成例と消費電力比較

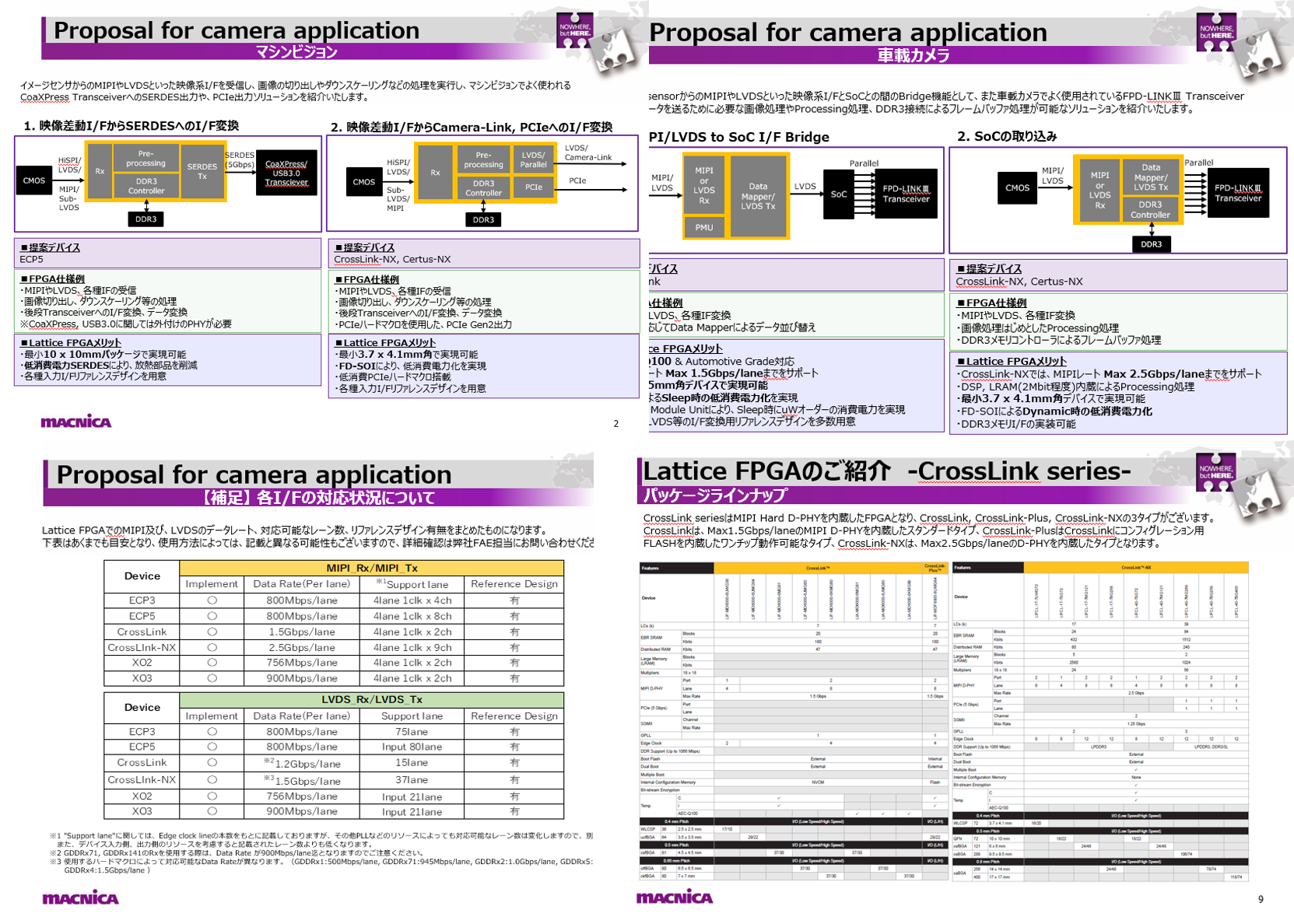

資料ダウンロード

これらのソリューションが実現できる具体的な製品名や、パッケージラインナップについても知りたい方は、下記の資料により詳しい情報を記載してあります。冒頭に記載のとおり、本記事で紹介したのは一例ですので、他にも様々なソリューションがあります。合わせてぜひご覧ください!

日本語マニュアル付き!MIPI CSI-2 リファレンスデザインを無償で提供中!

マクニカオリジナルの MIPI CSI-2 リファレンスデザインを作成しました。

以下ボタンより情報入力いただくことで、無償でダウンロードすることが可能です。

その他にも、MIPI DSI やSERDESのリファレンスデザインもご用意しております。

詳しくは、こちらよりご確認ください。

▼▽▼▽▼▽▼▽▼▽▼▽▼

お問い合わせ

本記事に関してご質問ありましたら以下より問い合わせください。