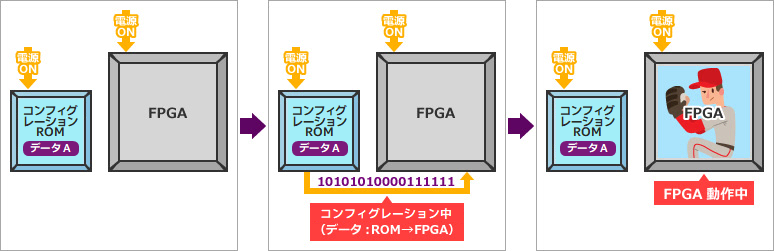

コンフィグレーションとは?

簡単に言うと、SRAM ベースの FPGA にデザイン(設計)データをロードすることです。

FPGA は SRAM ベースのデバイスなので、電源投入しただけでは何も動きません。動作させるには、FPGA のデザイン・データを ROM から転送させる必要があります。

これをコンフィグレーションと呼びます。

電源投入後のコンフィグレーションは、一般的には自動的に開始されます。

コンフィグレーション ROM には FPGA のデザイン・データ(コンフィグレーション・データ)を事前に書き込んでおく必要があります。

これをプログラミングと呼んでいます。

プログラミングについては、別の記事で一例を紹介しています。

FPGA 経由で EPCQ デバイスへプログラミング(JIC プログラミング)

コンフィグレーションの種類(スキーム)

コンフィグレーションの種類(スキーム)は、大きく分けて 3種類あります。

MSEL ピンというコンフィグレーションのモードを決定するピンの状態を電源投入時に認識して、そのモードによるコンフィグレーションがなされます。MSEL ピンの設定とコンフィグレーションのモードとの関係は、FPGA ファミリによって異なるので、使用する FPGA のドキュメントを必ず確認してください。

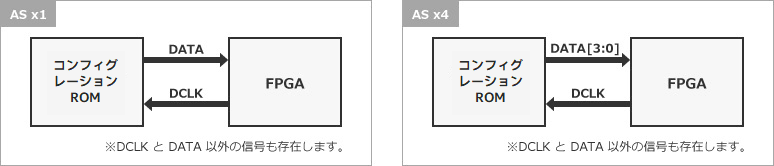

Active モード

FPGA 自身がコンフィグレーションの制御をおこない、コンフィグレーション ROM からのデザインデータを受け取ります。

使用できるコンフィグレーション ROM は、Altera® 純正のコンフィグレーション・デバイス(EPCQ-A / EPCQ / EPCS)や一部のサード・パーティー製 Flash メモリーです。

デバイス・コンフィグレーション - サポートセンター (Altera)

デザイン & デバッグ・ガイドラインも、参考にしてください。

アクティブ・シリアル・コンフィグレーション デザイン & デバッグ・ガイドライン

- Active Serial (x1):データが 1本

- Active Serial (x4):データが 4本

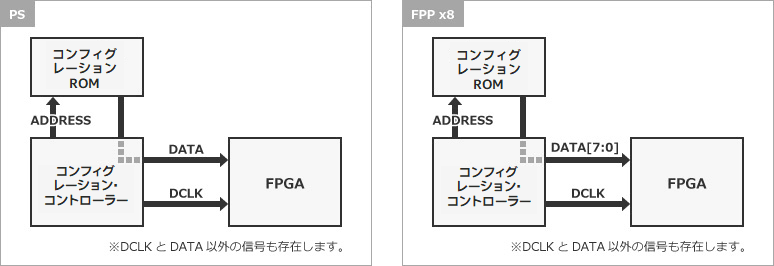

Passive モード

外部にコンフィグレーションを制御するデバイスがあり、FPGA はコンフィグレーション ROM からデザイン・データを受け取るのみです。

コンフィグレーション・コントローラーとしては、マイコンや Parallel Flash Loader (PFL) IP を実装した MAX® 10 / MAX® V / MAX® II などが考えられます。マイコンによる制御の場合は、ユーザーが制御プログラムなどをすべて作成する必要があります。(無償の PFL IP による制御の方が、ユーザーに負担が少なくオススメです。)

使用できるコンフィグレーション ROM は、CFI / QSPI / NAND Flash メモリーです。

- Passive Serial (PS)

FPGA が受信するDATA 線が1本(シリアル)

- Fast Passive Parallel (FPP)

FPGA が受信する DATA 線が複数本(8/16/32 本)

なお、PFL IP を使用する場合、PFL がサポートしている Flash メモリーがユーザーガイドに記載されています。詳しくはドキュメントをご覧ください。

Parallel Flash Loader (PFL) IP のユーザーガイド

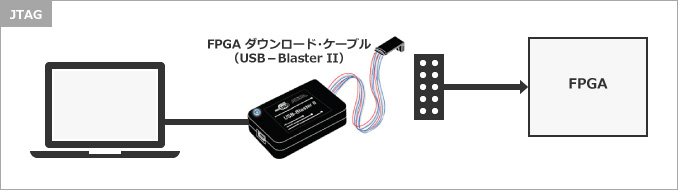

JTAG モード

JTAG モードは、おもにデバッグ時に使用するモードで、SOF ファイルを Quartus® Prime の Programmer から FPGA ダウンロード・ケーブル(USB-Blaster II など)を使用して FPGA の JTAG ポートから直接コンフィグレーションさせます。

コンフィグレーション ROM の容量の選び方

FPGA のデザインデータは、使用する FPGA によって異なります。基本的には、FPGA のドキュメントに記載されている RBF ファイルのサイズより大きいものを選んでください。

なお、このコンフィグレーション・データを圧縮してコンフィグレーション ROM に格納することができます。その時の圧縮率は、コンフィグレーション・データのビットストリームに依存するので、事前に圧縮率を知ることはできません。

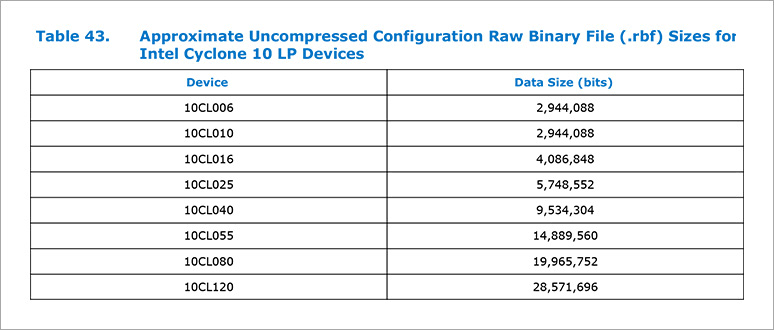

Cyclone® 10 LP を例に説明します。Cyclone® 10 LP は、下図のように 8種類の Density(ロジック規模)のデバイスが用意されており、それぞれの RBF サイズが示されています。基本的には、この RBF サイズを目安にコンフィグレーション ROM に容量を選定します。(開発時には、最新の英語版のドキュメントで必ずご確認ください。)

各 FPGA のコンフィグレーション・サイズは、ドキュメントで確認できます。

Stratix® 10 / Stratix® V

Arria® 10 / Arria® V

Cyclone® 10 GX / Cyclone® 10 LP / Cyclone® V

※ Configuration Bit Stream Sizes や Raw Binary File Size などのキーワードで検索してください。

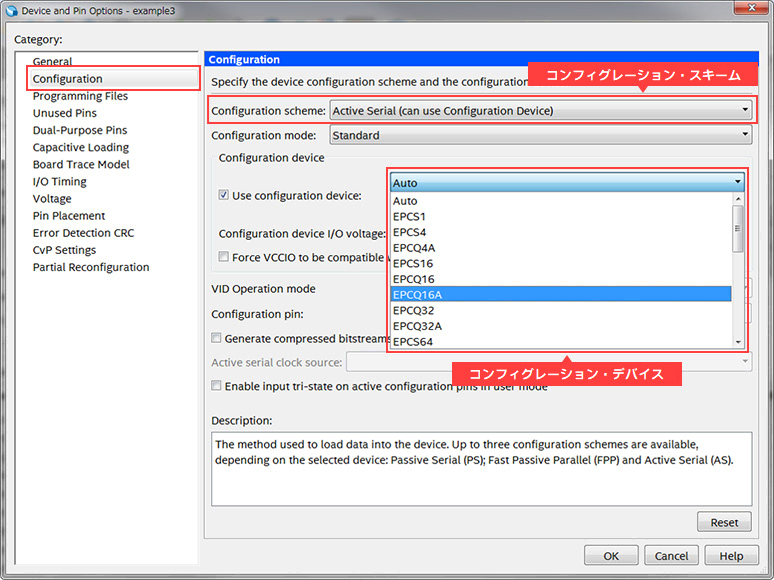

Quartus® Prime でのコンフィグレーションの設定

Quartus® Prime でコンフィグレーションの設定をしておけば、コンパイル時にプログラミング・データを自動で生成してくれます。

コンフィグレーションの設定やプログラミング・データの変換については、こちらをご覧ください。

Quartus® Prime デバイス・オプションの設定方法

Quartus® Prime プログラミング・ファイルの生成や変換(Convert Programming Files)

おすすめ記事/資料はこちら

アクティブ・シリアル・コンフィグレーション デザイン & デバッグ・ガイドライン

Quartus® Prime デバイス・オプションの設定方法

Quartus® Prime プログラミング・ファイルの生成や変換(Convert Programming Files)

Altera® FPGA の開発フロー/FPGA トップページ

おすすめ FAQ はこちら

おすすめセミナー/ワークショップはこちら

Quartus®Prime 入門編トライアル・コース <無料>

カスタムマイコン設計トライアル ~MAX® 10 FPGA を使った組込み設計を体感!~ <無料>