FPGA は知っての通り、電源投入時に FPGA の回路データ(コンフィギュレーション・データ)を格納しているフラッシュ・メモリからコンフィギュレーションさせないと、動作しません。そのフラッシュ・メモリに FPGA の回路データを事前にプログラミングしておく必要があります。

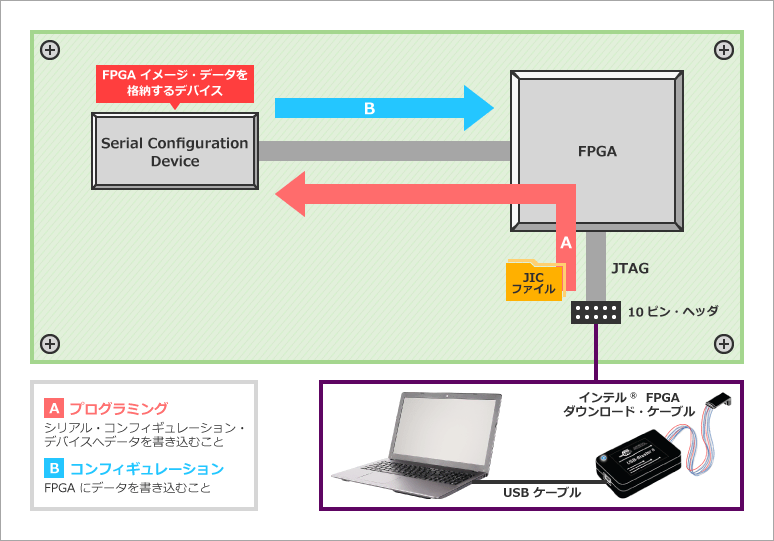

JTAG ポートから FPGA を経由してフラッシュ・メモリへプログラミングできれば、10ピン・ヘッダが 1個で済んで部品コストとスペースが節約できます。

JTAG ポートから FPGA 経由でプログラミングする便利な方法を紹介します。なお、Cyclone® V を例に説明していますが、他の FPGA でも実現できます。

JIC プログラミングの概要

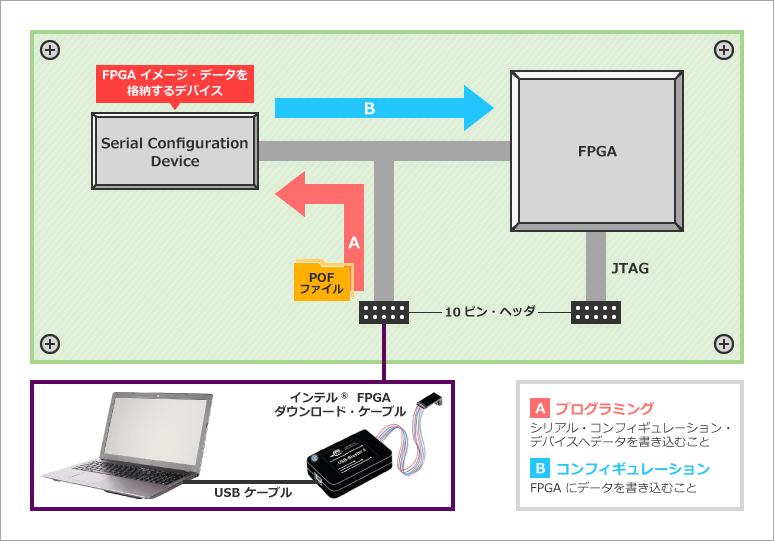

インテル® FPGA のコンフィギュレーション方法として Active Serial (AS) モードを選んだ場合、FPGA イメージを格納しておくデバイスは EPCQ デバイスや EPCS デバイスといったインテル® FPGA シリアル・コンフィギュレーション・デバイスを使用します。この EPCQ デバイスや EPCS デバイスへのプログラミングにはインテル® FPGA ダウンロード・ケーブル(USB-Blaster™ や USB-Blaster™ II など)を使用しますが、ダイレクトにプログラミングする方法と FPGA を経由してプログラミングする方法があります。

ダイレクトにプログラミングする方法を AS プログラミングといい、インテル® Quartus® Prime / Quartus® II 開発ソフトウェアで生成された POF ファイルをそのままプログラミングできます。しかし、ボード上に 10 ピンのヘッダ(コネクタ)を JTAG ポート用とは別に用意する必要があります。

JTGA ポート用のヘッダはデバッグでも使用する機会が多いので、実装するケースが大半です。そうなると、同じ 10 ピンのヘッダを 2個実装することになり、部品のコストと実装スペースが増えてしまいます。

JTAG ポートから FPGA を経由して EPCQ デバイス / EPCS デバイスへプログラミングできれば、10ピン・ヘッダが 1個で済みます。この方法を JTAG Indirect Configuration (JIC) プログラミングといいます。

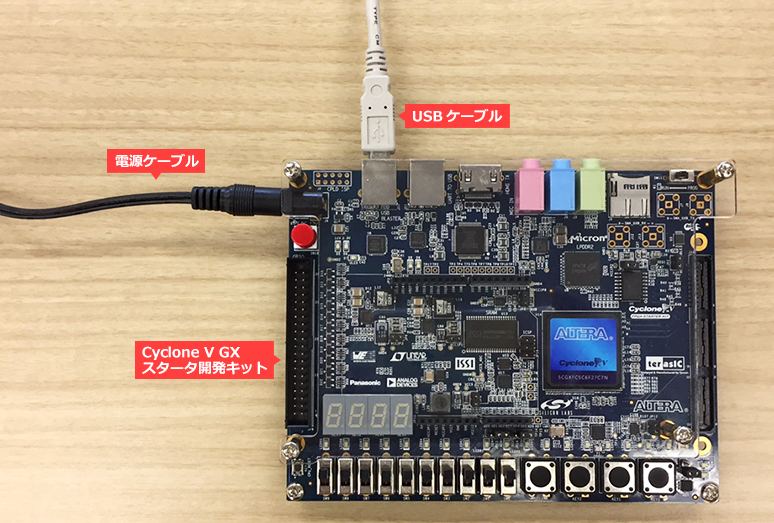

ワークショップ(Quartus® Prime 入門編トライアル)で使用している Terasic 社の Cyclone® V GX スタータ開発キットを例に、JICプログラミングの方法を説明します。

なお、初めて USB-Blaster™ II や USB-Blaster™ を使用する場合は、各プログラミング・ハードウェアのドライバをインストールする必要があります。ドライバのインストールが済んでいない場合は、こちらをご覧ください。

【TIPS】 USB-Blaster™ II のドライバーをインストールしてみよう (MACNICA フォーラム)

【TIPS】 USB-Blaster™ のドライバーをインストールしてみよう (MACNICA フォーラム)

JIC ファイルの生成と書き込み

環境

- ツール:Quartus® Prime v16.1

- 開発キット:Cyclone® V GX スタータ開発キット (Terasic 社)

手順

- JIC ファイルの作成(SOF ファイル → JIC ファイルへの変換)

- JIC ファイルの書き込み

JIC ファイルの作成(SOF ファイル → JIC ファイルへの変換)

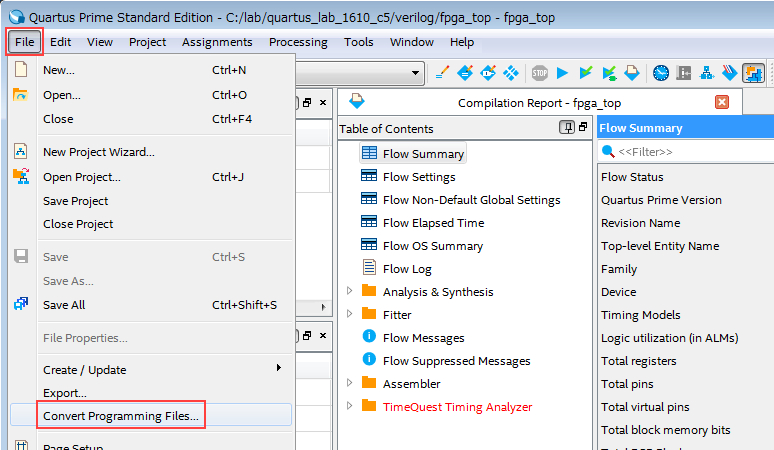

Quartus® Prime / Quartus® II の File メニュー ⇒ Convert Programming Files を選択します。

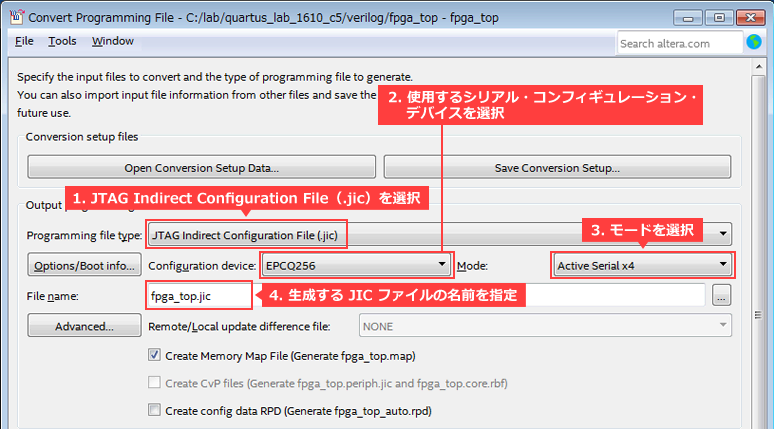

Convert Programming Filesウィンドウが開いたら、以下の設定を行います。

- 生成するプログラミング・ファイルのタイプを選択

- JTAG Indirect Configuration File(.jic)を選択

- コンフィギュレーション・デバイスを選択

- Cyclone® V GX スタータ開発キットに実装されている EPCQ256 を選択

- モードを選択

- Active Serial x4 を選択

- 生成する JIC ファイルの名前を指定

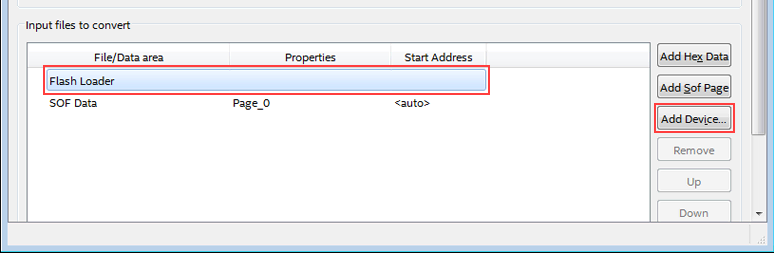

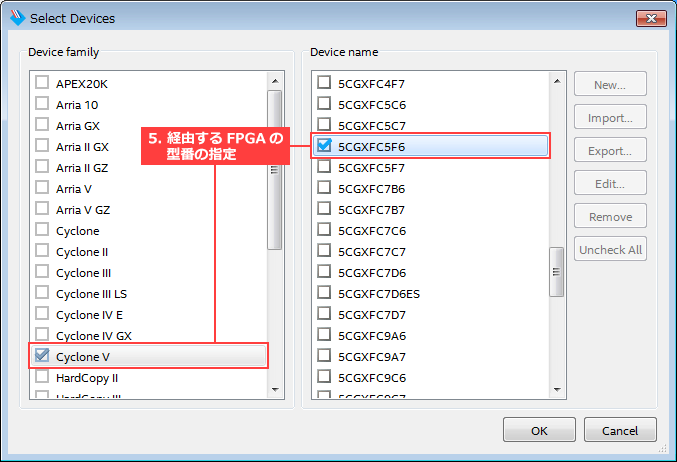

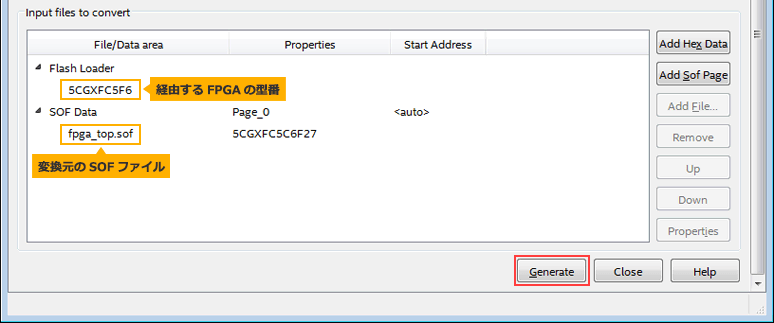

次に、経由させる FPGA を指定します。

- 経由する FPGA を指定

- デバイス・ファミリは Cyclone V を指定

- デバイス名は 5CGXFC5C6 を指定

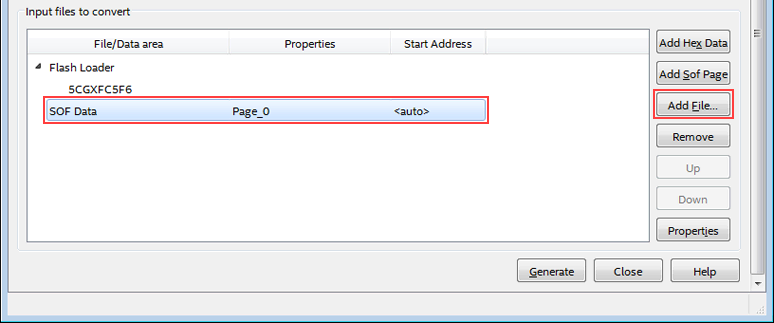

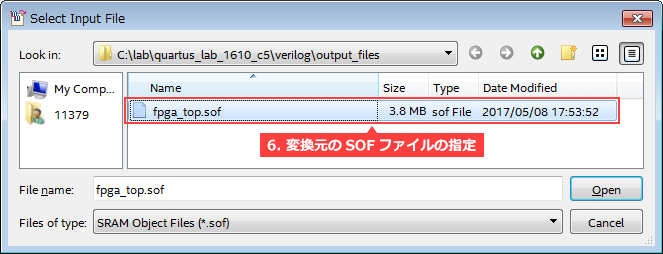

さらに、変換元の SOF ファイルを指定します。

- 変換元の SOF ファイルを指定

必要な設定ができたら、Generateをクリックして JIC ファイルを生成させます。

生成に成功しましたか?

JIC ファイルの書き込み

ボードとダウンロード・ケーブルを準備して、接続します。

なお、開発キットの多くはボード上にダウンロード・ケーブルの機能が実装されているため、PC と開発キットの間を USB ケーブルでつなぐだけで、ダウンロード・ケーブルを認識できます。今回もこのケースに該当します。

皆さんが作成したボードの場合は、ダウンロード・ケーブルを JTAG 用の 10ピン・ヘッダに接続します。

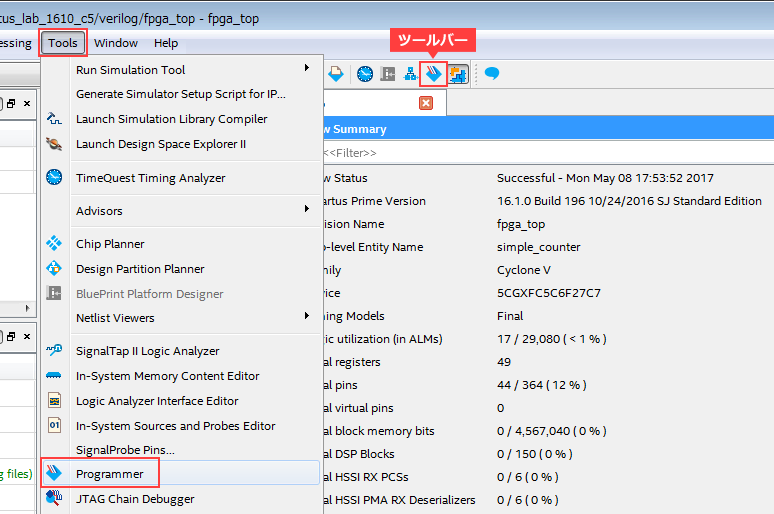

ボード(開発キット)の電源をオンします。そして、Quartus® Prime / Quartus® II の Tools メニュー ⇒ Programmer を選択またはツールバーをクリックして、Programmer を起動します。

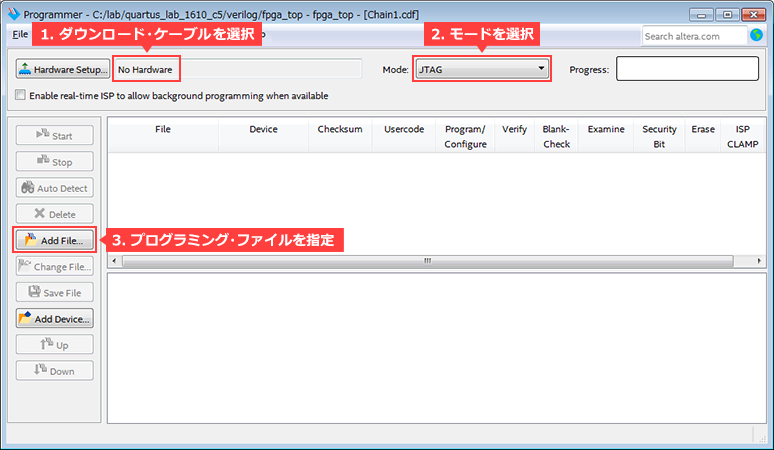

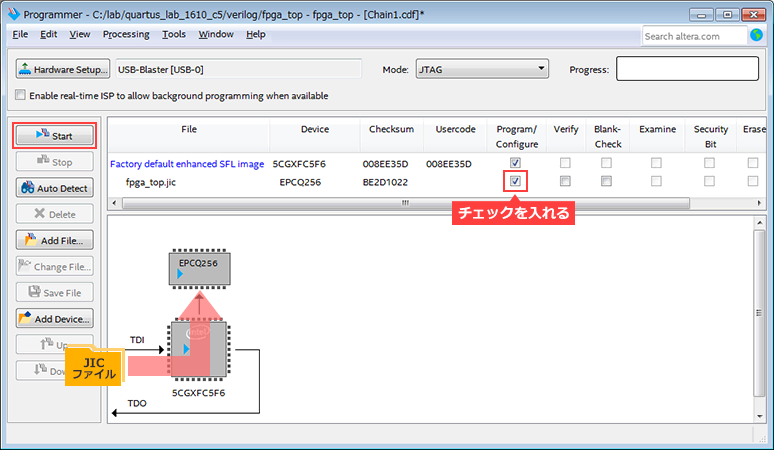

Programmerが起動したら、以下の設定を行います。

- ダウンロード・ケーブルを選択

- USB-Blaster を選択

- モードを選択

- JTAG を選択

- プログラミング・ファイルを指定

- Add File をクリックして、JIC ファイルを指定

下図のようになったら、Program/Configure にチェックを入れて、Start をクリックします。書き込みには少し時間が掛かるので、終わるまでお待ちください。

プログラミングが完了したら、再度、電源を入れ直してください。そうすると、新しい FPGA イメージがコンフィギュレーションされて、FPGA が動き出します。