ここでは、デジタル回路設計者が困ったこともあるだろうハザード信号、それがなぜ発生するかの簡単なメカニズムと、そのハザード信号がシステムに与える影響について簡単に説明します。

非同期信号を入力した際のシステムへ与える影響についてはこちらをご覧ください。

[RTL 設計ビギナー必見] 非同期信号を入力した際のシステムへ与える影響

同期設計と非同期設計の違いについてはこちらをご覧ください。

[RTL 設計ビギナー必見] 同期設計と非同期設計の違い

デジタル回路設計者を悩ませるモノ

電気的に正規化されたロジック回路は、カスタム LSI、スタンダード・セル、ASIC、FPGA や CPLD、古くは TTL と言ったいろんな実現手段で構築されてきました。アナログ信号に比べロジック信号は正規化されているので、考え方が非常にシンプルです。そのシンプルさが現在の文明を飛躍的に向上させました。自然界のほとんどの物理現象がデジタル化され、さらにはコンピュータ化される時代になって来たといっても過言ではありません。

多くの便利さが提供される中で、実際に半導体回路を使ってシステム化される段階では、マクロ的にはデジタル回路(ロジック回路)として正規化された考え方をすることができますが、ミクロ的にはアナログ信号となります。特に、最近の半導体デバイスは高速化され、ロジック回路として単純な “1” と “0” の世界だけで閉じて考えられなくなって来ています。例えば、ギガ・ヘルツ(GHz)帯の高速伝送や低消費電力化のために取り扱い信号の微弱化などがあげられます。

このように単純な “1” と “0” の世界だけで閉じられない世界に、古くから “ハザード” と呼ばれる期待値以外の信号が本来のロジック信号の中に含まれていて、ロジック回路設計者は度々も悩まされて来ました。

ハザード信号とは

1つ以上の入力が変化したとき、出力が正規の値と異なる値を出すような回路の誤動作をハザード(Hazard)と言います。

ハザードの種類

ハザードには、ダイナミック・ハザード(Dynamic Hazard)とスタティック・ハザード(Static Hazard)があります。

- ダイナミック・ハザードとは、1個以上の入力の変化によって出力が変化するとき、3回以上変化して過渡的な値の系列を発生させる現象を言います。

例えば、“1” から “0” に遷移する場合に: “1” → “0” → “1” → “0” と変化する場合です。また、“0” から“1” に変わる場合に: “0” → “1” → “0” → “1” と変わる場合です。

- スタティック・ハザードとは、1個以上の入力が変化したとき、同一値をとるべき出力が正しい値と異なる値を一時的に取ることを言います。このスタティック・ハザードには、2つのケースが有ります。

1 Hazard: “1” 出力が一時的に“0”” になる誤り

0 Hazard: “0” 出力が一時的に“1” になる誤り

スタティック・ハザードのメカニズム

ここではスタティック・ハザードについて説明します。

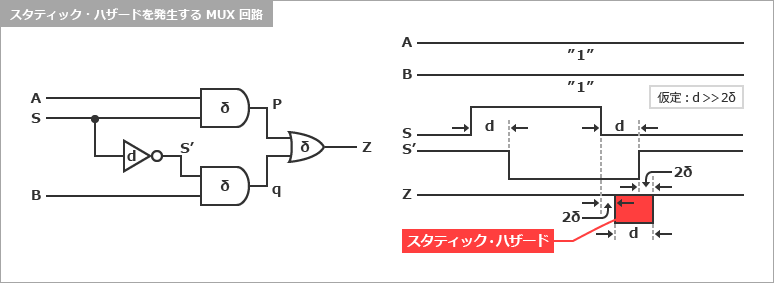

下図に良く使われる信号切換回路(MUX)を示します。

※上図の例では、説明を理解しやすくするために、切換信号用のインバータのディレイ(d)を他の AND-OR ゲートのディレイ(δ)よりも非常に大きいものとしています。

この例で考えると、例えば、入力 A と B が “1” のとき、切換信号 S を切換えても出力には何も発生しないはずですが、仮に S’ を作るインバータのディレイ(d)がゲートのディレイ(δ)に比べて十分に大きい場合、信号 S が変化しても S’ が変化するまでにはかなりの時間のずれが生じます。そうした場合に、S が “1” → “0” に変わって p 点出力が “0” になっても、S’ 信号はまだ “1” になっていませんので、結果として q 点出力も “0” のままです。したがって、最終出力 Z 点には “0” が出力されます。この負のパルス(ディレイ d に相当)がスタティック・ハザードです。このハザードは、複数の信号のタイミングのずれによって発生します。このタイミングのずれは、(後でも述べますが)一義的に決まるものではなく、色々な環境によって影響を受けます。今、この瞬間に発生していなくても、いつ何どきに姿を見せるか分かりません。そのため、明示的にその発生原因の抑制をした設計をする必要があります。

スタティック・ハザード信号の抑制

スタティック・ハザードが発生する原因は、2つ以上の入力の変化に時間差がある場合に発生します。つまりスタティック・ハザードを無くすためには、1個の入力のみが変化するようにすれば良くなります。一般的に、スタティック・ハザードを回避する方法として冗長回路の追加があります。この適切な冗長回路を探すためにカルノー図を使います。

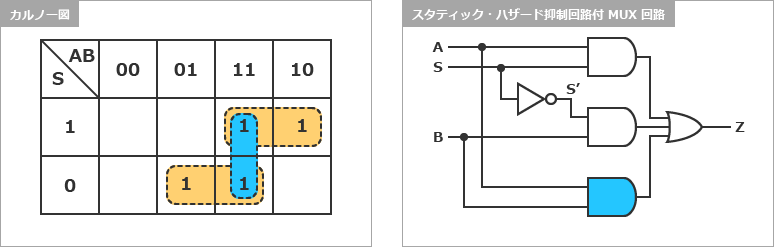

下左図にカルノー図、下右図に先ほどの図に冗長回路を付加してスタティック・ハザードを抑制した例を示します。

カルノー図の作り方は、X 軸と Y 軸に入力変数を書きます。先に述べたように、入力が1個のみの変化の場合はハザードを発生しませんので、それを調べるために、変数が1個だけ変化するように並べます。先の切換回路(MUX)であれば、変数は A, B, S の3変数ですので、X 軸に AB の2変数を1ビットの変化であるように “00” → “01” → “11” → “10” と並べ、Y 軸には S を “1” → “0” と並べます。続いて、各入力に対する出力 Z を表の中に埋めます。この例で言えば、入力切換信号 S が “1” の場合は入力 AB が “11” のときと “10” のとき、および S が “0” の場合は AB が “01” と “11” のときとなります。

上左図(カルノー図)で、切換信号 S の欄で “1” が横に2個並んだ項が正規出力項 AS と BS’ を示す必須項です。今、出力が “1” となる入力状態のうち、入力の値が1つだけ異なる隣り合った状態をみると、S が “1” の場合、B が変化しても AS が Z を “1” に定義し続け、S が “0” の場合は、A が変化してもBS’ が Z を “1” に定義し続けますのでハザードは生じません。しかし、S の変化については正規項に含まれていません。これがハザードを発生する原因です。そこで、AB 項(“11”)を追加すれば、S の変化に対しても、AB 項が Z を “1” に定義し続けますので、ハザードを除去することができます。この項は必須項ではないので、一般の論理合成では削除されますが、ハザードの防止と言う観点からすれば必要となります。したがって、ハザードを防止する目的で明示的に冗長機能をソースに記述する場合は、その個所を論理圧縮しないように設定することが必要です。

ハザード信号のシステムへの影響

正規化されたロジック信号は、実現された電子回路内で、目に見えない形で存在します。この信号は、計測器でも観測が困難な場合があります。特に、ロジック回路観測用に使われるロジック・アナライザでは観測が不可能です。オシロスコープなどの波形観測用の機材でもかなり高価なものを使用する必要があります。また、ハザード観測のためには知恵と熟練が必要となります。

夏場になったら不安定?

特に、始末が悪いのは、実験室や製造工場などの恵まれた環境(安定した電源環境、空調の効いた部屋など)で試験された装置は、大概にして安定動作してしまいます。“動作してしまう”と表現したのは、恵まれた環境内では、悪魔(ハザード)が出てこないことがほとんどです。実験室や工場での検査段階で問題が発生してくれれば、市場に出荷する前に対処できます。しかし、この悪魔(ハザード)は意地悪で、彼らが住み易いとされる不安定電源や高・低温などの悪い環境に行くとすぐに顔を出します。皆さんは、“夏場になったら機器が不安定になった”とか、“製造ロットが変わったら機器が不安定になった”等の経験はありませんか?この主たる原因がハザード(悪魔)です。

最新ロットは不安定?

このハザードは、環境の変化によって素子のタイミングが変化することに起因しています。特に、FPGA やCPLD の世界では、同一型名でありながら製造プロセスがどんどん進化することです。他の半導体ロジック素子では、一生同一製造プロセスが採用されるのが一般的ですが、FPGA や CPLD の世界では、歩留まり改善や高速化のためにプロセスの微細化が行われ、これによって素子の遅延が早まる傾向にあります。結果として、信号間のタイミングに差異が生じハザードを誘発します。特に、生涯ロットが大きく、永年にわたって繰り返し生産される機器では、“過去の製造ロットでは問題が発生しなかった” が、“最新ロットは不安定だ” というようなことが起こります。このような場合に陥りやすい問題解決のアプローチとして、“過去に正常動作していたから設計には問題無い”といって、設計レビューに目を向けないことがあります。このような場合は問題解決手法がその場しのぎとなり、後に同じ問題を引起す場合があります。

ハザード発生の原因と対応策

このタイミングのずれは、電源電圧の変動や装置が設置される環境での使用温度変化でも “ハザード” 発生の原因となりますが、それらの原因をまとめると、主として次の3つとなります。

- 電源電圧の変動

- 周囲温度の変動

- 製造プロセス変更

ハザードがシステムに与える影響は計り知れないことが多いですが、これらのシステム上における不安定要素を解決するためには、先に述べた “ハザード抑止策” を含めて以下の方法を採用することをお勧めします。

- クロック同期によるレジスタ回路でのハザード回避策

- 出力信号のレジスタ・ラッチ出力

- 冗長回路によるハザード抑止策

最後に

一般的には、ハザードの現象はシミュレーションや計測器でもほとんどの場合が発見できません。ですから、「電子回路で生成される回路はハザードを常に発生するもの」として、「発生しても問題無い回路」構成にすることが大切です。そのためにはやはり、同期設計をすることが重要なポイントになるのです。

おすすめ記事/資料はこちら

[RTL 設計ビギナー必見] 同期設計と非同期設計の違い

[RTL 設計ビギナー必見] 非同期信号を入力した際のシステムへ与える影響

Beryll の FPGA でクロック同期によるLチカ![#1/3]

FPGA/CPLD の動作特性について