この内容は、FPGA や CPLD の正しい設計手法や知識を整理し設計者に深く理解してもらうことで、インテル のデバイスが使いやすく信頼度も高い製品であることを知ってもらうのと同時に、デバイス内のデザインに不安定要素を限りなく軽減してもらうことを目的にしています。

FPGAや CPLD の開発において信頼性の高い(つまり動作する)システムを構築するには、ポイントとなるデザイン・テクニックの基本を学びデバイスにインプリメントすることが重要ですが、その予備知識として FPGA や CPLD の動作特性について理解することも少なからず重要です。

FPGA や CPLD が正しく動作することを阻害する要素は、主に以下があります。

- 電圧変動

- 周囲温度

- ロットのバラツキ、プロセスの進化

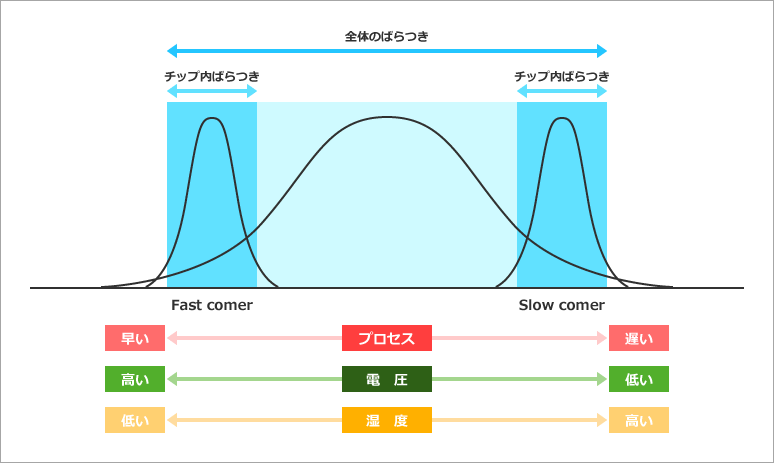

これらの外部要因は極一般的に考えられる要素で、これらが変動すると FPGA や CPLD のタイミング(遅延)も変動します。例えば、電圧が高いほど、温度が低いほど、遅延は小さくなり高速で動作します。多くの動作不良の原因は、このタイミングのバラツキによって起こります。『デバイスを交換したら動作した。』『デバイスを冷やしたら動作した。』と言ったことを良く耳にします。これらは、ほとんどの場合がタイミングの問題から来ています。ここで、意外と気が付かない問題があります。短期的にはデバイスのロットのバラツキが考えられ、また、長期的にはプロセスの進化による遅延値の変化が考えられます。

一方、FPGA や CPLD の遅延値は、最も高速の動作条件(Fast)と最も低速の動作条件(Slow)の少なくとも2つの動作条件(65nm プロセス以下の FPGA は3つの条件、28nm プロセス以下の FPGA は4つの条件)の下で定義されていて、開発ソフトウェアは動作条件の数だけライブラリ(タイミング・モデル)を持っています。デバイスのロットが変わったり、プロセス・チェンジを行っても、規定された最速値および最悪値のタイミング・モデルに違反しない限り、そのデバイスは正常なデバイス(良品)となります。

これらのことをあらかじめ良く理解した上で設計を行わないと、思わぬところで痛い目にあいます。デバイス・メーカーがいくら良品と言ってもシステムが動作しなくては元も子もありません。そこで、デバイス・メーカーから出荷されてくる良品(あくまでも、スペック上の)の考え方を整理しておきます。

製造ロット

一般的に、各デバイスはいくつかのスピード・グレードをラインナップとして揃えています。例えば、6品、7品、8品と言った具合です。これらのスピード・グレードは個別にタイミング・モデルを持ちますが、より遅いデバイスはより早いデバイスを含んでいる場合があります。つまり、スピード・グレード8のデバイスは、スピード・グレード7の性能をも含んでいる場合があると言うことです。言い換えると、スピード・グレード8のデバイスは、スピード・グレード7とスピード・グレード8の性能を持つ可能性があります。このことから、FPGA や CPLD の設計時に曖昧さがあると、タイミングのバラツキが原因で時として誤動作を引き起こすことになります。

プロセス・チェンジ

プロセス・チェンジを行った場合、製造ロットの問題と同様に、旧来品と同じタイミング・モデルが使われています。しかしながら、プロセス・チェンジによって遅延値は高速化の傾向を持ちます。結果として、新しいプロセス品を使用すると、『ノイズで動かない。』、『グリッチがでる。』、『グラウンド・バウンスによりカウンタが誤動作する。』と言ったことになります。

タイミング・モデル

インテル が推奨する動作条件は、以下を指します。

- 使用電圧範囲(V)

- 使用周囲温度範囲(T)

- ロットのバラツキ(プロセス・チェンジを含む)(P)

この PVT 条件下で、開発ソフトウェアのタイミング・モデルが用意されています。 インテル の FPGA/CPLD をタイミング検証(TimeQuest によるタイミング解析や EDA シミュレータツールによるタイミング・シミュレーション)をする場合に使用されるタイミング・モデルは、最も高速の動作条件である Fast モデルと、最も低速の動作条件である Slow モデルがありますが、回路のすべてのパスがそれらの最悪値だけで解析しても実は不十分です。ロットのバラツキも考慮する必要があります。回路のすべての部分が最も遅く動作するデバイスよりも、ロットのばらつきにより、ある部分だけが少しだけ速く動作するデバイスの方が、タイミングが厳しくなることがあるからです。この解析を Minimum/Maximum 解析と言い、Quartus® Prime ではこれらを考慮した解析を行います。

Quartus® Prime が算出した結果は、クロック同期設計においてユーザーの設計要求を満たしている値と言えます。例えば、TimeQuest から得られた Slow モデルにおける動作周波数(Fmax)は、そのデバイスの最も遅いパスの最低動作周波数を示すものなので、その周波数以下で使用されるシステムの動作周波数は確保できるわけです。同様にして、セットアップ/ホールド・タイムの算出結果値をシステム上で確保することにより、インテル の推奨条件下で動作するようになります。

このような理由から、インテル の FPGA や CPLD を使用する場合は、コンパイルが完了した後(配置配線後)にタイミング解析による綿密な動作検証を行うことをお勧めします。

以上、FPGA/CPLD 設計における予備知識でした。

おすすめ記事/資料はこちら

[RTL 設計ビギナー必見] 同期設計と非同期設計の違い

[RTL 設計ビギナー必見] 非同期信号を入力した際のシステムへ与える影響