極当たり前に設計をして、極当たり前に評価をして装置を出荷したにも係わらず、他の装置と接続して動作をさせていたら、『時々誤動作する』とか、夏場の暑い時に『誤動作する』とか言ったことを聞くことがあります。これらの原因は、タイミングによる影響がほとんどで、システムに同期をしていない入力信号(非同期入力信号)や回路上で発生するハザードに起因しています。

そこで今回は、システムに同期していない入力信号がシステムに与える影響とその解決方法について説明します。

ハザードがシステムに与える影響に関してはこちらをご覧ください。

[RTL 設計ビギナー必見] ハザード信号のシステムへの影響

非同期入力

非同期入力の持つ意味

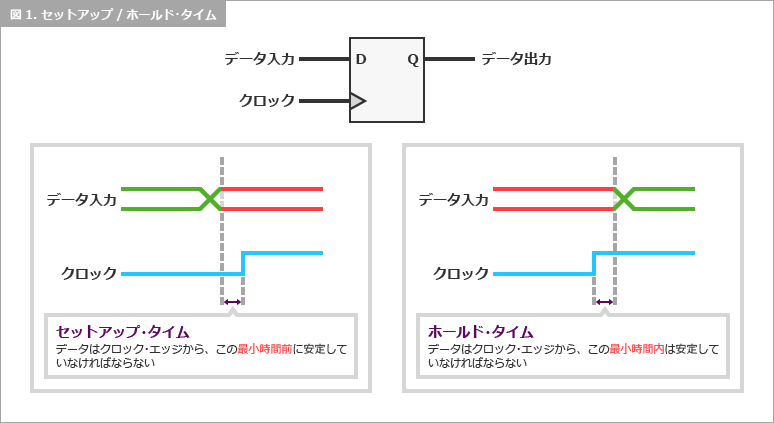

FPGA において、フリップフロップの入力信号とクロック信号との間には、安定して動作するための要求条件としてセットアップ・タイム(tSU)とホールド・タイム(tH)の規定があります。デジタル論理回路設計者はこれらの規定を厳守しなければなりません。この要求条件は、FPGA メーカーが提供する開発ソフトウェアの中に格納されています。図1にセットアップ・タイムとホールド・タイムの概念図を示します。

このセットアップ・タイム/ホールド・タイムの規定に違反した場合、”メタステーブル“ と呼ばれる一時的に不安定な状態やシステム上定義された状態とは異なる状態になる可能性があります。このことが要因でシステムの信頼性に大きく影響を及ぼします。異なる機器間でデータを授受するような場合は、非同期システムとなり、受け取る信号とシステム・クロック間では、このセットアップ・タイムとホールド・タイムの規定を保証することができません。これらの装置間での信号の授受時には信号の同期化が必要となり、この同期化がおこなわれない場合メタステーブル状態(メタスタビリティー)を引き起こしやすくなります。(メタステーブルは、必ず発生するのではありません。また、発生しても、その時間は通常は ns オーダーですから、問題にならないで済むこともあります。しかし極めて低い確率ではありますが、メタステーブルの不安定期間が長時間になることがあります。)

メタステーブルとは

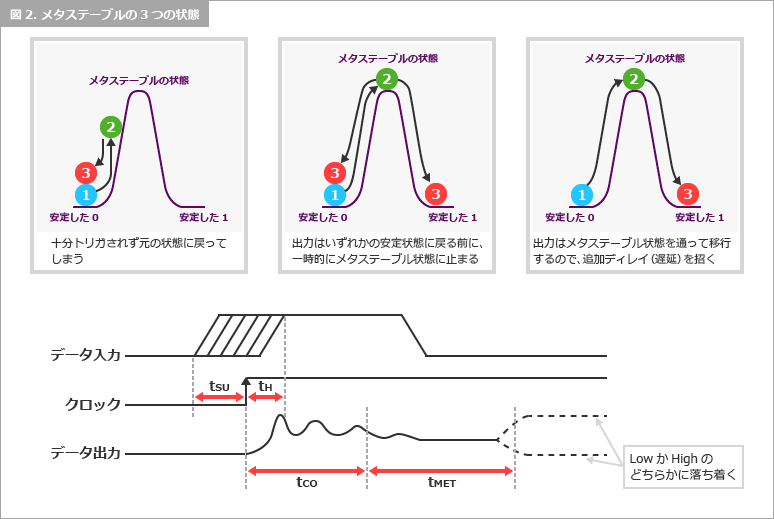

メタステーブルとは、本来規定されているクロックからの出力時間 tCO を超えても出力状態が安定しない状態を言います。安定するまでに必要な時間 tMET は、周囲条件やデバイスの製造技術に依存します。

レジスタの動作は、図2のようにボールが摩擦の無いひとつの山を移動する状態に例えて表すことができます。山の両側は安定した状態(High または Low)を表していて、山の頂上がメタステーブルの状態を表しています。

フリップフロップへの入力が規定のセットアップ・タイム tSU とホールド・タイム tHの最小値を満足している場合は、出力が一方の安定したステートからもう一方の安定したステートに(High から Low、または Low から High に)追加遅延無しで変化します。

一方、フリップフロップへのデータ入力が規定されているセットアップ・タイムまたはホールド・タイムの規定に違反している場合、フリップフロップが完全な形でトリガされず、出力が規定された時間内で2つの安定したステートのいずれかにすぐに遷移しなくなる可能性があります。この不適切なトリガーは出力にグリッチを発生させたり、一時的に出力が High と Low の間のメタステーブル状態になり、出力が安定したステートに戻るまでの時間が長くなる原因になり、いずれの条件でもクロックの遷移から出力が安定するまでの時間が増加することになります。

メタスタビリティーは、必ずしもシステムの性能の予測を不可能にする要因とはなりません。フリップフロップが安定したステートに戻るまでの待ち時間を十分に許容できるようになっていれば、システム性能に影響を及ぼすことはなく、フリップフロップの出力が一時的に不定となった場合でも、この信号は実際に使用される前に安定したステートに戻ることができます。このため、信号があらかじめ規定された値にセトリング(settling)するまでの追加時間 tMET を許容させることによって、規定されていない値の信号がシステムの他の部分に伝播することを避けることができます。

メタスタビリティーのシステムへの影響

先にも述べたとおり、非同期入力はシステムに悪影響を及ぼします。基本的に、システム内のフリップフロップが一度メタステーブルの状態に陥ると、単に不安定となるばかりでなく最悪の場合はシステム・ハングアップの状態となります。もはや電源を切る以外に復帰の方法はありません。このように、メタスタビリティーの状態は、システム上からは人為的に状態定義ができません。半導体の物性のみが状態を制御できます。“神のみぞ知る”です。

特に陥りやすい例は、同一クロック系システムの場合です。例えば、相互の機器が 50MHz のマスター・オシレーターで作動している機器同士での信号の授受です。このように公称同一周波数であっても、2つのマスター・オシレーターには周波数偏差や温度係数なども異なっており、微妙に周波数は変動します。結果として、信号が相互に非同期となります。ご注意ください。

メタスタビリティーの回避策

メタスタビリティーの影響を減らすための最も一般的な方法は、次の2つの方法があります。

・ 同期用フリップフロップを使用する

・ FIFO ロジックを使用する

これらを簡単に説明します。

同期用フリップフロップの使用

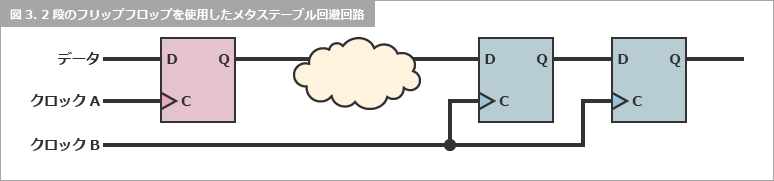

一般的なメタステーブル対策は、非同期入力信号とシステム・クロックとを同期化するために、図3のように後段の受信側クロック・ドメインに同期化フリップフロップを複数挿入します。ただし、挿入されるフリップフロップの数によってシステムの信頼性は格段に向上しますが、挿入したフリップフロップの段数分だけシステムのレイテンシーが増しますので、全体システムでのパフォーマンスの低下を引き起こす可能性があります。

非同期入力信号の繰り返し周波数とシステム・クロックの周波数との差が無視できる程にある場合は1段程度で十分ですが、2つの周波数が隣接している場合は数段入れる場合もあります。何段挿入したら良いかの目安は、Quartus® Prime の TimeQuest タイミング・アナライザー機能で MTBF(平均故障間隔)を確認すれば分かります。なお、メタステーブル期間が短くなるように受信側のFF間は短くすることをお勧めします。

図3において、同期化フリップフロップ(前段のフリップロップ)がメタステーブル出力を生成しても、その後、メタステーブル信号は2番目のフリップフロップがトリガーされる前に安定する可能性が出てきます。この方法は、2番目のフリップフロップが不安定出力をトリガーしないと言う保証は有りませんが、そのデータが回路の他の部分に到達する前に有効な状態になる確率は向上します。このようにして、システムに要求される信頼性から挿入するフリップフロップの段数を決定して行きます。

いずれにしても、1本の非同期入力は複数のフリップフロップに供給しないでください。1本の非同期入力を複数のフリップフロップに供給すると、メタステーブルの状態によるシステム・エラーの確率が増加します。なぜならば、非同期入力信号が複数のフリップフロップに入力された場合、接続されたフリップフロップ毎に異なる状態になる可能性があり、システム上一義的な状態定義ができなくなります。このような場合は、同期化フリップフロップを入れ、システム上一義的な状態定義をした後の出力を後段フリップフロップやロジックに供給してください。

FIFO ロジックの使用

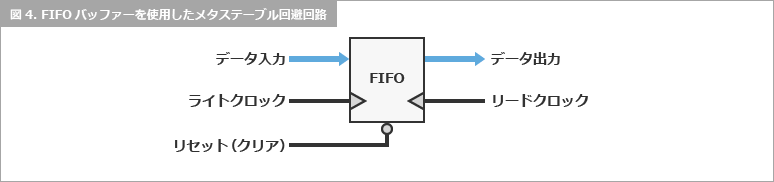

データ・バスなどの複数ビットの入力を同時に同期化するためには、FIFO(First-In First-Out)ロジックを使用します。FIFO ロジックは、シンクロナイザーを使用して2つのクロック間で制御信号を伝送するもので、データはデュアルポートメモリーに対してリード/ライトされます。図4にその概略図を示します。

最後に

システムに非同期の信号が入力されると、メタステーブルと呼ばれるシステム上予測不可能な状態に陥ります。最悪の場合、システムがハングアップし電源を切断しないと復帰しない事態を引き起こす場合があります。システム全体で同期化されていない機器間での信号の授受の場合には、メタステーブル状態を引き起こす可能性があります。したがって、システム全体の信号系統を精査し、同期化システムを構築し、不安定要素を取り除くことをお勧めします。

おすすめ記事/資料はこちら

[RTL 設計ビギナー必見] 同期設計と非同期設計の違い

[RTL 設計ビギナー必見] ハザード信号のシステムへの影響

FPGA/CPLD の動作特性について