こんにちは。

マクニカでインテル® FPGA 製品の技術サポートをしている インテル・F・ハナコ です。

以前ご紹介している「FPGAではじめてのLチカ!」のデザインは、クロック入力信号を必要としない回路でしたが、今回はボードに搭載されたオシレーター(クロック)を使って動作する HDL デザインを作り、Lチカします。

FPGA 設計が初めてのユーザー向けに、

デジタル論理回路には重要なクロック同期設計の話やグローバル・クロックの話、Cyclone® V シリーズをはじめとする近年の FPGA で可能なクロック・セレクタ(正式にはクロック・コントロール・ブロック)を使用したデザインついてもお話します。

また、デザインの論理合成に関しても簡単に触れてみたいと思います。ピン設定に関しても、ちょっとだけ FPGA の特徴を説明しながら設定していきます。

今回Lチカで使用するボードはコレ!Mpression 製 Beryll (ベリル)です。

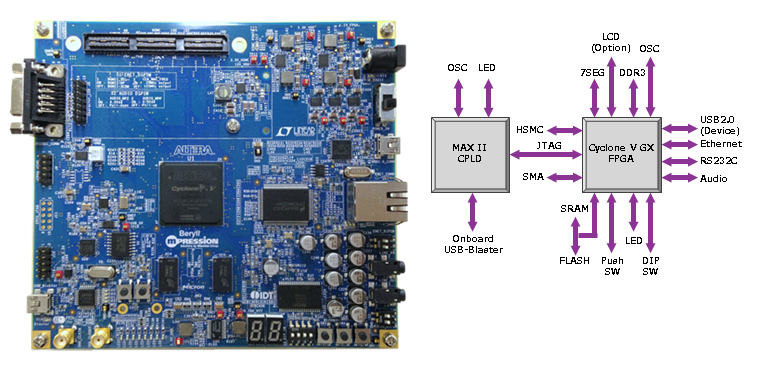

Beryll は、インテル® FPGA のローコスト製品に位置づけられる Cyclone® V GX (サイクロン・ファイブ・ジーエックス) を搭載した FPGA 開発ボードです。

ここでは Beryll ボードおよび Cyclone® V FPGA を使用していますが、他のインテル® FPGA の開発にも活用できる内容も盛り込まれているので、是非参考にしてください。今回は盛りだくさんです!

Beryll の特徴

- Cyclone® V GX FPGA を使用して、柔軟にユーザー・ロジックの開発・検証が可能

- HSMC(High-speed Mezzanine Connector)が搭載されているので、システム拡張が可能

- On-Board USB-Blaster™ 回路が搭載されているので、USB-miniUSB ケーブルを接続することでFPGA のコンフィギュレーション回路をダウンロード可能(つまり USB-Blaster™ は不要です。)

- Cyclone® V FPGA に搭載された HMC (ハード・メモリ・コントローラ) をマイクロン社のDDR3 SDRAM と共に評価可能

その他、Beryll の概要はコチラをご覧ください。

必要なもの

- Quartus® Prime ライト・エディション(有償のプロ・エディション、スタンダード・エディションでもOK)

- USB-miniUSB ケーブル、電源アダプタ(Beryll ボードに付属)

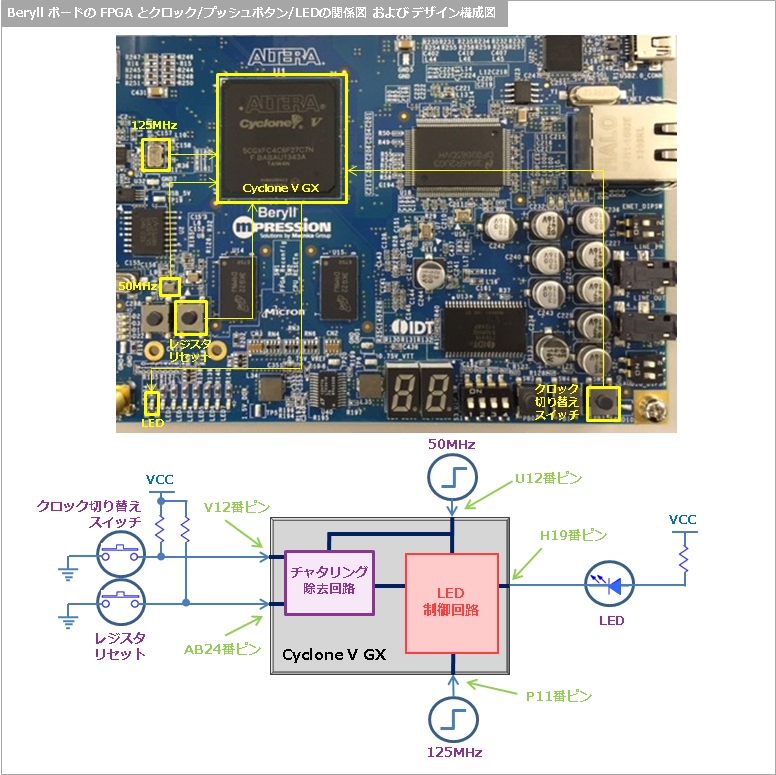

基板上のFPGA/クロック/プッシュボタン/LED とデザイン構成はこんな感じ

今回のLチカのデザイン仕様は、外部から入力したクロックで FPGA 内部のフリップフロップを動かし LED を点滅させます。

Beryll の FPGA には、周波数の異なるオシレーター(27MHz / 33MHz / 50MHz / 125MHz)が供給されていて、今回のデモではこのうち2つのクロックを使います。

FPGA 内部に供給するクロックをプッシュボタンで切り替えながらフリップフロップを動作させるデザインにします。(つまり、プッシュボタンの ON/OFF で点滅スピードが変わります。

「FPGA ではじめてのLチカ!」のデザインは、プッシュボタンに対してチャタリングを気にしていませんでした。

LED のON/OFFがチャタリングでパタついても目視ではわからないことと、FPGA 設計の初心者ユーザーさんにQuartus® Prime の設計フローを知ってもらう内容に重点をおいた回だったので、省略しました。

…が!でも実際はとっても大切です。チャタリングの除去方法は様々で、コレと言う決まりはありません。

FPGA に信号を入力する前にチャタリングを除去する回路を基板上に実装する方法もありますが、今回はチャタリングを除去する論理回路を設計して FPGA 内部に実装します。

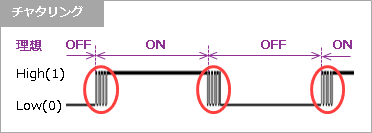

チャタリングとは?

トグルスイッチや押しボタン式スイッチなどが ON/OFF 直後にスイッチの接点がバウンドして ON/OFF を短時間に何度か繰り返してから ON や OFF(接触状態)になる現象のことです。

チャタリングの発生時間はスイッチにより数ms~数十ms程度と異なりますが、数ns単位で動作する FPGA にとっては十分長く、FPGAの入力端子に対して断続的な ON/OFF 状態を作り確実に認識します。つまり、1回しかスイッチを操作していないはずなのに複数回スイッチを操作したように見えてしまい、意図しない挙動を引き起こします。

今回のデザインは、ロジアナやオシロでLチカ動作を観測するのではなく人間が見てわかる速さで LED を点滅させるために、FPGA からの High/Low 出力の遷移周期を下げなければなりません。

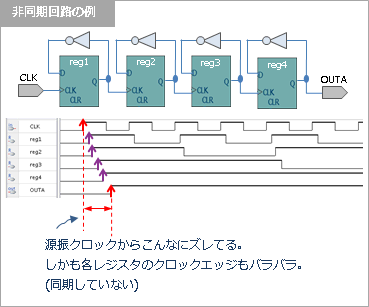

安易にクロックの周波数を下げる設計をするなら、フリップフロップで分周した出力を次のフリップフロップのクロックとして再利用し、さらにそのフリップフロップも分周させることを何回も繰り返せば実現できそうですが、それだと各フリップフロップは異なるクロック・エッジで動作することになって、FPGA 内部の動作にバラツキが起きます。これがいわゆる非同期設計です。非同期設計は、フリップフロップの伝播遅延が累積するため、後段の回路に行くほど遅延の影響が出ます。そのため FPGA の内部動作だけでなく、FPGA の出力信号と周辺デバイスとのタイミングも取り難くなり、システムとして考えたときにボード上あるいはボード間の同期も取りづらくなります。

FPGA の設計基本は “クロック同期設計” です。これはインテル® FPGA に限ったことではなく、どの FPGA メーカーも推奨しています。論理的に回路を設計しても、実際デバイス内では配置配線による遅延が発生します。そのため同一クロックのエッジに合わせて内部レジスタをトグルさせることは、非常に重要なことです。

FPGA の論理回路設計が初めてのユーザーさんは、是非下記ページを読んでください。デジタル論理回路を設計する上で重要な基本中の基本が書かれています。

[RTL 設計ビギナー必見] 同期設計と非同期設計の違い

Quartus® Prime で設計スタート!

FPGA/CPLD の一般的な開発フロー に基づいて作業を進めましょう。

1. 論理回路を設計する

プロジェクトを作り、HDL言語で以下の論理回路を書きます。

- チャタリング除去回路

- LED 制御回路

- これらを接続するトップ回路

チャタリング除去回路はインターネット上に考え方や設計例がたくさん紹介されていますので、ここでの具体的な記述や解説は省きます。(クロック同期回路を意識して設計します。)

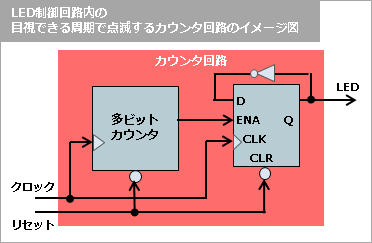

LED 制御回路は、目視できる速さで High/Low(点滅)を繰り返す回路にします。こちらも全てのフリップフロップをクロックに同期させた構成にします。

今回、FPGA への入力クロックは50MHzと125MHzの2種類です。どちらのクロックで動作させても「目視できるレベル」まで点滅周期を下げるため、イメージ図の多ビットカウンタはザックリと26bitカウンタで構成しました。

もし、点滅周期を「1秒」などと決めるのであれば、源振の周波数から算出してカウンタのビット数やカウンタをリセットする条件を求めてください。今回は、50MHzのときも125MHzの時も同じカウンタ回路を使用します。

VHDL 言語で書いてみると、例えばこんな感じ。

| library ieee; use ieee.std_logic_1164.all; use ieee.std_logic_unsigned.all; entity Lchica_counter is port( CLK: in std_logic; ACLR: in std_logic; LED : outstd_logic ); end Lchica_counter; architecture rtl of Lchica_counter is signal pls_cnt : std_logic_vector (25 downto 0):=(others => '0'); signal pls : std_logic :='0'; signal led_reg : std_logic :='0'; begin process (CLK, ACLR) begin if (ACLR = '0') then pls_cnt <= (others => '0'); led_reg <= '0'; elsif (clk'event and clk = '1') then if (pls_cnt = X"2AAAAAA") then pls_cnt <= (others => '0'); pls <= '1'; else pls_cnt <= pls_cnt + '1'; pls <= '0'; end if; if (pls = '1') then led_reg <= not led_reg; end if; end if; end process; LED <= led_reg; end rtl; |

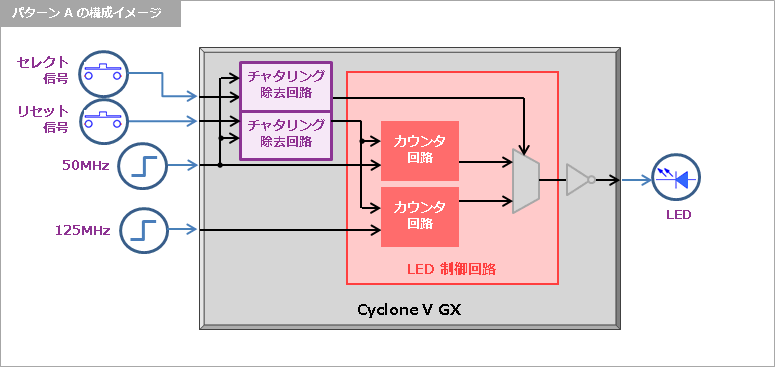

今回のデモは、50MHz動作回路と125MHz動作回路をプッシュボタンで切り替える仕様です。どのように論理回路を構成するかはユーザーの自由なのですが、その回路構成が FPGA で使用(消費)されるロジック数や動作スピードなど Quartus Prime のコンパイル結果に大きく影響します。

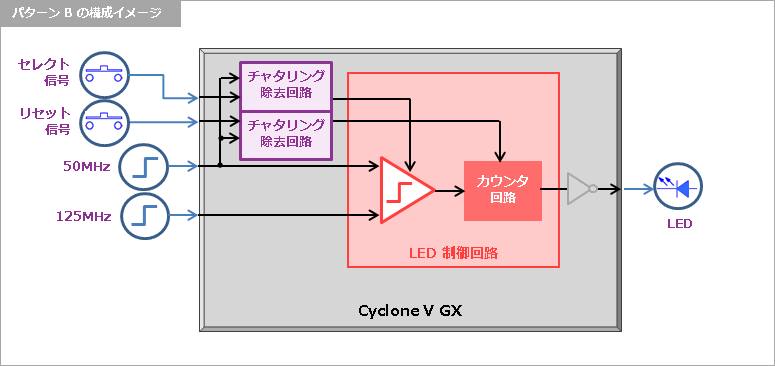

ここではこのデモを実現できる2つの構成例(下図)で、その違いを解説します。

パターンA(左図)は、点滅する周期を下げるカウンタ回路を25MHz用と125MHz用それぞれに用意し、最終段でセレクトして出力する構成です。もちろんクロック同期設計です。

パターンB(右図)は、点滅する周期を下げるカウンタ回路はひとつで、その前段で入力するクロックをセレクトさせる構成です。もちろんこちらもクロック同期設計です。

FPGA の場合、外部から入力されたクロックを内部で分周やセレクトするなどのロジックを介してしまうと、通常は グローバル・クロック ではなくなってしまいます。

(クローバル・クロックについてはこちらをご覧ください。)

このパターン B のクロック構成を見てみると、クロックをセレクトしている、つまり組み合わせ回路を経由しています。これはグローバル・クロックの定義に反しますから、後段のカウンタ回路内のフリップフロップはグローバル・クロックではないクロック信号でドライブされて各フリップフロップの同期が図りづらくなります。

でも安心してください!ALTCLKCTRL を使ってますよ!(右図)

ALTCLKCTRL は、グローバル専用ラインに接続できるクロック・コントロール・ブロックに配置させるためのメガファンクション(無償のベンダー・ライブラリ。IP みたいなもの。)で、クロック信号のマルチプレクサ(セレクタ)機能やクロック・イネーブル機能を持っています。コレを使うことで、50MHzと125MHzをマルチプレクスしても、後段のフロップフロップのクロックはグローバル・クロックとして扱われます。

ALTCLKCTRL は Cyclone® V GX をサポートしているので、早速 Quartus® Prime の IP Catalog(Tools メニュー)で作成しましょう!

Beryll の FPGA でクロック同期によるLチカ![#2/3] へ続く

グローバル・クロックとは?

FPGA にはグローバル・クロックと呼ばれるクロック専用ラインが配線されています。このクロック専用ラインは、FPGA 全体に対してクロック・スキュー(すべてのフリップフロップに到達するクロックの時刻差のこと。)が極めて小さく設計されていて、この専用ラインをクロックとして利用することで、各フリップフロップの同期が図れ、タイミング調整やタイミング解析などもしやすくなります。また、多くのフリップフロップを一つのクロックでドライブするとクロック信号が高ファンアウトになるため配線リソースを多く消費しますが、このグローバル専用ラインを使用すると、通常の配線リソースを消費することなくフリップフロップをドライブでき、配線リソースをデータ転送に優先的に使用できるため、FPGA 全体のパフォーマンスを向上させることも可能です。

グローバル専用ラインを使用するには、デバイスで決められた専用ピンにクロックを割り当てるか、Quartus Prime においてクロック信号に対してロジック・オプションを適用させることで可能です。また PLL(phase lock loop)で生成したクロック出力は、自動的にグローバル専用ラインに接続されます。いずれのグローバル・クロック信号も、組み合わせ回路の入力信号に用いたりフリップフロップのクロックポート以外に接続したりすると、グローバル専用ラインから外されます(通常の I/O 配線へ移動される)。

グローバルラインの種類や本数は、ターゲット・デバイスのファミリにより異なりますので、デバイス・ハンドブックをご覧ください。(今日はこのくらいにしておきます。)

Beryll の FPGA でクロック同期によるLチカ!シリーズ

Beryll の FPGA でクロック同期によるLチカ![#1/3]

Beryll の FPGA でクロック同期によるLチカ![#2/3]

Beryll の FPGA でクロック同期によるLチカ![#3/3]