この「Quartus® ガイド」シリーズは、インテル® Quartus® Prime 開発ソフトウェアをご利用になるユーザ向けの資料です。

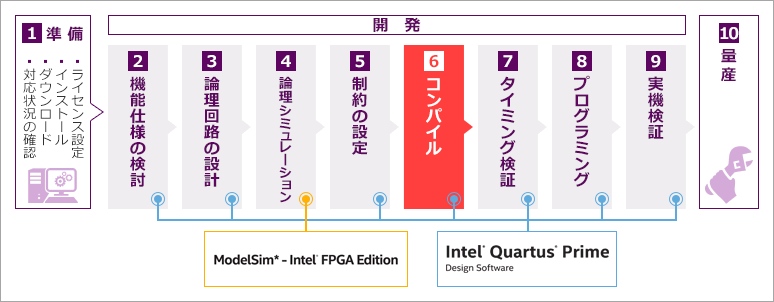

FPGA / CPLD の開発フローについては、こちら を参照してください。

説明

この資料は、FPGA / CPLD 開発の『6. コンパイル』フェーズで参考になります。

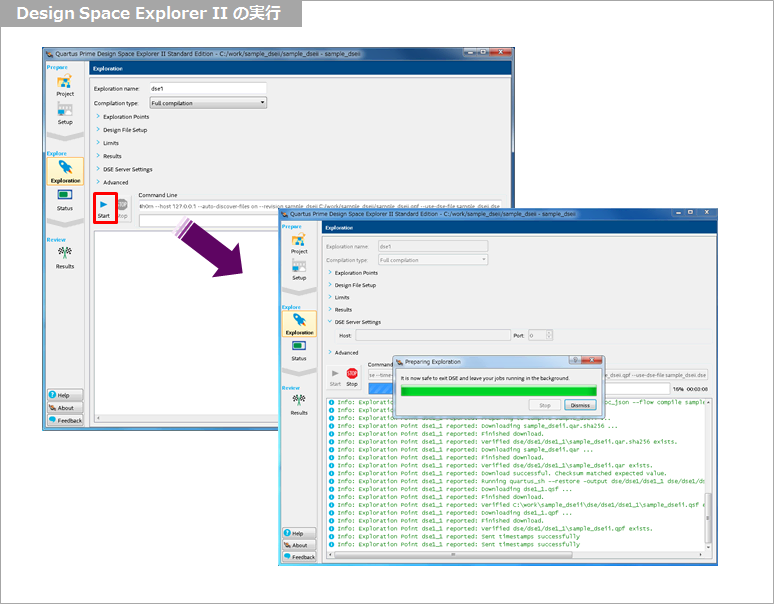

Design Space Explore II (DSE II)とは、Quartus® Prime の最適化設定を変更しながら複数回コンパイルを実行するという手順を自動で行うことができるツールです。DSE II を使用することによって、効率的にデザイン最適化を図ることができます。

この資料では、DSE II を実行する際の設定や実行後のレポート確認方法について紹介します。