こんにちは。

マクニカで インテル® FPGA 製品の技術サポートをしている インテル・F・ハナコ です。

インテル FPGA を開発中、ユーザーによっては Quartus® Prime のコンパイル実行を繰り返さなければならない場面があります。

コンパイルを何度も実行することへの一番のストレスは、やはり “コンパイル実行中の待ち時間” ではないでしょうか。

今回はそんなストレスから解放してくれる コンパイル時間を短縮させる方法 をご紹介します。

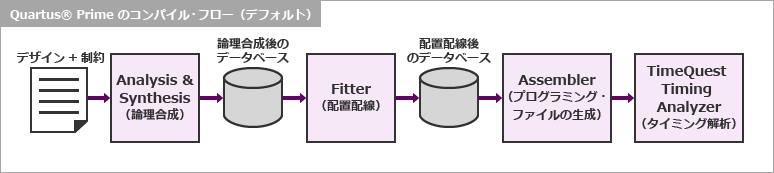

通常のコンパイル・フロー

下図は、通常 Quartus® Prime が行うコンパイル・フローを示したものです。

主なプロセスは以下の4工程です。このうち、Analysis & Synthesis(論理合成)と Fitter(配置配線)がコンパイル実行時間の大半を占めます。

つまり、この工程の処理時間を短縮することが、コンパイルの総時間を短縮することにつながります。

コンパイル時間を短縮させる方法はこれだ!

Quartus® Prime には、主に以下3つのコンパイル・メソッドがあります。

いずれもコンパイルが完了したプロジェクトに対して、その後修正を加え 再コンパイルを実施したときに効果を発揮します。

1. スマート・コンパイル(Smart Compilation)

2. ラピッド・リコンパイル(Rapid Recompile)

3. インクリメンタル・コンパイル(Incremental Compilation)

これらのコンパイル時間の短縮効果は、(小)1 < 2 < 3(大) です。

ここでは、その中でも簡単に使える スマート・コンパイル機能 と ラピッド・リコンパイル機能 を取り上げます。

ハナコのつぶやき

3つ目の “インクリメンタル・コンパイル” は一番効果的ですが、ややテクニックを要します。そのため別のページでご案内します。下記をご覧ください。

⇒ FPGA デザインの一部だけを再コンパイルする方法

⇒ インクリメンタル・コンパイルを使ってみよう

これら機能の特徴は?

スマート・コンパイル と ラピッド・リコンパイルの特徴をざっくりと下表に示します。

| スマート・コンパイル | ラピッド・リコンパイル | |

| 対象デバイス | Lite Edition および Standard Edition で サポートされているデバイス (Arria® 10, MAX® 10 を除く) |

Stratix® 10, Stratix® V, Arria® 10, Arria® V, Cyclone® 10 GX, Cyclone® V |

| 対応する Quartus® Primeの エディション |

Lite Edition Standard Edition |

Standard Edition(Arria® 10 を除く) Pro Edition (ver.20.3 以降では非推奨) |

| 特徴 | 再実行の必要ないコンパイル項目(例えば、Analysis & Synthesis、Fitter など)をコンパイラーが自動で判断し、その工程をスキップする機能。デザイン全体が適用の対象。 | 一度論理合成と配置配線を終えた結果の情報を再利用して、小規模な設計変更を高速にコンパイル処理できるようにする機能。デザイン全体が適用の対象。 |

| メリット | 操作が簡単! 工程がスキップされるので、コンパイル時間が短縮できる。 |

操作が簡単! 前回のコンパイル結果を再利用するので、必要な部分のみを論理合成および配置配線する。デザイン変更が少ない場合、コンパイル時間を削減することができる。 |

| デメリット | デザインを一部変更すると、前回の処理結果を再適用せず、(変更のない部分も含め)デザイン全体が再コンパイル(Analysis & Synthesis から再実行)される。 | 対象のデバイスが限定されている。 Lite Edition では実行できない。 |

各コンパイルの実行フロー例

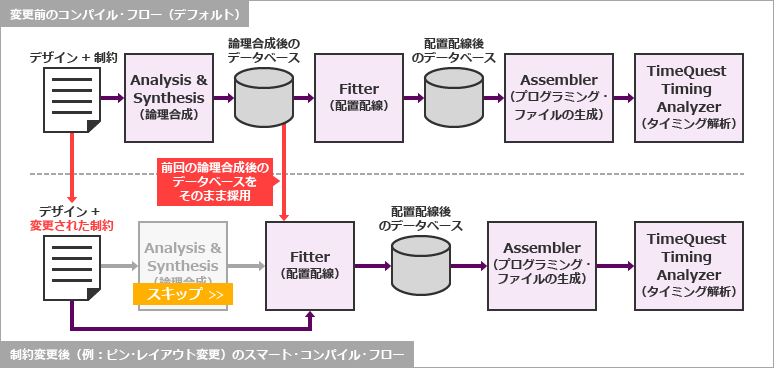

スマート・コンパイルの場合

例えば、(事前にスマート・コンパイルのオプションは適用済みの状態で)既にコンパイルが完了した後に

- ピンレイアウトを変更した

- デバイスの型番が変更になった(ただしデバイス・ファミリーは同一)

- (タイミングがメットできていないなどの理由で) 内部配置に影響するオプションを設定した

このようなときにスマート・コンパイルが適用されると、コンパイラーは下図の処理動作になります。

(※ Stratix® V, Arria® V, Cyclone® V の場合はラピッド・リコンパイルの活用を推奨します。)

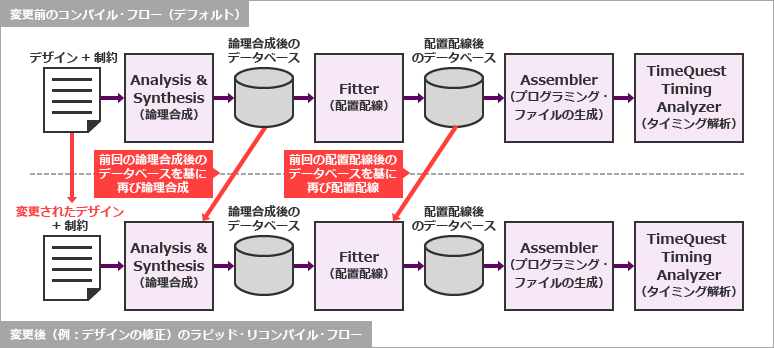

ラピッド・リコンパイルの場合

[Stratix® V, Arria® V, Cyclone® V をターゲットにしたプロジェクトが対象]

例えば、既にコンパイルが完了した後に

- 小規模なデザイン修正があった(例: レジスタの追加)

- 新たに機能モジュールが追加された

- ピンレイアウトを変更した

- デバイスの型番が変更になった(ただしデバイス・ファミリーは同一)

- (タイミングがメットできていないなどの理由で) 内部配置に影響するオプションを設定した

- SignalTap® II ロジック・アナライザーを追加した、あるいはそのデバッグ条件を変更した

このようなときにラピッド・リコンパイルが適用できます。

下図は、デザインが修正された場合にラピッド・リコンパイルを適用した際の、コンパイラーの処理動作を表したものです。

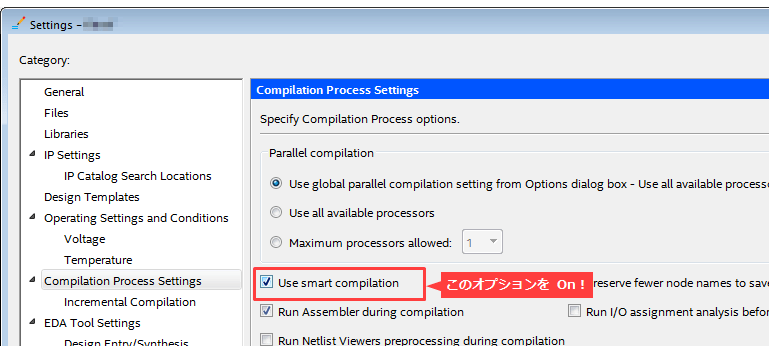

その実行方法は?(スマート・コンパイル)

ものすごく簡単です!!

まず 初回コンパイルの前に、オプションを設定します。

Assignments メニュー > Settings > Compilation Process Settings カテゴリーを選択し、Use smart compilation オプション = On!

その後、Processing メニュー > Start Compilation でコンパイルをスタートします。

このときに実行されるコンパイルは、まだスマート・コンパイルではありません。

この回 以降の再コンパイルをスマート・コンパイルで実行させるために、データベースを保存しながらコンパイルが行われます。(そのため若干処理時間がかかります。)

その後、レイアウト変更があったので再コンパイルが必要になりました。

Pin Planner でレイアウトを変更後、Processing メニュー > Start Compilation でコンパイルをスタートします。

この回のコンパイルが、まさに “スマート・コンパイル” になります!

なお、このオプションが適用されていても、再び論理合成が必要だと Quartus® Prime に判断された場合には自動的に Analysis & Synthesis が実行されます。実行状況や時間は、Tasks ウィンドウやコンパイル・レポートの Flow Elapsed Time で確認が可能です。

以上が、スマート・コンパイルの実行方法です。

その実行方法は?(ラピッド・リコンパイル)

こちらも、ものすごく簡単です!!

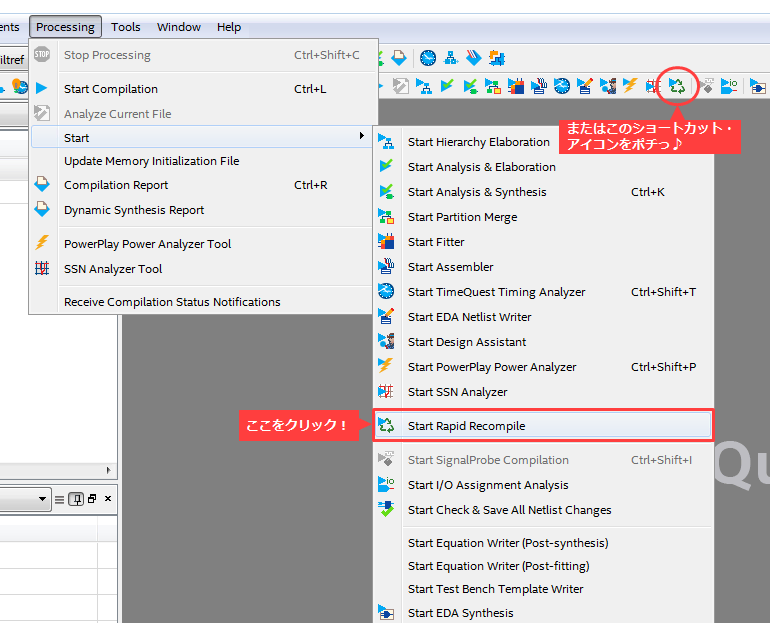

Processing メニュー > Start > Start Rapid Recompile をクリック!

これだけでラピッド・リコンパイルの再コンパイルが実行されます。

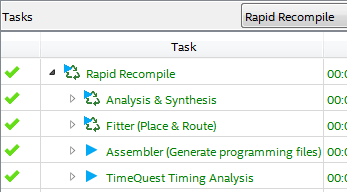

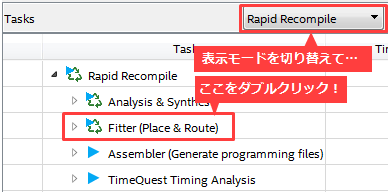

実行状況や時間は、Tasks ウィンドウ(自動的に Rapid Recompile モードに表示が変わります。)やコンパイル・レポートの Flow Elapsed Time で確認が可能です。

デザイン規模や変更内容の状況にも依存しますが、合成前のHDLを変更する(推奨5%以下)場合にはコンパイル速度を最大3倍に、配置配線(フィッティング)後の SignalTap® II ロジック・アナライザーを使った信号解析での条件変更の場合には最大4倍に、高速化が期待できますよ。

以上が、ラピッド・リコンパイルの実行方法です。

ハナコのちょこっとポイント!

ここでお伝えしたい結論は、「ラピッド・リコンパイルを使うとき、基本的にはスマート・コンパイル機能は OFF にしましょう。」です。

今までラピッド・リコンパイルを実行していたのに、レイアウトを変更後につい通常のコンパイル(Processing メニュー > Start Compilation)を実行してしまうと以下のエラーになることがあります。

ID:14608 You have completed a Rapid Recompile incremental compilation. Please run the Rapid Recompile Fitter to re-iterate your Rapid Recompile incremental compilation, or run Analysis & Synthesis (quartus_map) to start a Full Compilation.

"スマート・コンパイル" と "ラピッド・リコンパイル" は、前回のコンパイル結果(データベース)に対する処理のアルゴリズムが異なるため、このようなエラーが発生してしまいます。

上記エラーの回避策は、Rapid Recompile Fitter を単独実行(右図参照)後に改めてラピッド・リコンパイルを実行します。

このエラーはあくまでも一例で、他にもデータベースの不適合により別のエラーが発生することもあります。

"基本的には" と書いたのは、Quartus® Prime の特性を理解し きちんとした手順を踏めば、エラーを回避できますし機能の併用も可能です。…が、私から言わせてもらえば(せっかくラピッド・リコンパイルを使っているのに)この2つのオプション併用はあまり意味がないですね~。

最後に

いかがですか、こんなに簡単な操作でコンパイル時間を短縮できるなんて、画期的だと思いませんか?

ぜひみなさんもお試しください!

おすすめ記事/資料はこちら

FPGA デザインの一部だけを再コンパイルする方法

Quartus® はじめてガイド - コンパイル・レポート・ファイルの見方

Quartus® ガイド - Design Space Explorer II の使い方

FPGA / CPLD の一般的な開発フロー