こんにちは。

マクニカでインテル® FPGA 製品の技術サポートをしている インテル・F・ハナコ です。

Nios® II のブート・プログラムを MAX® 10 FPGA 内部のオンチップ・メモリに組み込む方法は2通りあります。

- オンチップ・フラッシュに組み込む

- オンチップ RAM に組み込む

参考: FPGA のオンチップ・メモリでNios® II をブートさせてみよう

今回は、MAX® 10 のオンチップ ・フラッシュである User Flash Memory(UFM)に Nios® II のブート・プログラムを組み込む方法をご紹介します。

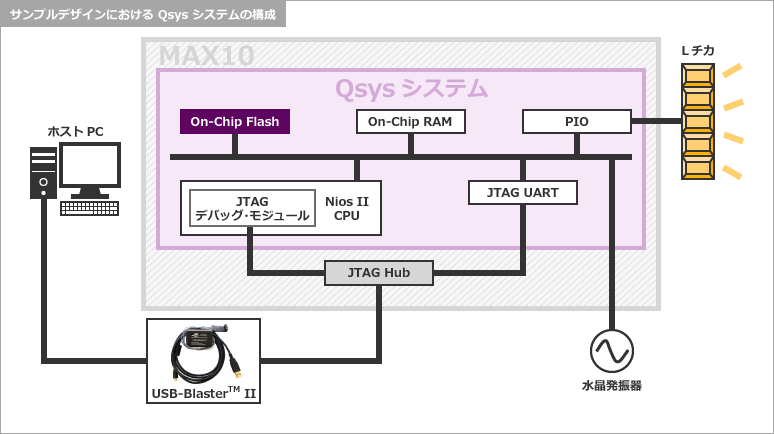

今回作ったデザインの概要

今回作った Qsys システムは、

ブート・プログラム用メモリをオンチップ・フラッシュ(UFM)、実行プログラム用メモリをオンチップ RAM で構成しています。

Nios® II がブート時にLチカする超シンプルなデザインです。

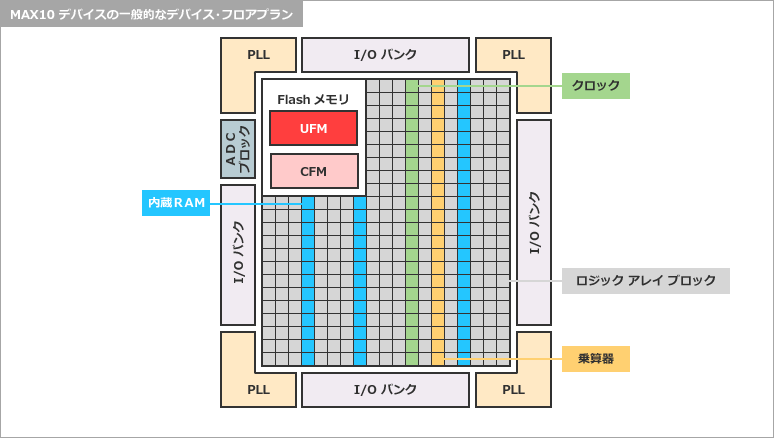

UFM の容量について

MAX® 10 には、不揮発性のフラッシュメモリ領域(UFM/CFM)が内蔵されています。

UFM の容量は下表のとおりです。

| Device | 10M02 | 10M04 | 10M08 | 10M16 | 10M25 | 10M40 | 10M50 |

| Total User Flash Memory Size (Kb)(※) | 96 | 1,248 | 1,376 | 2,368 | 3,200 | 5,888 | 5,888 |

(※) 選択したモードに依存する、指定可能な最大値です。

Nios® II のブート用プログラムがこの容量に収まれば、ブートメモリを UFM に指定できます。

ブート用プログラムのサイズは、Nios® II Software Build Tool(以下、Nios® II SBT)でビルドした際に Console 画面に表示される elf ファイルのプログラム・サイズを参考にしてください。

UFM の詳細は下記ドキュメントをご覧ください。

MAX 10 User Flash Memory User Guide (PDF)

操作フロー

Qsys において On-Chip Flash 以外の Nios® II やペリフェラルはすでに構成してあるものとします。

1. Qsys システムに On-Chip Flash を追加

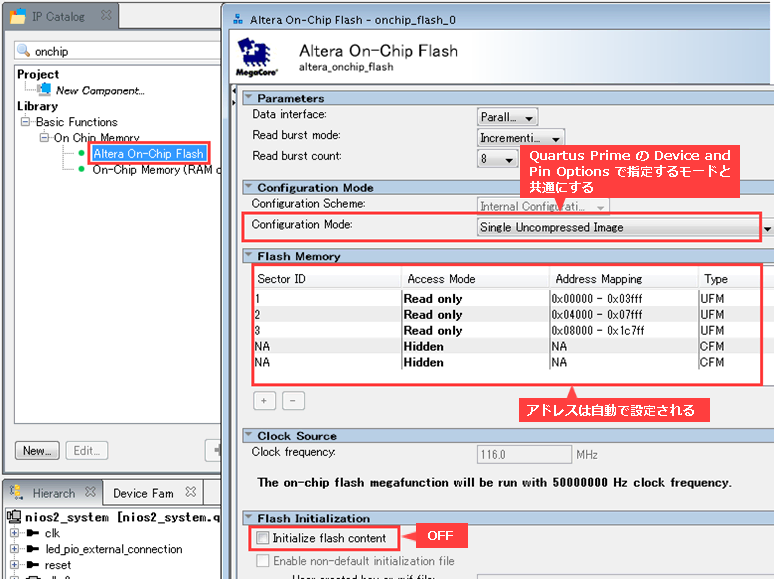

MAX® 10 の UFM を使用するには、“Altera On-Chip Flash” と言う無料の IP を組み込みます。

Tools メニュー > Qsys を起動し、IP Catalog(画面左上)から “Altera On-Chip Flash” をダブルクリックで選択します。

・ Configuration Mode を選択します。

UFM ブートをサポートする Configuration Mode は、以下の3つです。システム仕様に応じて選択してください。

Single Uncompressed Image

Single Compressed Image

Dual Compressed Images

今回のデザインではごく小さなプログラムで、UFM をブートメモリ以外には使用しないので、Single Uncompressed Image を選択しています。

・ Flash Memory でオンチップ・メモリのセクタ構成を決めます。

各セクタのアクセス・モードを Read only / Read and write / Hidden から選択します。

今回のデザインでは UFM を Nios® II のブートメモリ限定で使用するので、Read only にしています。

・ Initialize flash content オプション = OFF にします。

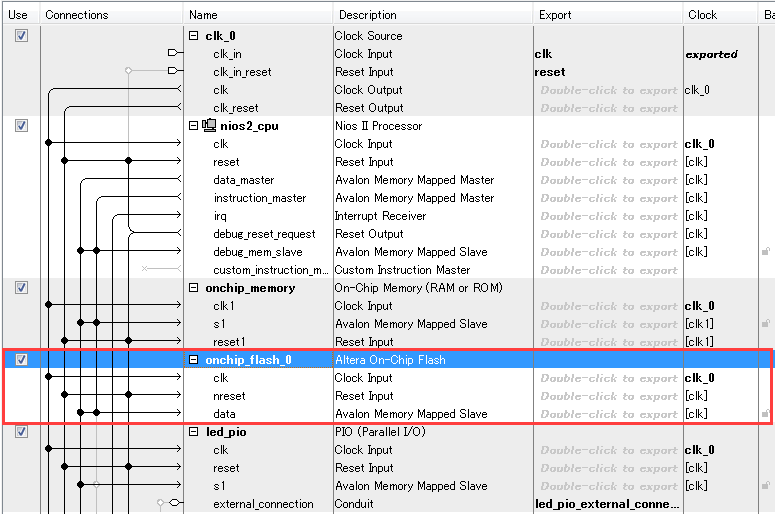

・ On-Chip Flash を Qsys システムに接続します。

ハナコのちょこっとポイント♪

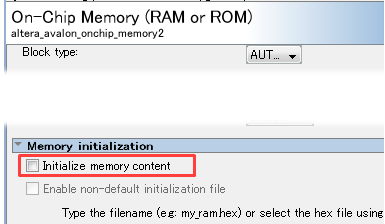

On-Chip Flash で選択できる Configuration Mode は3つともメモリの初期値をサポートしていないため、Qsys システムに組み込んでいる On-Chip Memory(RAM)も初期値を保有できません。

そのため、Initialize memory content オプション = OFF にします。

2. Nios® II のブート用メモリの指定

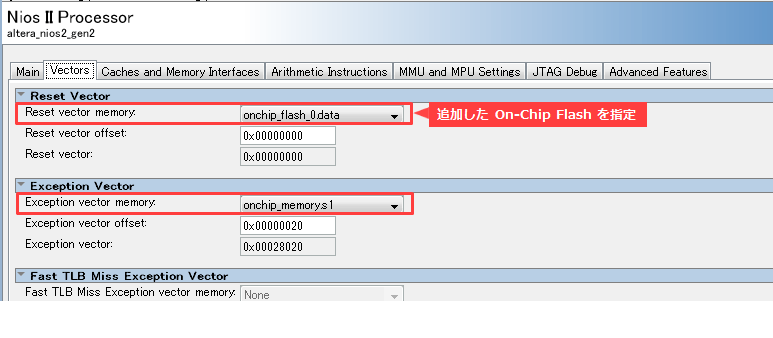

Nios® II の Vectors タブを以下のように指定します。

3. Generate HDL を実行して Qsys システムのモジュール生成

4. Quartus® Prime でコンフィギュレーション・モードの変更

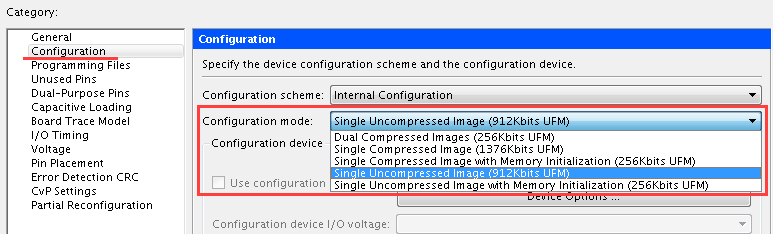

Qsys に組み込んだ On-Chip Flash で選択した Configuration Mode と同じモードを選択します。

Assignments メニュー > Device > Device and Pin Options > Configuration

5. Quartus® Prime でコンパイル実行(Start Compilation)

前編はここまで。

続きはこちらの技術記事をご覧ください。

MAX® 10 の UFM で Nios® II をブートさせてみよう [後編]

後編では、以下の操作を行います。

- Nios® II SBT で BSP Editor を設定し Generate を実行

- Nios® II SBT でブート用プログラムを HEX ファイルに変換

- プログラミング・ファイルのコンバージョン

- MAX® 10 へプログラミング

関連記事

FPGA のオンチップ・メモリで Nios® II をブートさせてみよう

MAX® 10 の UFM で Nios® II をブートさせてみよう [後編]

関連FAQ

MAX® 10 デバイスの Compact は、M9K メモリに初期値を設定できますか?

Nios® II はFPGA 内蔵のオンチップメモリ上のみで動作可能ですか?

関連商品

Odyssey MAX® 10 FPGA Eva Kit

MAX® 10 FPGA 開発キット

MAX® 10 搭載 Nios® II エンベデッド評価キット