こんにちは。

マクニカでインテル® FPGA 製品の技術サポートをしている インテル・F・ハナコ です。

インテル® の MAX® 10 は不揮発性の FPGA です。コンフィギュレーション用のフラッシュ・メモリ(CFM)を内蔵しているので、外部にコンフィギュレーション・メモリは必要ありません。

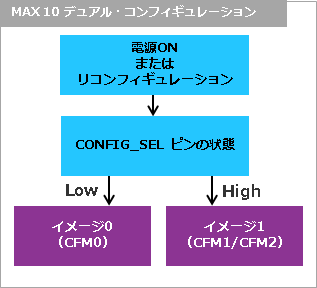

今回は、その CFM のちょっと変わった使い方、“デュアル・コンフィギュレーション” をご紹介します。

デュアル・コンフィギュレーションの概要

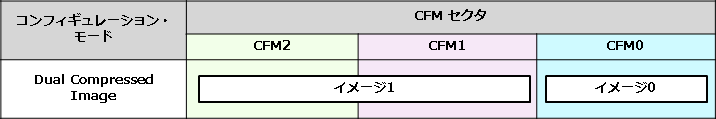

MAX® 10 の CMF は圧縮されたコンフィギュレーション・イメージを最大2つまで格納することができ、その2つのイメージを動作中に切り替えて使用することができます。この構成を “デュアル・コンフィギュレーション” と言います。

(ただしデバイスに2つのイメージを格納するには、圧縮率を30%以上にする必要があります。)

MAX® 10 には機能オプションとして “コンパクト” と “フラッシュ” と “アナログ” の3タイプがあります。

その中で、コンフィギュレーション・モードとして “Dual Compressed Image“ をサポートしている “フラッシュ” と ”アナログ” だけがデュアル・コンフィギュレーションに対応しています。

(ただ、フラッシュ・タイプは WLCSP(ウェハ・レベル・チップ・スケール・パッケージ)で一般的にはあまり使用されないので、事実上 “アナログのみ” と言えます。)

MAX® 10 の CFM は、CFM0/CFM1/CFM2 の3セクタで構成されています。(10M02 は CFM0 のみ。)

CFM0 はコンフィギュレーション・イメージ0の領域として使用され、CFM1 と CFM2 はコンフィギュレーション・イメージ1の領域として使用されます。

デュアル・コンフィギュレーションは、MAX® 10 の CONFIG_SEL ピンを使用してイメージの選択をします。デバイス外部から CONFIG_SEL ピンに High または Low を供給し、MAX® 10 の電源投入時またはリコンフィギュレーション開始時のこのピンの状態に応じて、どちらのイメーがコンフィギュレーションされるかが決まります。

★ 参考資料 (Device Pin Connection Guidelines より)

「MAX 10 FPGA Device Family Pin Connection Guidelines」

準備しよう

MAX® 10 でデュアル・コンフィギュレーションを実現するためには、これら以下が必要です。

● MAX® 10 デバイス(フラッシュあるいはアナログ機能オプション対応)の搭載された開発ボード

例えば、Odyssey MAX® 10 FPGA Eva Kit(以下 Odyssey)や MAX® 10 FPGA 開発キットなどが使用できます。(※ボードの選定条件として、CONFIG_SEL ピンへの入力が High/Low と切り替えられることが絶対条件です。)

● 使用する開発ボードに応じたダウンロード・ケーブル

Odyssey の場合は、USB-Blaster™ または USB-Blaster™ II があった方が楽チン。(無くても microUSB ケーブルで対応可能。参考記事はコチラ)

MAX® 10 FPGA 開発キットの場合は、USB-Blaster™、または USB-Blaster™ II 、または付属の miniUSB ケーブルで Embedded USB-Blaster™ II 対応。

● Quartus® Prime Lite Edition(Pro/Standard Edition でもOK)

MAX® 10 は無償のツールで開発できちゃいます。

● 使用する開発ボード向けのデザイン・プロジェクトを2種類

ひとまず作業フローを体験したいときは、デュアル・コンフィギュレーション用のサンプル・デザインを使っちゃいましょう!Design Store からデザイン・プロジェクトを入手できます。

★ 参考記事 FPGA のサンプル・デザインを無料で手に入れよう

Odyssey のデュアル・コンフィギュレーション用サンプル・プロジェクト(Quartus® Prime 16.0 用)はココから入手できます。

MAX® 10 FPGA 開発キットのデュアル・コンフィギュレーション用サンプル・プロジェクト(Quartus® Prime 16.0 用)はココから入手できます。

実際にやってみよう

ザックリ作業をお話しすると、2つのプロジェクトの SOF ファイルを合成すれば良いのですが、単に合わせれば良いわけではありません。各プロジェクトのデザインにおいて、デュアル・コンフィギュレーション用の IP(無償で使えます)を組み込みます。

流れはこんな感じ。

- デザインにデュアル・コンフィギュレーション用 IP を組み込む

- デュアル・コンフィギュレーション対応にオプションを設定

- コンパイルして SOF を生成

- 2つのプロジェクトの SOF ファイルから POF ファイルを作成

- MAX® 10 デバイスへ POF をダウンロードして動作確認

- CONFIG_SEL への入力を切り替えて動作確認

1. デザインにデュアル・コンフィギュレーション用 IP を組み込む

各プロジェクト・デザインの最上位階層に、デュアル・コンフィギュレーション用 IP を組み込みます。

まず一方のプロジェクトを開き、IP を作成します。

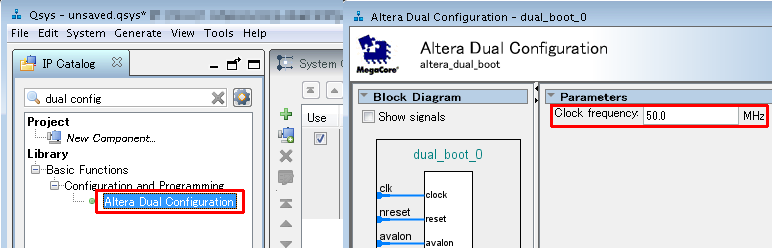

Tools メニュー > Qsys を起動し、IP Catalog(画面左上)から “Altera Dual Configuration” をダブルクリックで選択します。

パラメータ設定画面が表示されるので、この IP へ供給するクロックの周波数を設定します。(例えば、Odyssey の場合は 50MHz に、MAX® 10 FPGA 開発キットの場合はクロック周波数が4種類選択できる仕様なので選択した周波数を設定します。)なお、設定できる周波数は最大 80MHz までです。

Finish ボタンをクリックし、Qsys システムに追加させます。

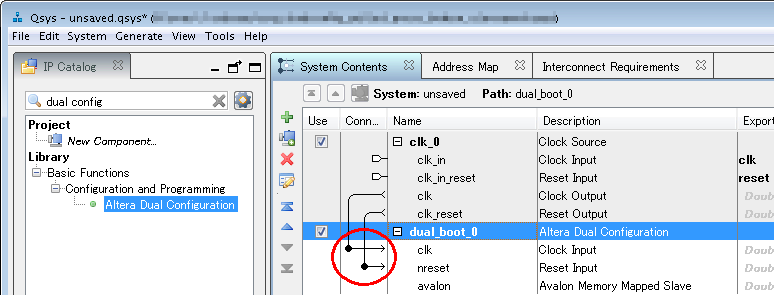

デュアル・コンフィギュレーション用 IP のクロック(clk)とリセット(nreset)ポートを下図のように接続します。

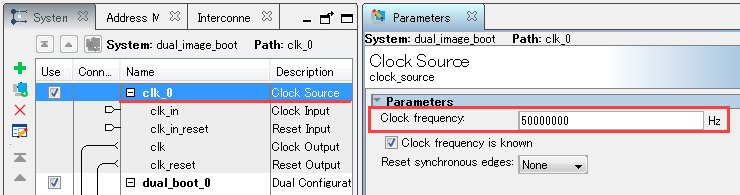

Clock Source(デフォルト名 clk_0)のクロック周波数を 先程設定した Altera Dual Configuration のクロック周波数と同じ値に設定します。

Qsys の File メニュー > Save As において、IP の名前と保存フォルダを指定します。

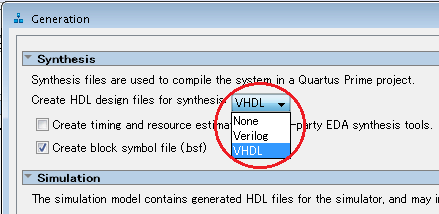

画面右下の Generate HDL ボタンをクリックすると Generation ダイアログボックスが表示されるので、論理合成用に生成される HDL 言語(Verilog/VHDL)を指定します。

Output Directory のパスを確認して、画面右下の Generate ボタンをクリックします。

Generate ウィンドウにログが表示され、“Generate: completed successfully” のメッセージが確認されたら IP 作成完了です。Close ボタン、続けて Finish ボタンをクリックして画面を閉じます。

.qip をプロジェクトに追加するようにメッセージが表示されるので、Add/Remove Files in Project(Project メニュー)から IP を生成したフォルダ内の synthesis フォルダに保存されている .qip ファイルを Add ボタンで登録します。

続いて、Altera Dual Configuration IP をプロジェクトの最上位デザインに加え、クロック、リセット(Low アクティブ)を接続します。編集終了後、デザインを保存してください。

2. デュアル・コンフィギュレーション対応にオプションを設定

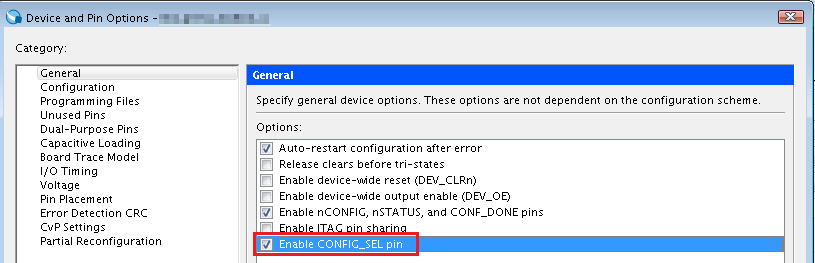

Device and Pin Options(Assignments メニュー > Device)において、各種オプションを設定します。

[General カテゴリ]

- Enable CONFIG_SEL pin オプション = ON に設定します。

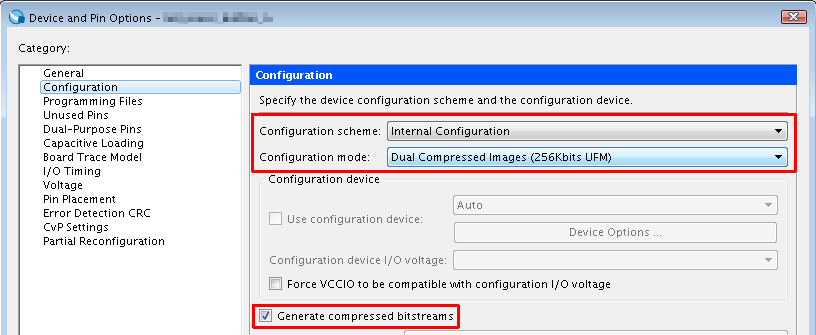

[Configuration カテゴリ]

- Configuration Scheme : Internal Configuration

- Configuration Mode: Dual compressed Images

- Generate compressed bitstreams オプション : ON

設定したら、全てのダイアログボックスをOKボタンで閉じます。

3. コンパイルして SOF を生成

Quartus® Prime 画面左下に位置する Tasks ウィンドウの Compile Design をダブルクリックし、コンパイルを実行、完了させます。その後、プロジェクトを終了します。

※ この 1~3 の作業を、もう一方のプロジェクトでも行ってください。

4. 2つのプロジェクトの SOF ファイルから POF ファイルを作成

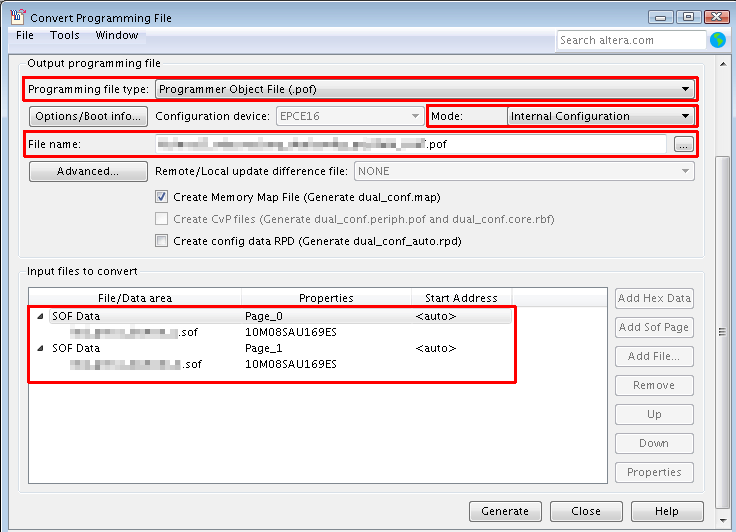

Quartus® Prime の File メニュー > Convert Programming Files を起動し、以下の設定をします。

[Output programming file]

- Programming file type: Programmer Object File (.pof)

- Mode: Internal Configuration

- File name: 作成する POF ファイルのファイル名と保存フォルダを指定 (必要に応じて Options/Boot info オプションを設定してください。)

[Input files to convert]

- SOF Data を選択して、Add File ボタンをクリック。Page_0 に CFM0 へ書き込むプロジェクトの SOF ファイルを選択します。

- Add Sof Page ボタンをクリックし、Page_1 を追加します。下段の SOF Data を選択して、Add File ボタンをクリック。Page_1 に CFM1 へ書き込むプロジェクトの SOF ファイルを選択します。

Generate ボタンをクリックして、”Generated ファイル名.pof successfully” のメッセージと共に POF ファイルが作成されます。

Close ボタンでウィンドウを閉じます。

5. MAX® 10 デバイスへ POF をダウンロードして動作確認

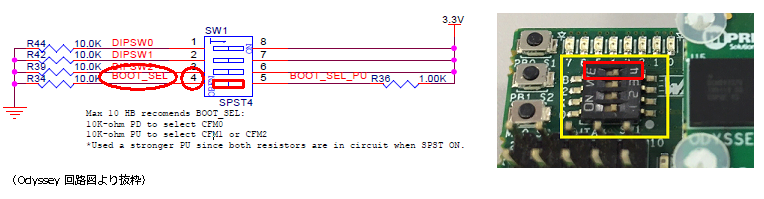

POF ファイルを書き込む前に、CONFIG_SEL ピンのステータスを確認、設定しておきましょう。

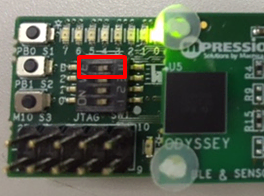

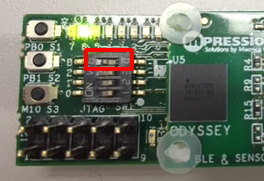

ちなみに Odyssey や MAX® 10 FPGA 開発キットの場合は、CONFIG_SEL ピンは DIP スイッチでプルアップ/プルダウンを切り替えられる仕様になっています。

では MAX® 10 の CFM に POF ファイルを書き込みましょう。

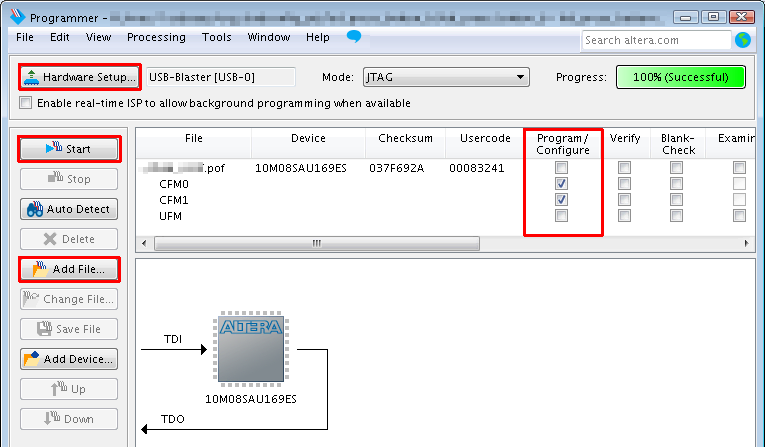

ボード、ダウンロード・ケーブルなどの準備をしたら、Tools メニュー > Programmer を起動し、以下を設定します。

- Hardware setup: 使用するダウンロード・ケーブルを選択

- Mode: JTAG

- Add File ボタン: 作成した POF ファイルを選択

- Program/Configure オプション: ON

★ 参考情報: もしも Hardware Setup に USB-Blaster™ 系の名前が表示されないときは…

USB-Blaster™ のドライバをインストールしてみよう

USB-Blaster™ II のドライバをインストールしてみよう

Windows 10 に USB-Blaster™ および USB-Blaster II ドライバをインストールできないときの対処方法

Start ボタンをクリックして、書き込みスタ~ト!

Progress バーが 100% を表示し、Messages ウィンドウに “Successfully performed operation(s)” のメッセージが確認できたら書き込み完了です。

ボードの電源を一度OFFしてダウンロード・ケーブルを外します。その後ボードの電源を再びON!

ボード上の CONFIG_SEL のステートに応じた CFM が選択され、そこに格納されたイメージがコンフィギュレーションされ動作していることが確認できます。

右画像は、イメージ0 が選択されて、LED0/LED1 が交互に点滅するデザインが動作している様子です。

(静止画ですみません。)

6. CONFIG_SEL への入力を切り替えて動作確認

続いて、CONFIG_SEL のステートを切り替えてみましょう。

その後、ボードの電源を再投入(OFF→ON)するか、あるいは MAX® 10 の電源を投入したままリコンフィギュレーションさせるために nCONFIG ピンをあるパルス幅以上 Low に引き下げ、再び High を供給します。

Odyssey は nCONFIG ピンが 10Ω 抵抗を介して 3.3V へプルアップ(固定)されているので、電源の再投入で対応してください。

もう一方のイメージがコンフィギュレーションされ動作していることが確認できます。

右画像は、イメージ1 が選択されて、LED6/LED7 が交互に点滅するデザインが動作している様子です。

(こちらも静止画ですみません。)

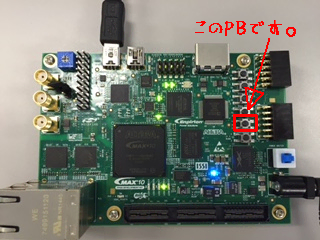

MAX® 10 FPGA 開発キットの場合は、nCONFIG ピンにプッシュボタン(PB)が付いていて、このPBを押すことで nCONFIG に Low パルスが供給されて、ボードの電源をOFFにしなくてもリコンフィギュレーションを実行することができるので便利です。

以上で、MAX® 10 のデュアル・コンフィギュレーション・システムは完成です♪

みなさんも是非体感してくださいね。

今回登場した開発ボードやダウンロード・ケーブルはこちらで購入できるので、すぐに体験できますよ。

関連商品