※ ここまでの内容は以下をご覧ください。

Beryll の FPGA でクロック同期によるLチカ![#1/3]

Beryll の FPGA でクロック同期によるLチカ![#2/3]

Beryll ボードに実際に設計してきたデザインを書き込んで、動作させてみましょう。

6. 実機デバッグをする

Cyclone® V GX の JTAG ポートを活用して、コンフィギュレーション・データ(*.sof)をパソコンから直接転送してデバッグをしたいと思います。

Beryll に電源ケーブルを装着後、Beryll とパソコンを付属の USB-miniUSB ケーブルで接続し、Beryll の電源を On にします。

Quartus® Prime のProgrammer を起動して、SOF ファイルをセットしたら、Start ボタンをポチッ♪ Programmer の Progress バーが100%になったらデータ転送完了です。

Beryll とはじめて接続するパソコンの場合は、On-Board USB-Blaster を認識させるためにドラバのインストールが必要です。

インストール方法は こちらの記事 をご覧ください。

いざ!実機で検証

LED が点滅しているのが確認できます。

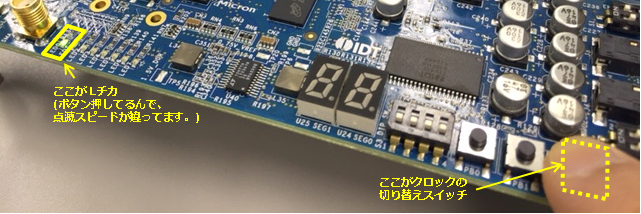

では、FPGA 内部のレジスタの入力クロック周波数を切り替えるため、プッシュボタンをポチッ♪と押してみましょう。

おぉ!点滅スピードが変わりました!(静止画なのが残念です。)

7. コンフィギュレーション ROM にプログラミング

デバッグが完了したので、次に Quartus® Prime の Programmer を使って、基板上のコンフィギュレーション ROM(EPCS128)に Cyclone® V のコンフィギュレーション・データを書き込みます。

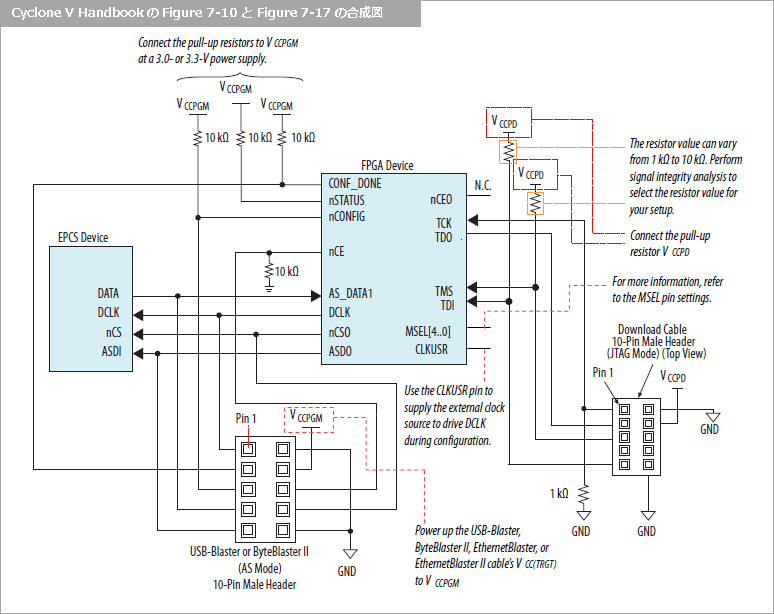

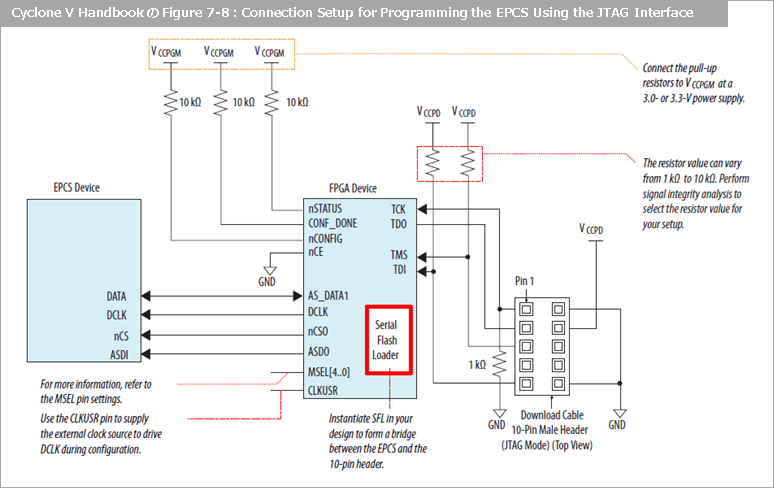

Cyclone® V と EPCS デバイス間のデータ転送方式は「アクティブ・シリアル・コンフィギュレーション・モード(通称 AS モード)」と言います。通常、この AS インタフェースを使って EPCS デバイスにプログラミングするには、基板上に 10 ピン・ヘッダ(下図の左側のヘッダ)が必要です。このヘッダに USB-Blaster II または USB-Blaster ダウンロード・ケーブルのコネクタを装着します。

一方、先ほどの 操作6 のように FPGA に対して JTAG ポート経由でデータをコンフィギュレーションしたり、SignalTap® II と言う FPGA デバッグ機能を活用したりする場合は、別途 FPGA に対する JTAG 用の 10 ピン・ヘッダ(下図の右側のヘッダ)も必要です。

これだと、基板上に2つ分の10ピン・ヘッダ用のスペースを確保しなければなりませんよね。

でも JIC(JTAG Indirect Configuration)機能 を活用すると、FPGA 内部の シリアル・フラッシュ・ローダ(SFL) デザインがブリッジとなって、EPCS デバイスに対するプログラミングが JTAG ポート経由でできるようになります。そのため、AS モード用の10ピン・ヘッダを用意する必要がなくなり、基板面積を縮小できて低コスト化を図れます。

【参考資料】AN 370: Using the Intel FPGA SerialFlash Loader with the Intel QuartusPrime Software

Beryll はまさにこの構成を採用しています。

シリアル・フラッシュ・ローダ経由のプログラミングは、従来の SOF ファイルや POF ファイルではなく、JIC ファイル で行います。FPGA 用のコンフィギュレーション・ファイルの SOF ファイルから JIC ファイルを作成し、プログラミングを実行します。

操作フローは以下の2ステップです。

7-1. SOF ファイルから JIC ファイルを生成

7-2. EPCS へのプログラミング

7-1. JIC ファイルの作成

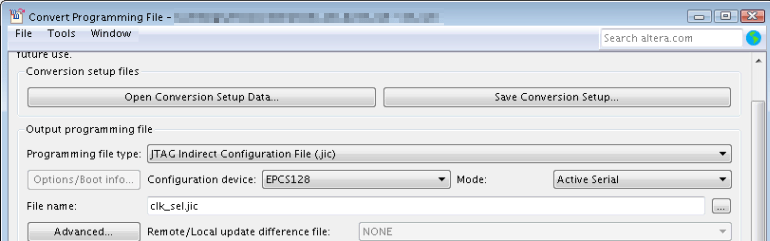

(1) File メニュー > Convert Programming Files を選択します。

(2) Output Programming File 項目で以下の内容を選択・指定します。

- Programming file type: JTAG Indirect Configuration File (.jic)

- Configuration device: EPCS128(プログラミングするコンフィギュレーション・デバイスの型式)

- Mode: Active Serial

- File name: 生成するファイルの保存フォルダ選択と出力ファイル名の指定

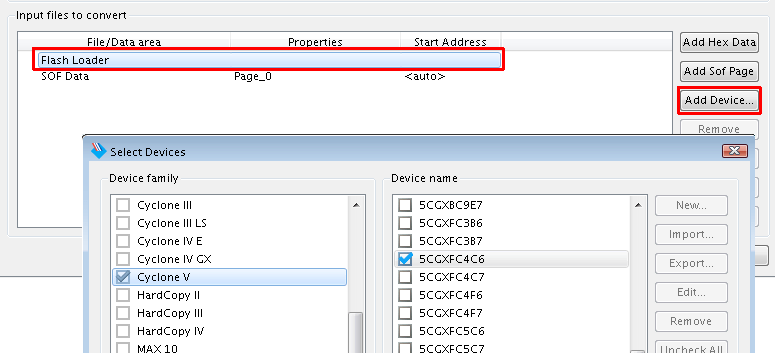

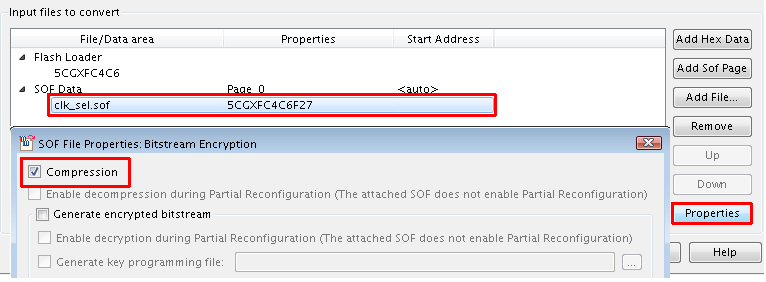

(3) Input files to convert 項目で以下の内容を選択・指定します。

(3)-1. シリアル・フラッシュ・ローダ・デザインを使用するFPGA の型式を選択します。

- Flash Loader 行を選択し、Add Device ボタンをクリックします。

- Select Device ダイアログ・ボックス: Device family= Cyclone V、Device name= 5CGXFC4C6

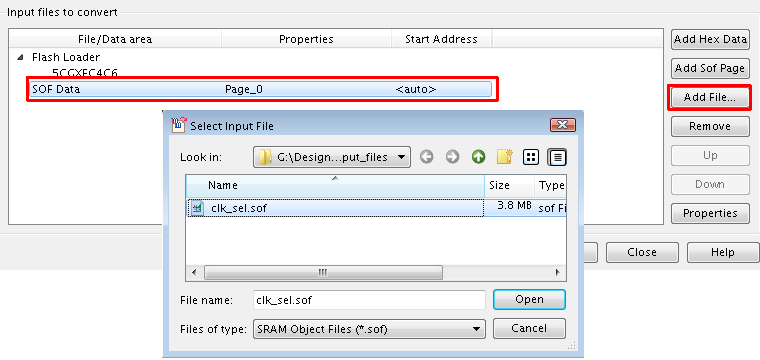

(3)-2. JIC ファイルのもとになるコンフィギュレーション・ファイル (.sof) を指定します。

- SOF Data 行を選択し、Add File ボタンをクリックします。

- 変換する sof ファイルを選択し、Open ボタンをクリックします。

プログラミング・ファイルを圧縮する場合は、圧縮したい SOF ファイルを選択し、Properties ボタンをクリックします。SOF File Properties ダイアログ・ボックスにて、Compression オプションにチェックを入れ OK ボタンをクリックします。

(4) Generate ボタンをクリックします。

“Generated jic ファイル名 successfully” のメッセージが表示され、JIC ファイルの生成は完了です。

7-2. EPCS へのプログラミング

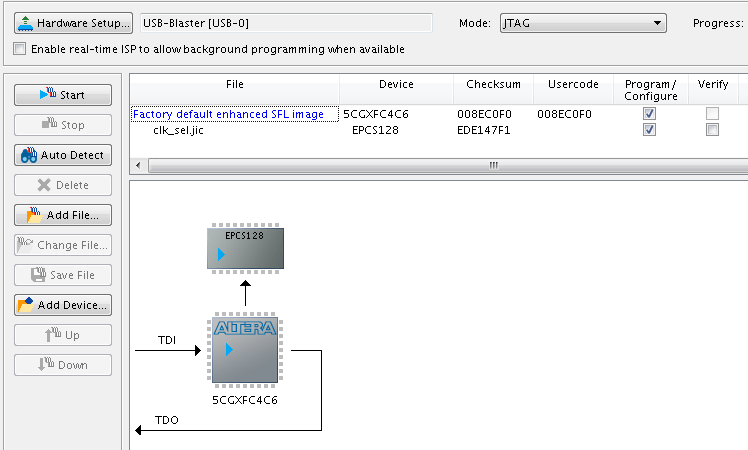

生成した JIC ファイルを EPCS デバイスに JTAG モードでプログラミングします。

Quartus® Prime のProgrammer を起動します。JIC ファイルをセットして Program/Configure オプションにチェックしたら、Start ボタンをポチッ♪Programmer の Progress バーが100%になったら、JTAG Indirect Configuration による EPCS デバイスのプログラミングは終了です。

Beryll ボードの電源を ON するごとに EPCS128 から Cyclone® V GX FPGA へコンフィギュレーション・データが転送され、FPGA が動作を開始するようになりました。

今回は、Beryll の紹介以外にも、FPGA を開発していく上で必要な情報を色々と盛り込んでお送りしました。

是非、ご自身の開発にも活用してみてください。

Beryll の FPGA でクロック同期によるLチカ!シリーズ

Beryll の FPGA でクロック同期によるLチカ![#1/3]

Beryll の FPGA でクロック同期によるLチカ![#2/3]

Beryll の FPGA でクロック同期によるLチカ![#3/3]

Beryll の開発者インタビュー

関連商品