この「Quartus® はじめてガイド」シリーズは、インテル® Quartus® Prime / Quartus® II 開発ソフトウェアを初めてご利用になるユーザ向けの資料です。

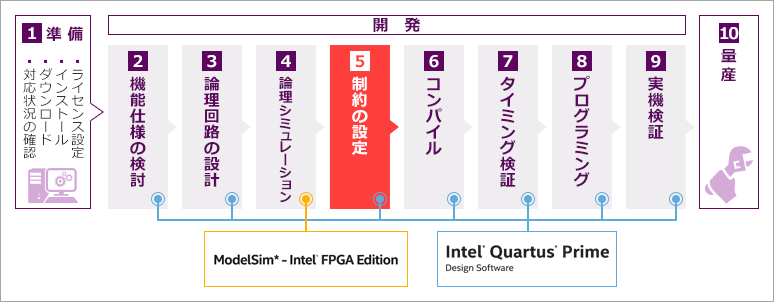

FPGA / CPLD の開発フローについては、こちらを参照してください。

説明

この資料は、FPGA / CPLD 開発の『5. 制約の設定』フェーズで参考になります。

Quartus® Prime / Quartus® II 開発ソフトウェアでターゲットの FPGA / CPLD のデザイン(回路)に対して、タイミング制約を与える方法について紹介しています。

この資料は、FPGA / CPLD のデザイン(回路)に対して、タイミング制約を与える際に使用するタイミング制約用ファイル(SDC ファイル)の作成方法について説明しています。元々は ASIC 業界の標準フォーマットになっている Synopsys Design Constraints (SDC) ファイルを FPGA / CPLD のタイミング制約に使用することで、Quartus® Prime / Quartus® II 開発ソフトウェアの Fitter(配置配線)で目標(ガイド)として参照するだけでなく、TimeQuest Timing Analyzer による高性能なタイミング解析にも使用します。

資料

Quartus® Prime はじめてガイド - TimeQuest によるタイミング制約の方法 ver.17

(ツール・バージョン:Ver.17.1 用ドキュメント(Rev.2)

Quartus II はじめてガイド - TimeQuest によるタイミング制約の方法 ver.15

(ツール・バージョン:Ver.15.0 用ドキュメント(Rev.2)

おすすめ記事/資料はこちら

TimeQuest ~タイミング解析の用語と考え方~

Quartus® Prime 関連の記事や資料

インテル® FPGA の開発フロー/FPGA トップページ

おすすめ FAQ はこちら

おすすめセミナー/ワークショップはこちら

Quartus®Prime 入門編トライアル・コース <無料>

カスタムマイコン設計トライアル ~MAX® 10 FPGA を使った組込み設計を体感!~ <無料>