BGAからの配線などで途中でZ0が変わる線路

BGAパッケージ下部とそれ以外の配線パターンは、配線幅が異なるので、特性インピーダンスが異なります。その結果、接続部での反射により、波形乱れが生じます。

パターンの幅

BGAパッケージの下部の配線は、パッケージの端子間の狭いすき間を縫うように通す必要があります。

BGAパッケージの端子密度は高いので、配線パターンは、必然的に通常の配線に比べてギリギリまで細くする必要があります。

細い配線パターンは、断線の確率が高いので、歩留りの低下を避けるため、必要最小限に留めます。

パッケージの下部以外の通常の配線パターンは、十分な歩留りが得られる、BGA下部よりも太い(広い)パターン幅を用います。

特性インピーダンス

配線パターンの特性インピーダンスは、配線幅に影響されます。細いパターンは特性インピーダンスが高く、太いパターンは低いインピーダンスになります。

したがって、BGA下部は特性インピーダンスが高く、それ以外では、それよりも低くなります。

BGA下部以外の配線は、通常、50Ω程度に選びます。

以下を参照ください。

ボードの特性インピーダンスの決め方

https://www.macnica.co.jp/business/semiconductor/articles/basic/111385/

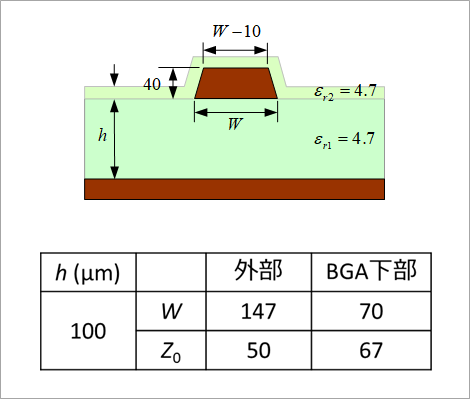

図1に表面層の断面を示します。

グラウンドからの距離(厚み)hを100μmとし、BGA下部のパターン幅を70μmとすると、特性インピーダンスZ0は、67Ωとなります。

BGA下部以外は、Z0=50Ωに選びます。このときのパターン幅は147μmです。

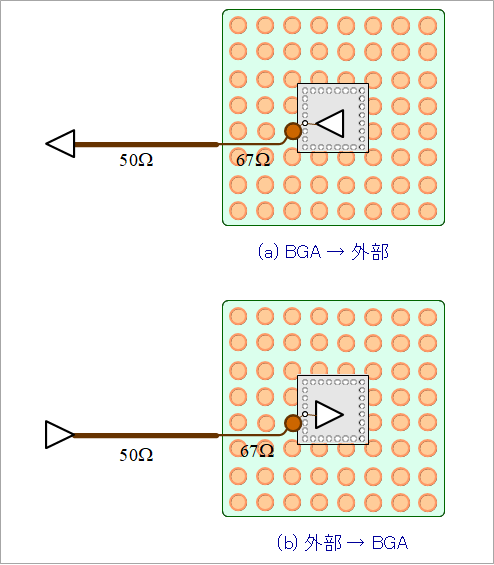

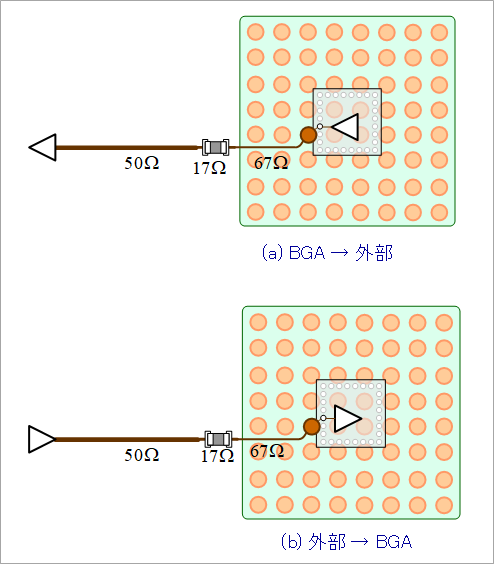

図2は、今回のテーマの配線の様子を示します。

BGA下部とそれ以外の特性インピーダンスが異なるため、接続点の反射による影響があります。

同図の(a)は、BGA側がドライバで、BGAから、細いパターンを経て、外部に信号が伝わります。同図(b)は、逆に、外部からBGAに信号が伝わります。

反射解析

反射解析は、計算による方法では、格子線図または、縦続行列を高速フーリエ変換して波形を求めます。

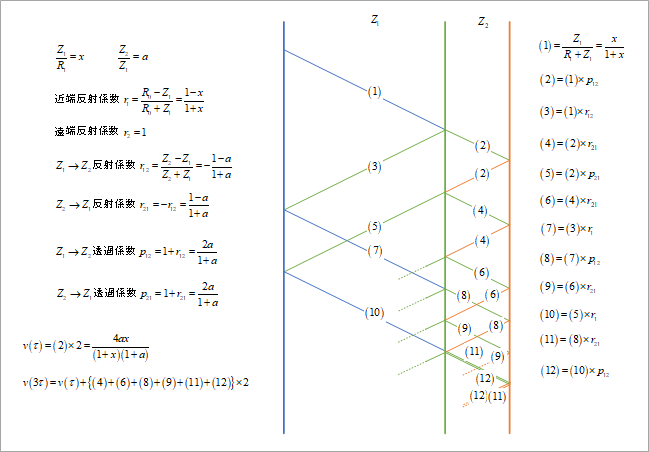

図3に、図2(b)の場合の格子線図を示します。

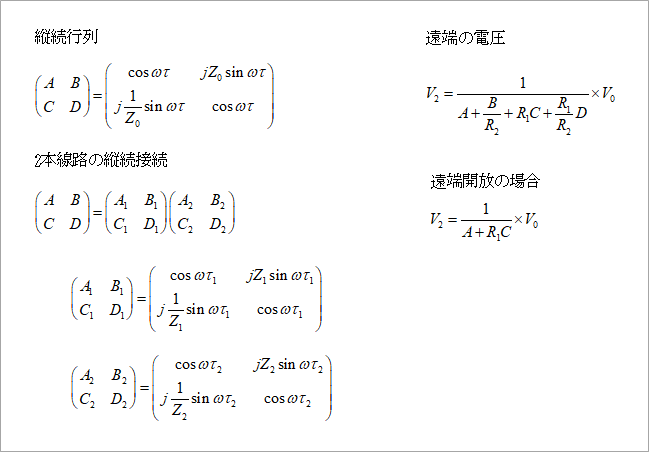

図4に、縦続行列による計算を示します。V0は、ドライバの出力振幅です。

縦続行列を周波数に対して求め、iFFT(高速フーリエ逆変換)により出力波形を求めます。

各パラメータの影響を知るには計算が有用ですが、結果を得るだけなら、SPICEが簡単です。

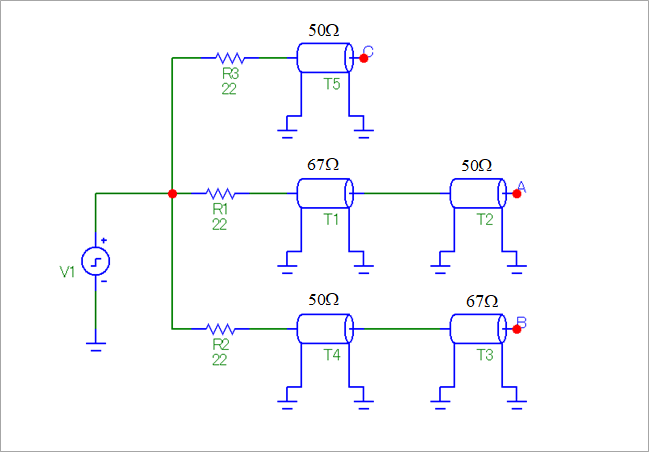

図5は、回路図の例です。図2の(a)と(b)および、Z0が50Ωのままで、途中で変化しない場合も含めて同時に解析できます。

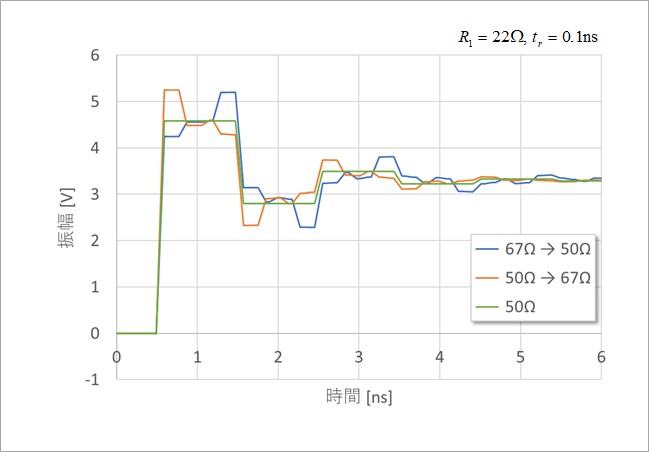

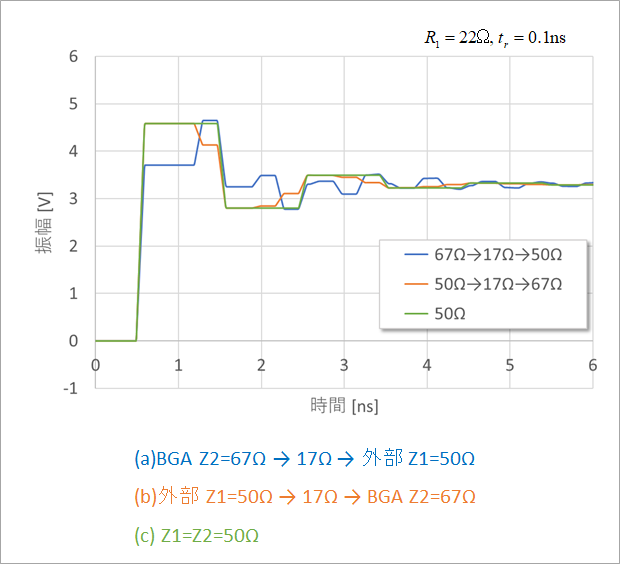

図6は、図2の条件における遠端(レシーバ端)の波形を示します。

凡例に記載の、67Ω→50Ωは、図1(a)に相当し、50Ω→67Ωは、図1(b)に相当します。

同じく、50Ωは、インピーダンスが途中で変わらず50Ωの場合です。

ドライバの出力抵抗R1は22Ωで、12mAドライバ相当です。

緑の50Ωの波形は、4.5Vのオーバシュートと、2.8V程度の跳ね返りが生じます。

これに対して、途中でインピーダンスが変化する線路では、同図に示すように、さらに大きなオーバシュートと跳ね返りが生じます。

なお、同図は、縦続行列とiFFTによる解析結果です。当然ながら、SPICEも同じ結果となります。

対策

この対策として、通常よりやや大きなダンピング抵抗22Ωを挿入します。

R1=22Ω、Z0=50Ωのとき、x=50/22=2.27です。22Ωのダンピング抵抗を追加すると、x=50/44=1.14と半分になり、x/(1+x)は、0.69から0.53に小さくなります。

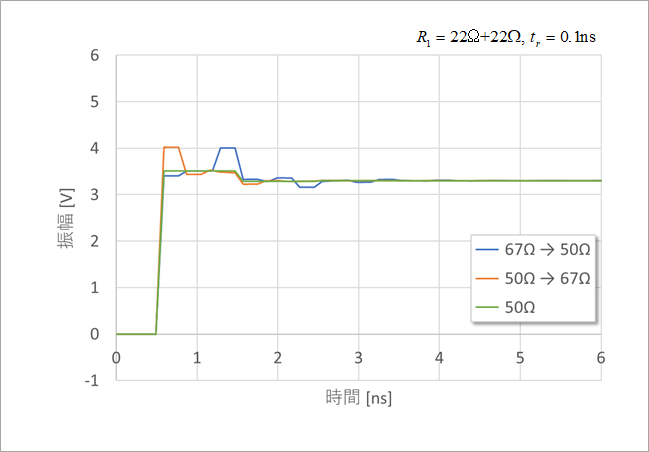

図7は、ダンピング抵抗22Ωを追加した場合の反射波形で、オーバシュートが小さくなり、跳ね返りは小さく抑えられていることが分かります。

通常は、12mAドライバの場合、オーバシュートを10%に抑えるには、ダンピング抵抗の値を18Ωに、オーバシュートを20%まで許容するなら、ダンピング抵抗を11Ωにします。

ダンピング抵抗の求め方は、

「もっと簡単に決めるダンピング抵抗の値」

https://www.macnica.co.jp/business/semiconductor/articles/basic/112905/

を参照ください。

図2(a)の場合、ドライバがBGAなので、ダンピング抵抗は入れられません。このICが、FPGAなら、駆動能力を低く選択してください。

もう一つの対策として、図8に示すように、BGA下部の67Ωの線路と、外部の50Ωの線路との接続点に、このインピーダンスの差の17Ω(E24系列では16Ωまたは18Ω)を挿入する方法があります。

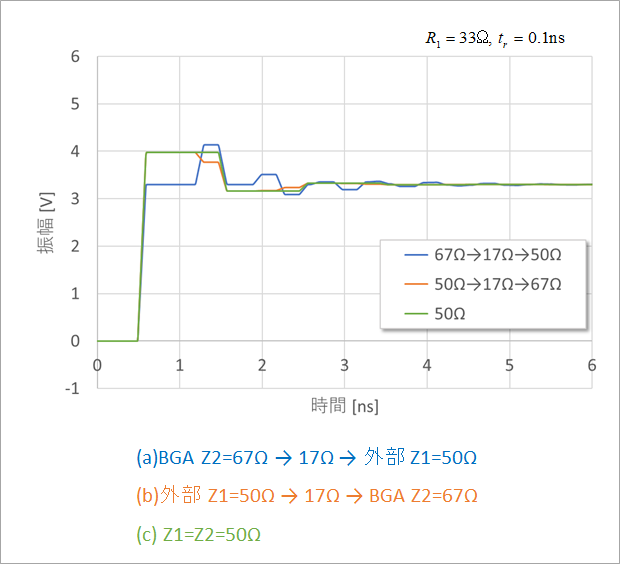

図9はこのときの解析結果です。

オーバシュートもその跳ね返りも、50Ωで統一したときの内側に入っています。

さらに、図9にダンピング抵抗11Ωを挿入したとき(R1=33Ω)の解析結果です。

いくつかの対策案を述べました。

外付け抵抗の有無や、対策効果を比較して、より有効な対策を選んでください。

碓井有三のスペシャリストコラムとは?

基礎の基礎といったレベルから入って、いまさら聞けないようなテーマや初心者向けのテーマ、さらには少し高級なレベルまでを含め、できる限り分かりやすく噛み砕いて述べている連載コラムです。

もしかしたら、他にも気になるテーマがあるかも知れませんよ!