遠端終端は「最遠端」に

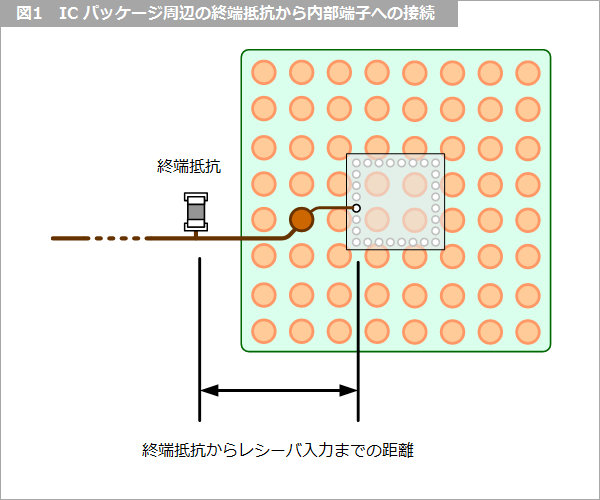

遠端の終端抵抗は、文字どおり遠端、それも最遠端に配置します。最近は、IC のパッケージも大型化して、図1 に示すように、パッケージの周辺からパッケージ内部の端子までの距離が数センチになることは珍しくありません。したがって、終端抵抗が最遠端に配置できません。

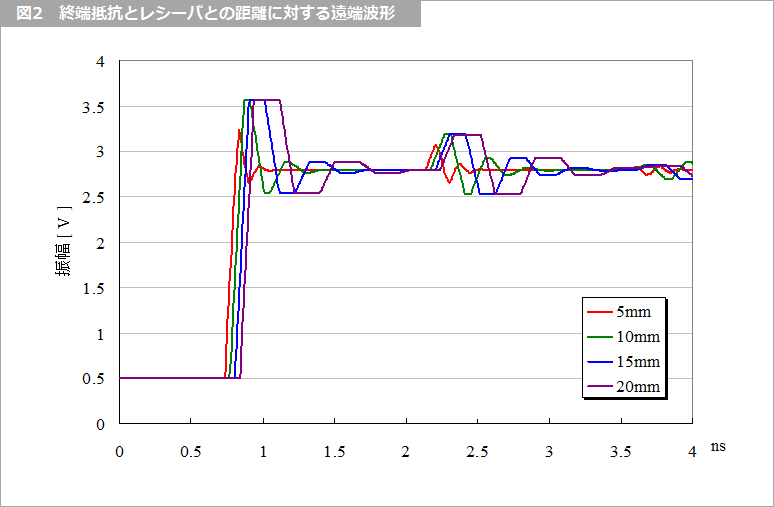

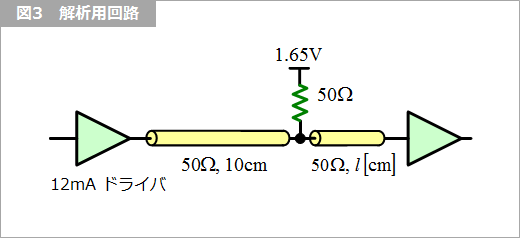

図2 は、終端抵抗と最遠端との距離に対して、最遠端の信号波形を解析して示します。終端抵抗と最遠端との距離が長くなればなるほど波形乱れが大きくなります。

図3 は、これを回路図に書き表したもので、終端抵抗から最遠端のレシーバの間の配線はスタブとして働きます。回路図中の定数は、図2 の解析用で、影響を多少誇張するために、ドライバの立ち上がりを、100ps としています。

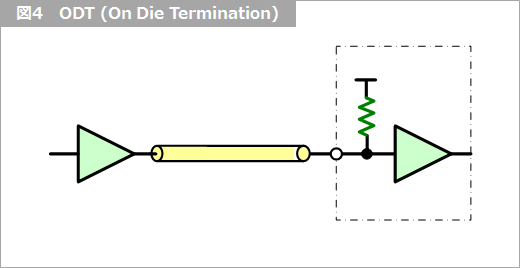

ODT (On Die Termination)

この不具合な現象を回避する手法として、DDR2 SDRAM の世代から 図4 に示すような、IC チップ内に終端抵抗を内蔵する、ODT (On Die Termination)が導入されました。ODT を有しない場合に、図2 および 図3 に生じるスタブの影響を回避するにはどうすればよいか? 少し考えてみてください。最後に正解を載せておきます。

Dynamic ODT

遠端終端は、消費電力の増加を招きます。終端抵抗をチップに内蔵することにより、必要なときだけ終端を接続し、必要でないときには切断する機能が追加されています。この方法を、Dynamic ODT といいます。この機能は、DDR3 SDRAM の世代から導入されました。

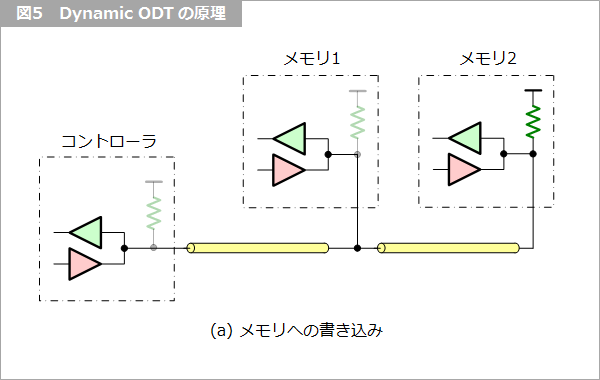

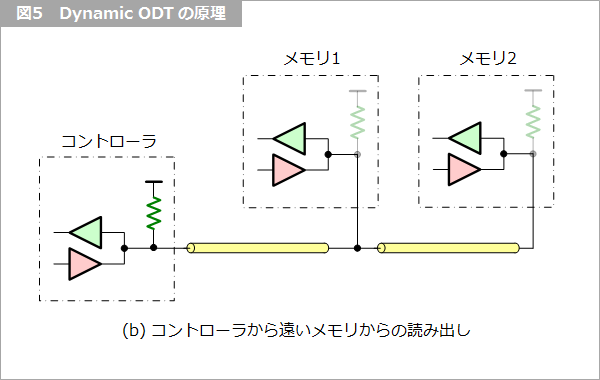

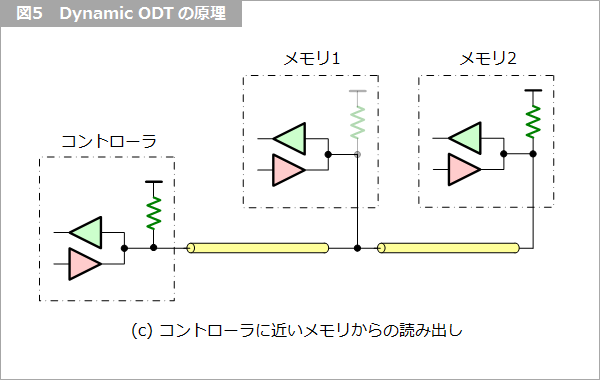

図5 は、メモリの ODT の原理です。図5(a) はメモリに対する書き込みの場合、図5(b) はコントローラから遠いメモリからの読み出しの場合、図5(c) は途中のメモリからの読み出しの場合をそれぞれ示します。どこの終端を有効にして、どこの終端を無効にするかは、以下の原則(原理)によります。

- 1対1 伝送の場合は、1個所だけ非整合を許す。

- 整合終端した線路は、時間遅れを無視すれば純抵抗とみなすことができる。

図5(a) と 図5(b) の不連続点は、コントローラとメモリ2 です。メモリ1 は単なる負荷なので不連続点ではありません。どちらも遠端を整合終端すると、他方は整合する必要がありません。図5(c) の不連続点は、コントローラとメモリ1 およびメモリ2 です。この場合は、1対2 伝送になります。コントローラとメモリ2 の両方を整合すると、両方の配線は純抵抗とみなすことができます。ただし時間遅れは考慮する必要があります。このように、どこを終端するかは、上記原則に基づけば解が見つかります。

問題の答え

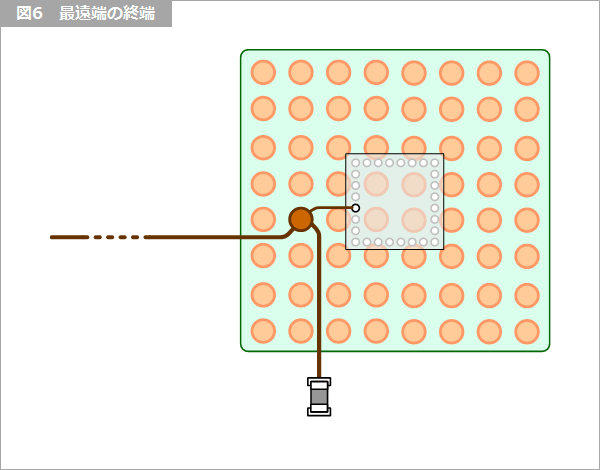

遠端終端は、最遠端のレシーバ端子に終端抵抗を配置するのでははなく、「最遠端」に終端抵抗を接続することを意味します。「最遠端」に終端を配置するスペースがないなら、作り出せばよいわけです。すなわち、レシーバから、配線しやすいところを選んで、空き地のあるところまで配線を延長して、終端抵抗に接続すればよいわけです。

本コラムの『終端抵抗とは ~その2』の 図2(b) に示すように、遠端終端は線路上の全ての位置で波形乱れがありません。したがって、新たに、「最遠端」を作り出せば、その線路上は、どの場所でも波形乱れがありません。ただ、一つ注意していただきたいのは、この方法は、遠端整合終端の場合だけ有効です。完全に整合しない場合には、新たに「最遠端」を作り出しても、途中は波形乱れが生じるので注意が必要です。

AC カップルの位置

少し話題がそれますが、線路の途中にキャパシタを挿入して、直流分をカットする場合があります。よく、このキャパシタは線路のどこに入れるべきか...という質問を受けます。これは、上に述べたことをよく考えればよいわけです。すなわち、遠端終端は線路上の全ての位置で波形乱れがない、それならば、遠端には極力整合を妨げるようなものを配置しない、すわなち、遠端を避けることが必要です。一般的にはトランスミッター側に配置します。

碓井有三のスペシャリストコラムとは?

基礎の基礎といったレベルから入って、いまさら聞けないようなテーマや初心者向けのテーマ、さらには少し高級なレベルまでを含め、できる限り分かりやすく噛み砕いて述べている連載コラムです。

もしかしたら、他にも気になるテーマがあるかも知れませんよ!