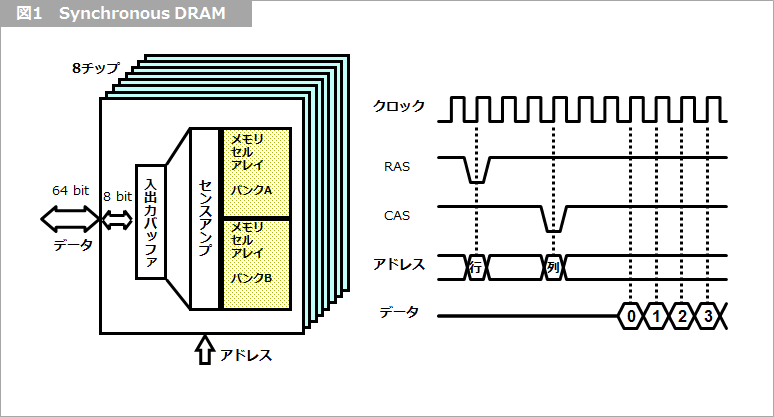

メモリの使用量の増加に伴って、非同期型 DRAM の限界に対応するために 図1 に示す SDRAM が登場しました。通常の論理回路と同じようにクロック同期型となって、ボード設計が楽になりました。

メモリの特殊性が薄れて、普通の論理設計者がメモリ周りの設計をするようになったのもこの辺りからでした。最初の SDRAM は 66 MHz と、従来の非同期型 DRAM の 2倍の速度になりました。この後、すぐに 100 MHz、さらには 133 Mbps となり、メモリの高速化の競争が始まったわけです。

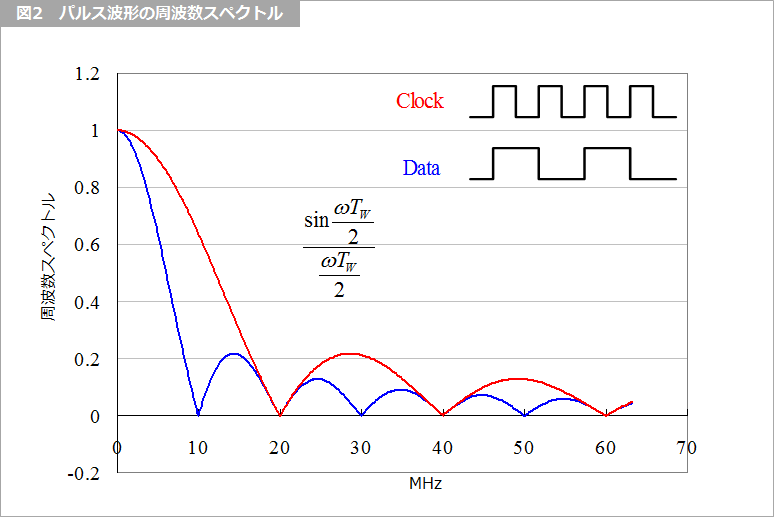

ところで、パルス波形の周波数成分は、パルス幅と立ち上がり時間とにより決定され、周波数成分はパルス幅に反比例します。ダブル・データ・レート(DDR)ではない一般的なクロック系の場合、データ信号の最小パルス幅はクロックのパルス幅の半分です。

図2 にクロックとデータの周波数スペクトルを示します。簡単のためにそれぞれのパルスの立ち上がり時間は 0(ゼロ)として求めています。

配線系が持つ周波数伝送能力がクロックもデータも同じとすると、データを倍、すなわちクロックと同じパルス幅で送る余裕があるわけです。このように、データ信号はクロックに比べて伝送系の性能の半分しか利用してないので、倍のデータを送って伝送系の帯域を有効に使おうというのが DDR の発想です。

クロック波形の立ち上がりと立ち下がりの両方のタイミングを使ってデータを取り込みます(脚注1)。この結果、単純にデータ・レートは倍になりました。

100 MHz のクロックで端子当たり 200 Mbps のデータ転送が実現しました。その後の転送速度の高速化はよくご存じのとおりです。DDR で 400 Mbps、DDR2 で 800 Mbps となり、DDR3 の 1600 Mbps を経て、DDR4 では何と 3200 Mbps まで計画されています(脚注2)。Direct Rambus が 800 Mbps で登場したときの驚きはすでに遠い過去のものになりました。なお、DDR に対して、従来の SDRAM を SDR (Single Data Rate) といって、DDR と区別することもあります。

この高速化を実現するために、インピーダンスを整合(Impedance Matching)させました。SDR SDRAMは、LVTTL の信号を非整合で使用していました。メモリ・バスは通常 64ビットですから、3.3 V 振幅のままインピーダンス整合すると消費電力が大きく増大します。これを回避するために、DDR では振幅を下げる試み、すなわち、小振幅の SSTL が導入されました。

SSTL とは、Stub Series Termination Logic の略で、基本は両終端の小振幅インターフェースであり、スタブにおける多重反射を回避するために、スタブ・シリーズ抵抗を設けます。SSTL_2 とか SSTL_1.8、さらにはSSTL_1.5 などの末尾の数字は、基本的には 2.5 V とか 1.8 V、1.5 V などの出力回路の電源電圧を示します。SSTL の原理については、『豆知識:SSTL~その1~』や『豆知識:SSTL~その2~』で詳しく述べます。

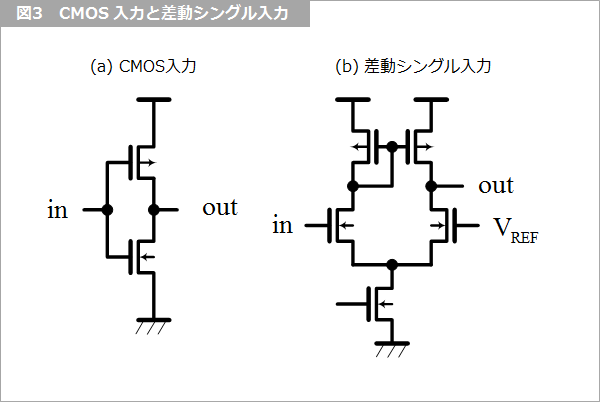

図3 に、従来の CMOS 入力と SSTL で用いられる差動シングル入力とを示します。SSTL で小振幅化を可能にしたのは、レシーバに基準電圧(VREF)を設けたことです。レシーバ回路は基本的に差動入力で、受信側と反対の入力に基準電圧を加えます。

従来の CMOS 回路はトーテムポール接続された、P チャネルと N チャネルの 2つのトランジスタのスレッショールド電圧の差でレシーバのスレッショールド電圧が決まるので、30 ~ 70 % というような広い不感帯が存在します。差動回路は、基準電圧にペア接続された 2つのトランジスタのバラツキが加わる程度なので、極めて狭い不感帯しか存在しません。

したがって、電圧振幅の全てが有効に使われるので、小さな振幅でも信号を伝えられます。小振幅化によって終端しても消費電力の増加は少ないので、基本的に整合終端とします。これによって、反射が抑制され、高速化が可能となります。さらに、同じ立ち上がり時間でも振幅が小さいので、スルー・レイト(Slew Rate)も小さくなり、同時スイッチング・ノイズなどの微分性のノイズ発生が抑制されます。

脚注1

実際には、メモリ内部の DLL (Delay Locked Loop) によって、クロック波形の立ち上がりと立ち下がりの両方に相当するタイミングを生成しなおしています。

脚注2

実際には、JEDEC で標準化されているこれらの転送速度よりも高速のものが製品化されています。例えば、DDR2 は実際にこれらの速度で動作するかどうかは別として、このコラムの執筆時点で 1200 Mbps の製品も現実に入手可能です。

おすすめ記事/資料はこちら

======================================

碓井有三のスペシャリストコラムとは?

基礎の基礎といったレベルから入って、いまさら聞けないようなテーマや初心者向けのテーマ、さらには少し高級なレベルまでを含め、できる限り分かりやすく噛み砕いて述べている連載コラムです。

もしかしたら、他にも気になるテーマがあるかも知れませんよ!

こちら から他のテーマのコラムも覗いてみてください。