ノイズを嫌うアプリケーションでは、スイッチング・レギュレーターを使用できないため、リニア・レギュレーターを使用します。その際、電位差が大きい場合や負荷の電流値が大きくなった場合、リニア・レギュレーターの発熱が問題となります。

従来の方法

ヒートシンクや筐体に熱を逃がす

大きな筐体で設計する際などは、TO-220 のパッケージのリニア・レギュレーターを使用して、発熱に関しては筐体に逃がしたり、図1 のような形で大きなヒートシンクをネジ止めで取り付けて効率的に放熱をおこなっていました。

最近は、筐体・基板の小型化が必要となり、ヒートシンクを利用できない場合などは、アプリケーション的に消費電力を抑えるように設計し、QFN パッケージなどを用いてボードへの放熱をおこなうことが多くなっています。

発熱を抑える方法

スイッチング・レギュレーターと低ドロップ LDO 構成

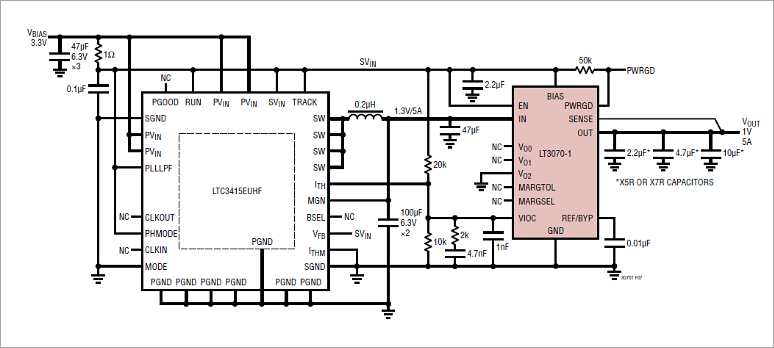

FPGA のコア電圧などのように、ボード上にスイッチング・レギュレーターを用いても良いですが、PLL 用の電源はローノイズにしたい場合もあります。

そのような場合には、一旦、スイッチング・レギュレーターで 5V や 3.3V などの低い電圧に落として、PLL 用の電源としては低ドロップタイプの LDO を用いることで発熱を抑えることが可能です。

アナログ・デバイセズ社の LT3070-1 は、ドロップ・アウト電圧(入力-出力の電圧差)が 85mV あれば、リニア・レギュレーターとして正常に動作します。図2 のように、前段で LTC3415 により 1.3V を作り、LT3070-1 にて 1.0V / 5A の出力を作る電源回路を構成することが可能です。

3.3V から直接 1.0V を作った場合には、パワーロス (Pd) は、11.5W [ (3.3V-1.0V) x5A ] となります。

LTC3415 を介して、1.3V から 1.0V を作った場合、パワーロス (Pd) は、1.5W となり 10W 電力損失を低減することにより、LT3070-1 の発熱を抑えることが可能です。

リニア・レギュレーターの並列接続による構成

スイッチング・レギュレーターを同一ボード上で使用できないようなシステムにおいては、先程の LT3070-1 のような回路構成は使用できません。

そのような場合は、リニア・レギュレーターの並列接続による構成を考える必要があります。

並列接続をおこなうためには、並列接続したリニア・レギュレーターの出力電流のバランスをとることが問題となります。出力電流のバランスを取るには、リニア・レギュレーターの出力に「バラスト抵抗」を使用する方法があります。一般的にバランスを良くするには、バラスト抵抗を大きくする必要がありますが、逆にロードレギュレーションが悪くなる副作用が有ります。このトレードオフの関係が、並列接続の設計の難易度をあげてしまいます。

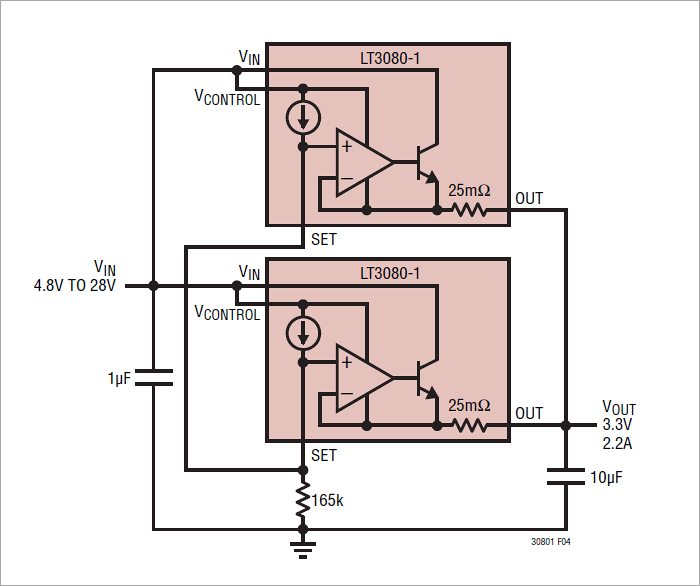

バラスト抵抗内蔵のLT3080-1

アナログ・デバイセズ社の LT3080-1 は、並列接続可能なリニア・レギュレーターです。

図3 に示すように、25mΩ のバラスト抵抗が内蔵されており、均等な電流分担が可能な設計になっています。

図3 は、2つの並列接続で 2A 出力となっていますが、並列接続を増やすことで更に出力電流を大きくすることが可能です。また、2A の負荷電流が必要な回路に対して、LT3080-1 を 2個→4個並列に増やした場合は、1個当たりの負荷電流の負担が 500mA と少なくなるため、発熱少なくなり放熱設計が楽になります。

リニア・レギュレータしか使えず、放熱設計に苦労されている方に最適なリニア・レギュレーターです。

関連情報

おすすめセミナー/ワークショップはこちら

おすすめ記事/資料はこちら

商品の購入はこちら

メーカーサイト/その他関連リンクはこちら

お問い合わせ

本記事に関してご質問などありましたら、以下よりお問い合わせください。

アナログ・デバイセズ メーカー情報Topへ

アナログ・デバイセズ メーカー情報Topに戻りたい方は、以下をクリックしてください。