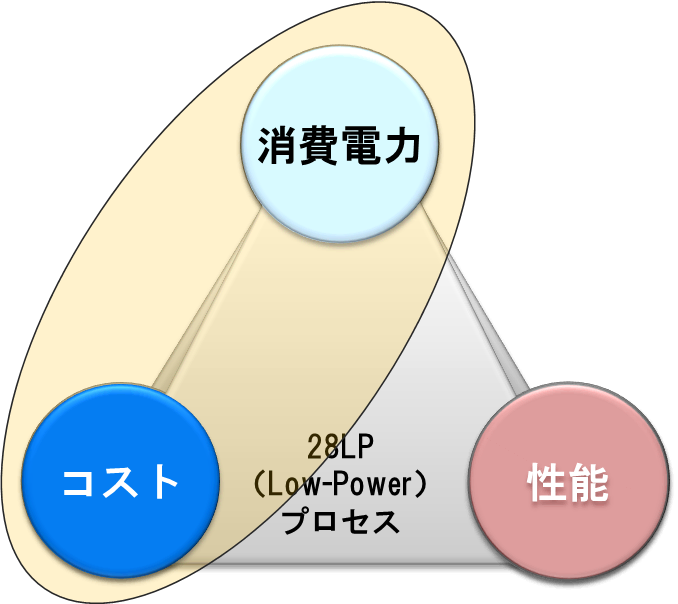

Intel 's Cyclone ® V SoC and Arria ® V SoC families are manufactured on TSMC's 28nm low power (28LP) process technology, realizing low power consumption, a rich set of hard IPs, and a low power serial interface. A transceiver can be used.

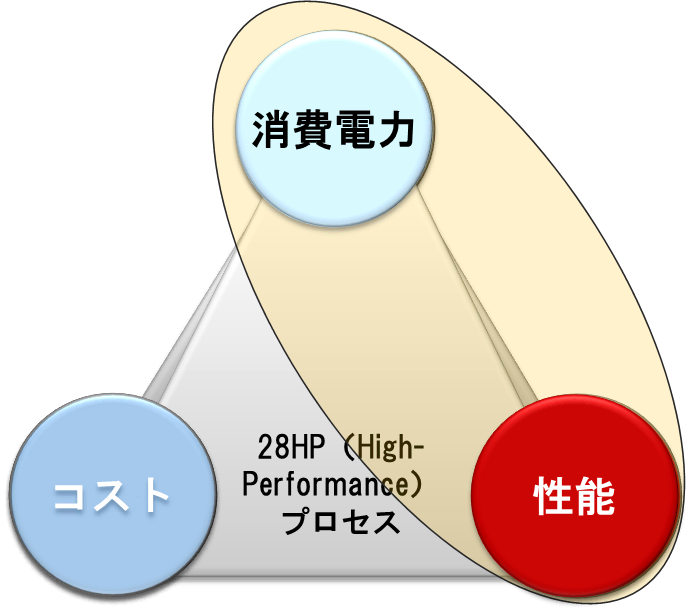

Process Options in the 28nm Portfolio

The Cyclone V SoC and Arria V SoC families are differentiated by optimizing for requirements such as performance, I/O resources, package size, power consumption, and cost. And it enables rapid design development with a productivity-enhancing design platform common to the 28nm device family.

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

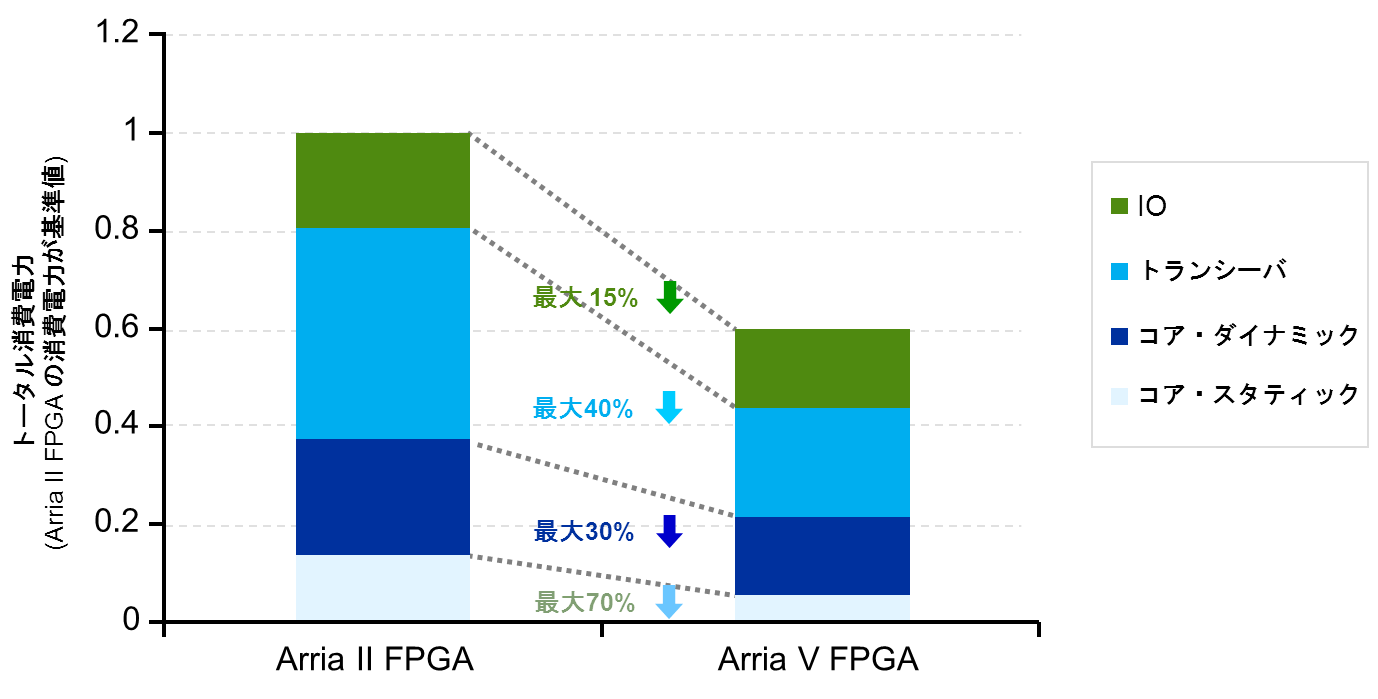

Achieved 40% lower power consumption with Arria V FPGA

Arria V SX and ST SoCs offer the industry's lowest total power consumption for midrange applications.

The adoption of the 28nm Low-Power (LP) process reduces dynamic power consumption, realizing the following benefits:

|

|

|

|

|

|

Compare Arria V FPGA Device Types

|

function |

|||||

|

Number of ALMs(K) |

170 |

190 |

190 |

174 |

174 |

|

Number of variable precisionDSPblocks |

1,139 |

1,156 |

1,156 |

1,068 |

1,068 |

|

Number of M20Kmemory blocks |

1,700 |

- |

- |

- |

- |

|

Number of M10Kmemory blocks |

- |

2,414 |

2,414 |

2,282 |

2,282 |

|

DDR3memory interface speed |

800MHz |

667MHz |

667MHz |

667MHz |

667MHz |

|

hard memory controller |

- |

4 |

4 |

4 |

4 |

|

Transceiver speed(Gbps) |

12.5Gbps |

10.3125 |

6.5536 |

10.3125 |

6.5536 |

|

PCI Express® (PCIe) Gen3/2/1 HIPs |

1 |

- |

- |

- |

- |

|

PCIe Gen2/1 HIP |

- |

2 |

2 |

2 |

2 |

|

Design/Security |

|

|

|

|

|

|

SEUmitigation |

|

|

|

|

|

Arria V FPGA Architecture

|

・Lowest power consumption mid-range FPGA in the industry

Arria V GZ FPGAs have the lowest power per bandwidth for midrange applications and are ideal for power-conscious designs requiring transceivers up to 12.5 Gbps. Arria V GZ FPGAs consume less than 180 mW per channel at 10G and less than 200 mW at 12.5 Gbps. It also offers low static power products in -3L speed grade.

Arria V GX and GT FPGAs are designed for lowest static power consumption with 28nm Low-Power (LP) process, lowest transceiver power consumption at transceiver speeds up to 10.3125 Gbps, and dynamic power reduction It provides superior fabric with well-designed hard IP to achieve the lowest total power consumption for mid-range applications. Arria V devices deliver an average 40% power reduction over previous-generation midrange FPGAs.

・SoC FPGA – Customizable SoC based on ARM processor

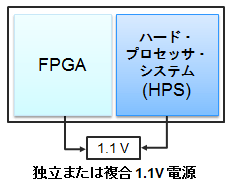

The Arria V SoC reduces system power, system cost, and board space reduction. The combination of HPS and Intel's 28nm low-power FPGA fabric offers the ecosystem and performance of application-class ARM processors with the flexibility of Arria V FPGAs and rich DSP blocks.

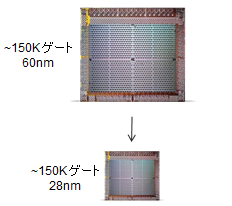

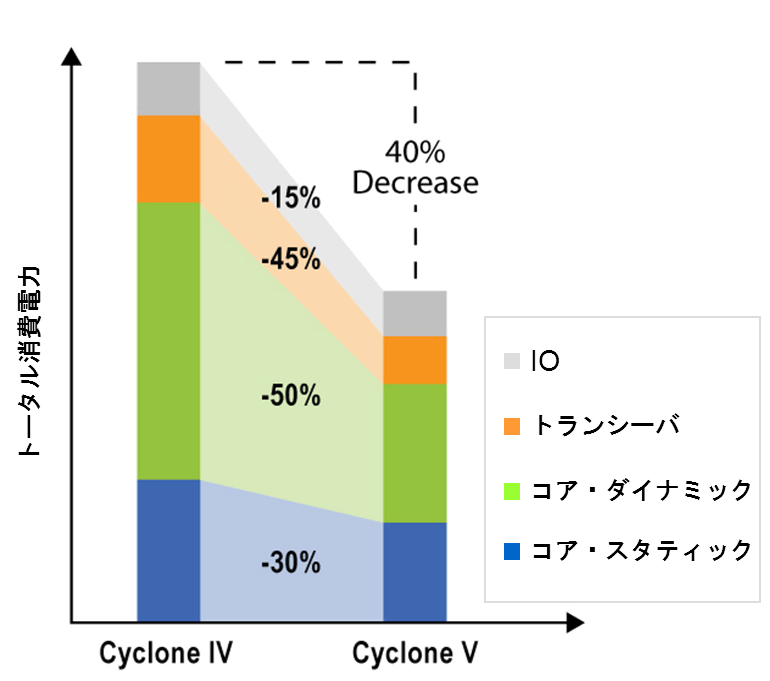

Up to 40% reduction in total power consumption even with Cyclone V FPGAs

Manufactured on TSMC's 28nm LP process, Cyclone V FPGAs deliver the performance demanded by cost-sensitive applications while reducing power and cost.

|

|

|

|

Advantages of 28nm LP: |

|

|

|

|

| |

|

|

|

|

| |

|

Cost savings also come from being able to operate with only two power regulator voltages and being offered in wire-bond packages, including small packages.

Cyclone V FPGA Family Offers Six Products

|

Features |

lowest cost and power consumption |

3.125G transceiver |

6.144G transceiver |

| Lowest system cost and power optimized FPGA for a wide range of logic and DSP intensive applications | Lowest cost and power FPGA optimized for 614Mbps to 3.125Gbps transceiver applications |

Industry's lowest cost, lowest power FPGA for 6.144Gbps transceiver applications (1) |

|

| FPGA | |||

| ARM Cortex™-A9 MPCore™ processor system |

(1)

Cyclone V GT devices support the 6.144 Gbps CPRI protocol.

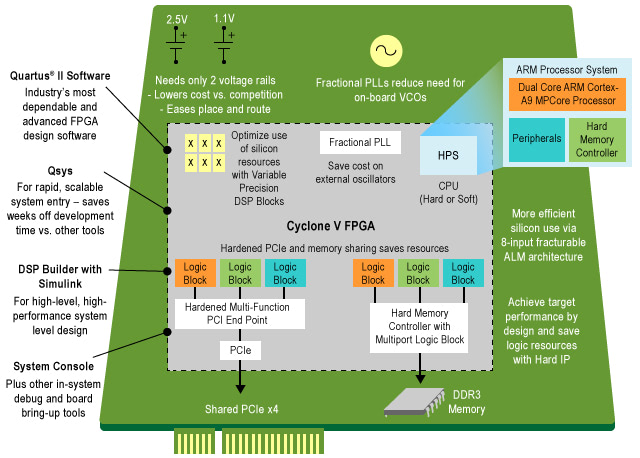

Cyclone V system integration reduces system-level costs

|

・Suitable for cost-sensitive mass production applications

Cyclone V FPGAs are ideal for high-volume applications such as protocol bridging, motor control drives, broadcast video converter/capture cards, and portable devices. Discover the benefits of Cyclone V FPGAs in various markets.

・Intel SoC – customizable ARM processor-based SoC

Cyclone V reduces system power consumption, system cost, and Provides board space reduction. The combination of HPS and Intel's 28nm low-power FPGA fabric offers application-class ARM® processor ecosystem and performance with the flexibility, low power, and low cost of Cyclone V FPGAs.

・Reduction of overall system cost through system integration

Cyclone V FPGAs include numerous hard IP blocks that allow you to differentiate your product while lowering overall system cost and power consumption, and shortening your design's time to market. The main hard IP blocks are:

|

A device that incorporates a lot of techniques for low power consumption

|

|

|

Intel SoC and 28nm Portfolio

When performance, power, and cost requirements conflict, there's no better solution than Intel's 28nm portfolio.

Offering a range of advantages, from broad functionality to application-focused solutions, Intel's 28nm portfolio takes programmable logic to new heights, delivering more complex and differentiated solutions in less time. and can be developed with less effort.