hello.

This is the ignorant ignorant who excluded the C language at the stage of course registration in college.

So far, I've learned a lot, and I've come up to step 3 of software design for production training.

![]()

This is the final chapter!

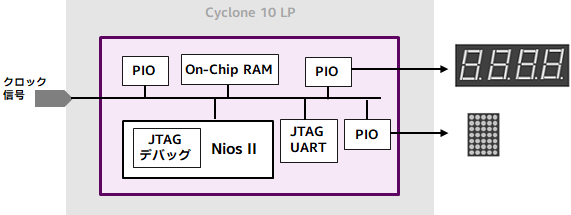

The circuit designed in step 2 is now designed in a "software language" using Intel 's Nios ® II soft core processor.

Well, will it be reproduced?

* first stage<Specifications/board creation>, Second stage <Hardware design> together withPlease look.

table of contents

・ Incorporating Nios® II into hardware design

・ Insert the Nios® II boot program into the configuration data

・ Things that were dangerous not to know

Incorporate Nios® II into your hardware design

A Nios ® II soft-core processor (hereafter referred to as Nios ® II) is embedded in order to execute a program written in C on an FPGA.

* For information on Nios ® II, see this content.

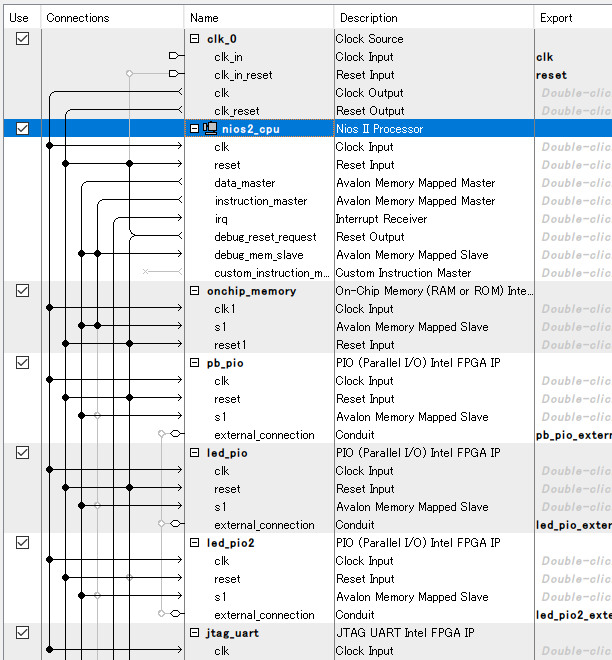

I launched Platform Designer from Quartus ® Prime and built the Nios II processor and the necessary modules and peripherals such as PIOs.

Designed in C

When it reaches 1 million μs (1s), go to the next loop

We design the C language to reproduce exactly the same behavior on Nios ® II as designed in Verilog HDL (hardware language).

So Ignorance Ignorance-kun searched for the materials used in the technical training so far.

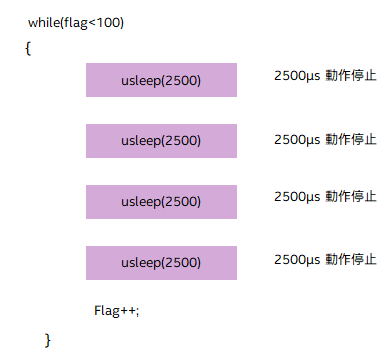

Then, I found that I could easily make a clock using the usleep() function.

I made 1 second using while statement and usleep() function.

In Verilog HDL, I made it based on the clock, but in C language, there is a function that can stop the operation in units of 1 second or 1 μs, which is very convenient!

This continues until 23:59:59 and returns to 0:00:00 after 1 second.

Put the Nios® II boot program into the configuration data

Using the Run Configuration function of the Quartus® Prime Nios® II Software Build Tools for Eclipse (hereafter referred to as Nios ® II SBT),

Ignorance ignorance-kun, who had created a C program and executed it on Nios ® II, thinking that it was completed.

A word from the seniors here.

"Oh yeah.

Put the Nios ® II boot program in the FPGA's on-chip memory.

So, make sure Nios® II can run when the FPGA boots. ”

![]()

After this I realized that what I was doing was "just debugging".

In other words, after writing the hardware to the FPGA, temporarily transfer the Nios® II program to on-chip memory,

I was just checking the initial operation.

Then the old man continued and left.

"Oh, it's on the web article~"

O help boat!

I immediately searched for the article that my senior told me The first L blinking on the Intel FPGA Nios II! Part 2 For reference.

As a result, just by supplying power to the FPGA, Nios II will execute the program written by ignorant ignorance, and it is now possible to operate the 7-segment LED and dot matrix LED on the expansion board☆

This saves the trouble of "downloading the software program after writing the hardware program".

(Certainly, I agree that if you have to do that every time, it won't be a product.)

That's it, you've completed Step 3.

in retrospect...

What I didn't know was crazy

1. How to incorporate Nios® II into hardware

The contents of the program executed by Nios ® II should be correct, but when I debug it on the Nios ® II SBT, "no response" occurs.

Even if you simply change the contents of the code, you can't see any change, ignorant ignorant petit panny! !

The factor is simply ignorance ignorance-kun's operation error.

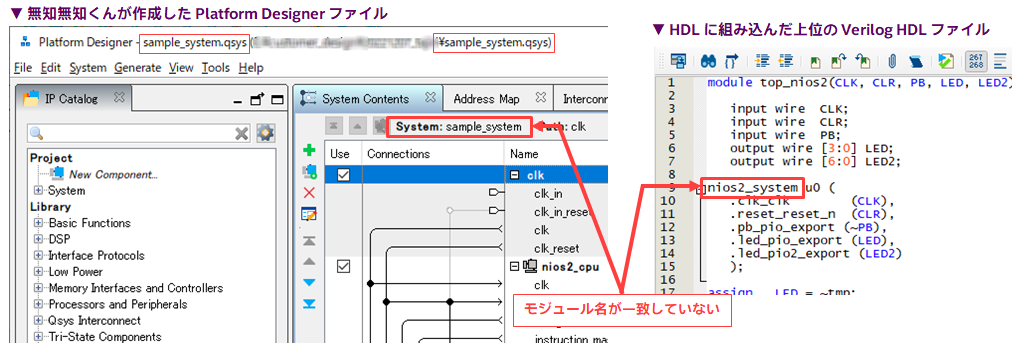

It was because the module names of the Nios ® II system design created in Platform Designer and the system embedded in Verikog HDL "mismatched".

Such discrepancies usually result in Quartus ® Prime compilation errors.

This time, I was enthusiastic about "using the sample design as a reference and applying it from there!"

This situation happened because I used the completed sample project as it was and built it while editing it.

Moreover, the software project created with the Nios ® II SBT was created with ignorant .sopcinfo files that were not incorporated into Verilog HDL, and the use of Quartus ® Prime was unclear, so it took extra time to investigate the cause. I spent it.

It would have been better if I hadn't used the sample project as is, but "just for reference".

Also, the consistency between the hardware design and the software seems to have been resolved by using the System ID Peripheral Intel FPGA IP.

(For an overview of the System ID Peripheral Intel FPGA IP, see here.)

Later, I was taught by seniors.

Senpai, I wanted to know as soon as possible.

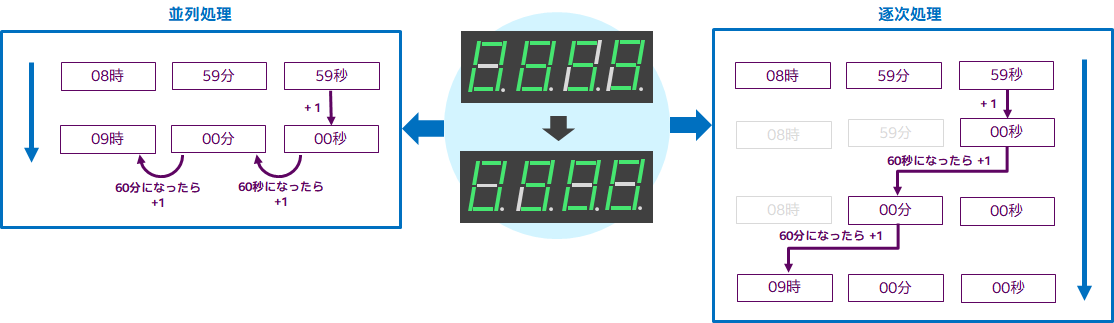

2. Processing differences between Verilog HDL and C language

Contrary to Poki-senpai who wrote a blog about sequential processing and parallel processing, Ignorance Ignorance-kun has become accustomed to Verilog HDL and has begun to understand the sense of parallel processing.

Verilog HDL non-blocking assignment is parallel processing, so you can write without worrying about the order,

Since the C language is a sequential process, the order of description is very important when describing loops inside { } and behavior when exiting.

It took me some time to get used to that rule.

for example

When designing a clock in a hardware language,

As shown in the lower left figure, <minutes> count up according to the value of <seconds>, and <hours> count up according to the value of <minutes>.

These actions (processes) are performed simultaneously.

On the other hand, in C language,

As shown in the lower right figure, the processing is performed one by one.

The amount of description is overwhelmingly small in the C language, but at first I was quite confused.

I think I've been muttering to myself over and over again, "Oh, it's processed in order from the top, isn't it?"

3. Interval Timer Intel FPGA IP

The Interval Timer Intel FPGA IP is

This IP is compatible with the Nios ® II processor HAL API Driver provided in Platform Designer.

(I learned about this after finishing the production training.)

This library has alt_ticks_per_second() It seems that there is a function called

A function that returns the number of system clock ticks that pass per second

I thought I could make a clock by applying it.

alt_alarm_start(),alt_alarm_stop() witha function

You can even add an alarm function to your watch without complicated descriptions! (maybe?)

It is a function that seems to be useful when making a clock.

In the usleep() function used in the actual design,

Because all processing stops for a specified time while it is running

It is difficult for ignorant ignorant to create code that allows parallel processing,

Abandoning complex displays on dot-matrix LEDs.

But with these functions

It might have been possible to project a different animation onto the dot-matrix LED while the clock was running.

I have regrets.

It's a loss if you don't know.

Good point

In the software design (Step 3), I kept in mind the points I had learned in Steps 1 and 2, so there were no outrageous failures.

However, there were some things that made me realize that I should have done this.

![]() It would have been better to understand the overall work flow and clarify what to do before proceeding.

It would have been better to understand the overall work flow and clarify what to do before proceeding.

There was a lack of research, such as checking the settings of various peripherals and what functions could be used in the code.

![]() I should have tried it first because there is content (such as exercises) that I can get a sense of in advance

I should have tried it first because there is content (such as exercises) that I can get a sense of in advance

Is that it? This line, like I said in step 2...

I understood that it was important to carefully set IP parameters and build the environment for Nios® II development during Step 2.

Learned again here in Step 3.

Problem caused by aerial wiring!

video will play

A few days before the production training presentation,

A situation occurred in which the 7-segment LED reacted just by lightly touching the push button or its surroundings!

This is due to the air wiring. yes.

Depending on the angle of the board and how you touch the button, it will work properly,

The wiring was extremely unstable.

"Stay alive until the presentation!"

If next year's new employee says, "Please show me your senior's expansion board in operation,"

I'm not sure if the board will be alive at that time. sorry!

![]()

at the end

The in-house presentation of production training ended successfully, and Ignorance and Ignorance took a deep breath.

What I learned in this practical training is useful for my current OJT.

During the practical training, I used to be Wakemo Wakaraz, but when I think about it now, there was no need for hard work!

Before the production practice, I had a question for my senior.

“How can I multitask at work?”

“There is no such thing as multitasking.

Concentrate on one by one and use the gap time. It only seems that way thanks to meticulous schedule management."

and seniors.

You are right!

I suddenly remember that now,

At the same time I thought it was like dynamic lighting.

I was ashamed of my past naivety of asking vague questions just because of the sound of the word "multitasking."

This concludes the 2022 New Graduate Employee Ignorance Ignorance's Struggle.

If you notice, a junior will join the company in a few months.

I will continue to do my best so that I can become a reliable ignorant ignorant paisen!