スカイワークス社 Si5338のメリット

4つの優れた特長

Si5338は様々な機能を1chipに集約させたプログラマブル可能なクロックジェネレーターです。ユーザーは優れた機能を簡単に利用することができ、また、多くのアプリケーション用途に使用することができます。ここでは特にユーザーにとって嬉しい特長を4つ、ご紹介します。

特長1. MultiSynth テクノロジーで0ppm精度周波数出力を実現

特長2. 4つの出力バンク毎に出力フォーマットと出力電圧の選択が可能

特長3. 4つの出力バンク毎に周波数と位相をダイナミックに調整可能

特長4. 4つの出力バンク毎にEMIを低減するスペクトラム拡散設定が可能

特長1.MultiSynth テクノロジー

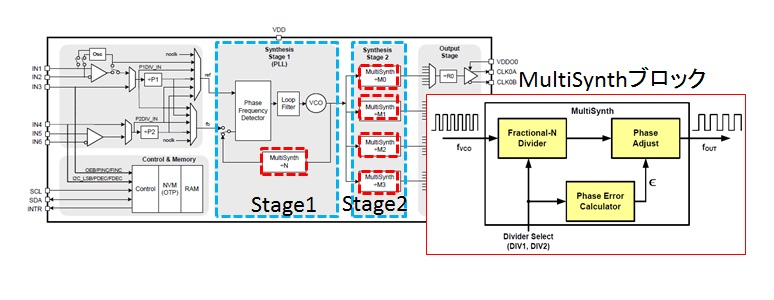

MultiSynthテクノロジーを使ったディバイダーは、「Synthesis Stage 1のPLL部VCOの出力フィードバック経路」と「Synthesis Stage 2で各出力バンク毎」に配置されています。MultiSynthテクノロジーによって、1つのPLLから4つの任意周波数を生成することができます。

Synthesis Stage 1では、2.2~2.84GHzの出力レンジをもつアナログPLLの高精度フィード・バック・ディバイダーに使用され、このレンジ内のあらゆる周波数生成が可能です。また一般的なフラクショナルN PLLに比較して低ジッター出力を実現しています。

Synthesis Stage 2では、バンク毎に配置されフラクショナル-N ディバイダーをベースに0ppmの正確なクロック出力を生成するために、2つの近似整数値の間をシームレスにスイッチします。

このプロセスによって生成されたフェーズ・エラーを除去するために、MultiSynthブロックは、フラクションナル-Nのディバイダーによって作り出されたクロックと要望の出力クロック間の相対位相差を計算し、理想的なクロック波形と一致させるためダイナミックにプロセスを調節します。この新しいアプローチは、ジッター性能を犠牲にせず、どんな出力クロック周波数も生成することを可能にします。

※一部、制約がありますので詳細はデータシートをご確認ください。

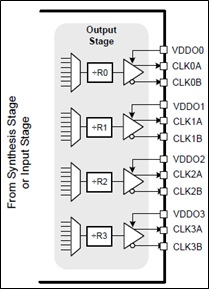

特長2.出力フォーマットと出力電圧

出力ステージは、出力セレクター、出力ディバイダー、プログラマブル出力ドライバーからなります。

出力ドライバーは、以下のフォーマットと出力周波数レンジをサポートしています。

・LVPECL/LVDS: 0.16 ~ 710MHz

・HCSL: 0.16 ~ 250MHz

・CMOS: 0.16 ~ 200MHz

・SSTL/HSTL: 0.16 ~ 350MHz

出力電圧ピン(VDDn)はバンク毎に独立しており、各フォーマットで要求される出力電圧として3.3V,2.5V,1.8Vの設定が可能です。また、PLLのロックが外れたときの出力を、High停止、Low停止、Hi-zに設定することもできます。I2Cポートから各ポートのイネーブル or ディスエーブルの制御をすることができます。

特長3.周波数と位相をダイナミックに調整

周波数調整(インクリメントとデクリメント)は、I2Cのポートからバンク毎に独立して調整が可能です。周波数アップ・ダウンのステップサイズは、レジスタへあらかじめ設定します。最小ステップ幅は1ppmです。

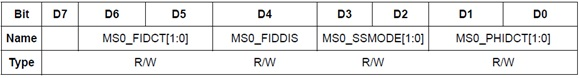

具体的にはI2CポートからMuliSynth0 Freq inc/dec_SS_Phase inc/dec Configurationレジスタ(Address 52)のBit4 MS0_FIDDIS = 0 (Frequency inc/dec enable)とした後、bit[6:5]MS0_FIDCTに10bをライトすることで周波数のインクリメント、11bをライトすることでデクリメントが設定されたステップ幅で実行できます。MultiSynth0 ~ MultiSynth3それぞれが同コントロールレジスタを持ち、各々固有の設定ならび周波数調整を行うことができます。周波数調整は、前述のSynthesis Stage 2内MultiSynth ディバイダーを使用するため最大の出力周波数はFvco/8 MHzで最小は5MHzです。

以下にレジスタ52のレジスタ・フィールドを示します。

位相調整(インクリメントとデクリメント)は、レジスタにより1) 初期位相オフセット値 2)位相インクリメント・デクリメントのステップ幅を設定することができます。位相調整幅は、±45nsecで最小ステップ幅は20psecです。周波数調整と同様に、レジスタ25のbit[1:0]MS0_PHIDCに10bをライトすることで位相のインクリメント、11bをライトすることでデクリメントが設定されたステップ幅で実行できます。MultiSynth0 ~ MultiSynth3全てに固有の設定、調整ができます。

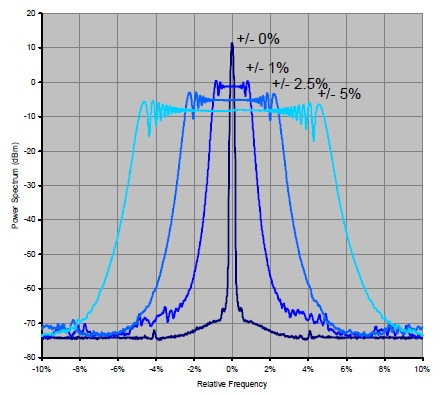

特長4.スペクトラム拡散

電磁波輻射(EMI)のピークを低減するため、4バンク全てにおいてスペクトラム拡散変調をサポートしています。スペクトラム拡散変調は、独自機能であるMultiSynth技術を使用して実現しています。

1) スペクトラム拡散変調は、5MHz ~ 350MHzのあらゆる周波数出力で実行可能

2) スプレッド幅 ダウン・スプレッド -0.1% ~ -5.0%、センター・スプレッド ±0.1% ~ ±2.5%

3) 変調周波数 33 ~ 63kHz

Si5338使用例

Si5338はクロックジェネレーターと呼ばれる製品です。クロックと聞いて水晶振動子(X’tal)や水晶発振器(XO)を思い浮かべる方が多いかと思いますが、クロックジェネレーターは、振動子や発振器などのクロック源から任意の周波数を生成することができる製品です。クロックジェネレーター以外に、クロックバッファーと呼ばれるクロック源を分配する製品、クロック源のジッターを低減させるジッターアッテネーターと呼ばれる製品などがありますが、いずれもクロック源が必要です。

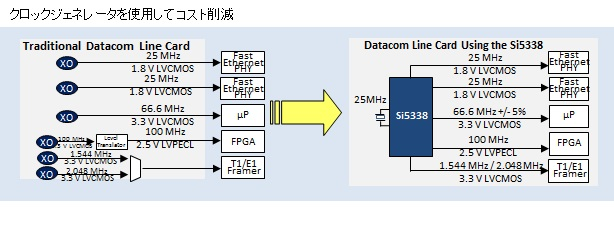

次にクロックジェネレーターを使用するメリットについてお話しします。システム上ではMPU、FPGA、高速伝送プロトコル等々、異なる周波数や出力フォーマットでクロックを供給することが要求されます。通常、左の図の様に発振器など使用し個々のデバイスにクロックを供給します。この例では6つの水晶発振器(XO)に加え、信号レベル変換ICとクロックを切り替えるセレクターが必要です。一方、右の図はSi5338を使用し水晶発振器を置き換えた例です。複数必要であったデバイスが水晶振動子 + Si5338の構成で置換えできます。この様にクロックジェネレーターを使用すれば部品点数を削減し実装面積縮小に貢献します。また、一般的に発振器は高周波数や出力フォーマットによっては価格が大幅に上昇しますので、クロックジェネレーターを使用してトータルコストも抑えることが可能です。

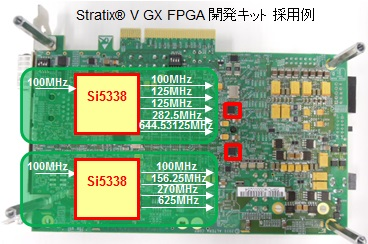

Si5338はFPGA 開発キット にも採用されています。実際にはこの様に使われます。

以上、Si5338の特長をご紹介しましたが、次回、専用ツール(ClockBuilder)を使用し詳しく説明します。

Si5338記事

FPGAにも最適な超高精度クロックジェネレーター Si5338

使いやすい設計サポートツール ~高精度クロックジェネレーター Si5338~

アルテラ Nios® IIでSi5338を自在にプログラム

お問い合わせ

本製品に関して質問などありましたら、以下よりお問い合わせください。

スカイワークス社 メーカー情報Topへ

スカイワークス社のメーカー情報Topページに戻りたい方は以下をクリックください。