HyperLynx DRC は、問題を引き起こしそうな PCB 設計個所を特定してくれるデザイン・ルール・チェッカーです。デザイン・チェックを自動化して、検証工数を削減できます。

本製品のセミナーを定期開催しています。参加申込は こちら から!

紹介動画

<環境構築>

HyperLynx のダウンロードやインストールは、こちらを参考にしてください。

▶ Siemens EDA ツールのダウンロード方法

▶ HyperLynx のインストール方法

<評価ライセンスの申請>

ライセンスをお持ちでない方で、実際に HyperLynx DRC を使ってみたい方は、弊社まで評価ライセンスの発行をリクエストしてください。

▶ お問い合わせ(評価ライセンスのリクエスト)など

「評価ライセンスを希望」とお書きください。担当者から、連絡させていただきます。

機能概要

HyperLynx DRC は、CAD ツールなどの PCB レイアウト・システムから生成されたファイルをインポートし、基本的なデザイン・ルール・チェックだけではなく、EMI / EMC 問題を回避させるためのデザイン・ルール・チェックも実行できます。目視によるチェック・ミスを防ぎ、設計担当者の経験や知見に左右されないため、チェック精度の向上とチェック時間の大幅な短縮を実現できます。

以下のような流れで、デザイン・ルール・チェックを実行して、結果を確認することができます。エラーがあった場合はエラーの原因を取り除き、このループを繰り返すことでデザイン精度を高めていきます。

① ボード・レイアウト

② デザイン・ファイルを HyperLynx DRC へインポート

③ デザイン・ルール・チェック

④ 結果をレポート

⑤ エラーをレイアウトに反映して修正

<HyperLynx DRC 製品ラインナップ>

HyperLynx DRC には、使用可能なデザイン・ルール・チェックが異なる 4つの製品ラインナップがあります。なお、HyperLynx DRC 301 はユーザーが作成したカスタム・ルールによるデザイン・ルール・チェックを実行することもできます。

● HyperLynx DRC PE

● HyperLynx DRC 101

● HyperLynx DRC 301

● HyperLynx DRC 401

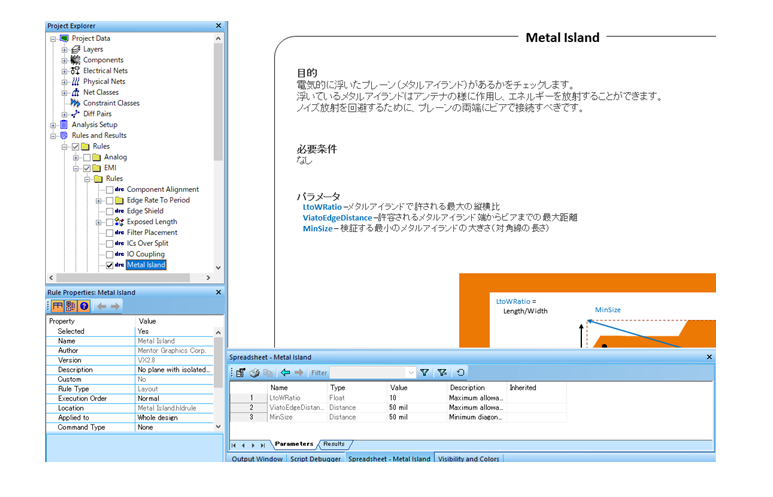

HyperLynx DRC には予め多くの標準ルールが搭載されており、デザイン・ルール・チェックを容易におこなうための機能をサポートしています。

製品ごとの対応ルールについては、以下をご覧ください。

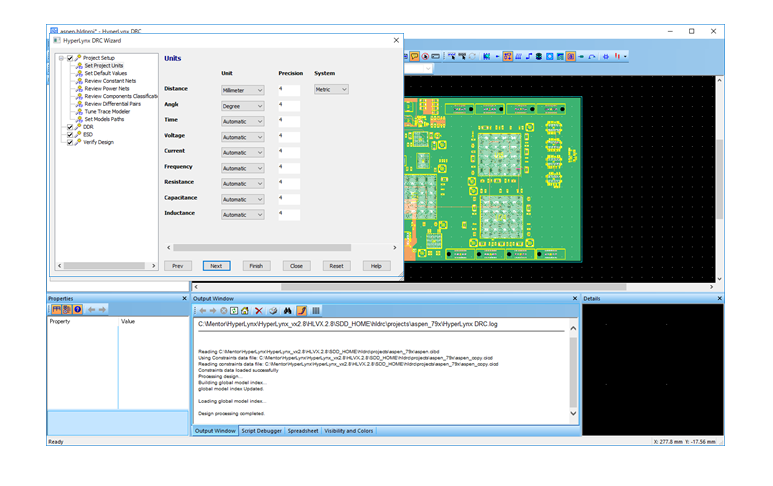

起動とプロジェクトの設定

ボードのデザイン・データを開いて、デザイン・ルール・チェックを行うための各種設定をおこないます。

デザイン・データの検証

デザインをロードした後、HyperLynx DRC が設計データを正しく認識しているかどうかを確認することが重要です。設計コンポーネントやスタックアップ・データを正しく認識していることを確認します。

オブジェクト・リストの内容が正しくない場合、ルールは正確な結果を生成できません。

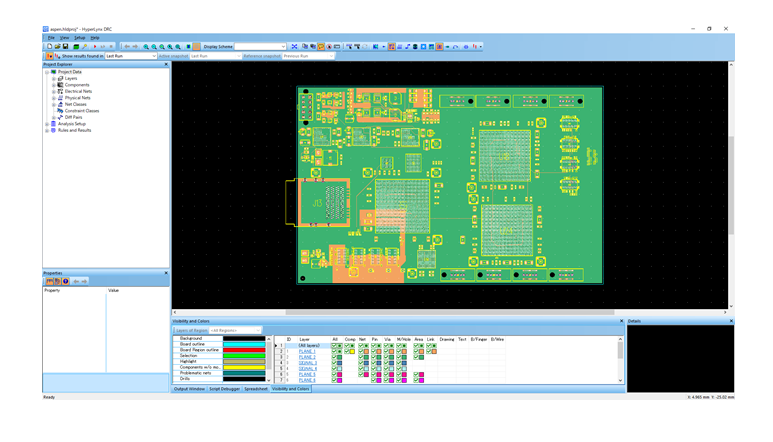

デザイン・ルール・チェックの実行

膨大な数の違反(疑似エラー等)を避けるために、実行するルールの数や範囲を制限することが大切です。その後、ルールを徐々に追加していき、その範囲を拡大させていくようにします。

つまり、デザイン・ルール・チェックを実行する対象と内容が適切かどうかを実行前に確認する事が重要で、対象と内容を適切に指定(制限)しないと、膨大な疑似エラーが発生してしまいます。

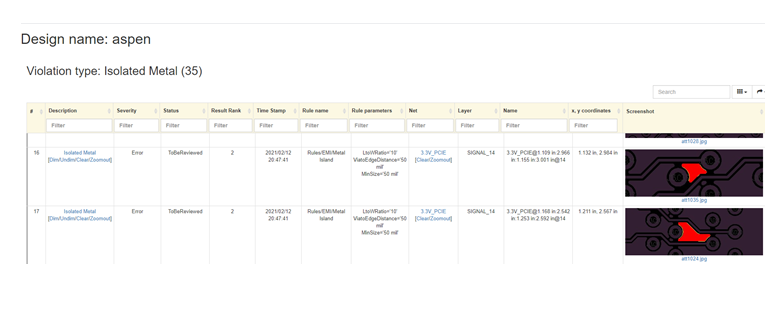

ルール違反のドキュメント化

デザイン・ルール・チェック実行後に、その結果を保存したり、簡単にドキュメント化することもできます。

また、CSV 形式で出力することで、サード・パーティーのツールでも活用しやすくなります。ShareList をエクスポートも可能です。

関連情報

セミナー/ワークショップ

改版ゼロを目指す、FPGA 基板設計手法

基板検図の短時間化とエンジニアの負担軽減

▶ Siemens EDA セミナー

お問い合わせ

本記事に関してご質問がありましたら、以下より問い合わせください。

メーカー情報 Top へ

メーカー情報 Top ページへ戻りたい方は、以下をクリックください。

シーメンス(Siemens)が所有する商標や登録商標:こちら