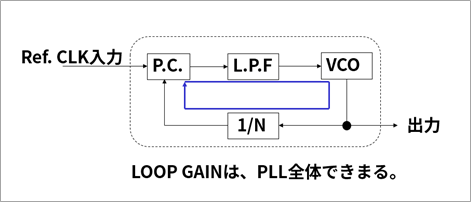

閉ループゲイン

PLLは、定常位相誤差を持つと前述しましたが、定常位相誤差はPLLの閉ループのトータルゲインで変化します。PLLは、青線で示すように負帰還回路で構成されます。トータルゲインは各ブロックのゲインの乗算となります。

P.C.:位相比較情報を電圧値に変化するゲイン

L.P.F:アクティブFilterの場合、オペアンプのゲイン

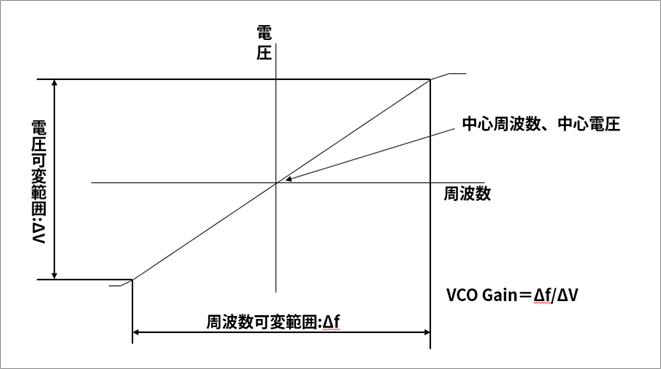

VCO:電圧/周波数変換効率(Δf/電圧可変範囲)

1/N分周器:ゲインはReference Clockを使用するのと比べて1/Nになる

このTotal Gainは、PLLの定常位相誤差と大きくかかわります。Total Gainが高ければ位相誤差も小さくなり、低ければ位相誤差が大きくなってしまいます。また、Total GainはReference Clockに重畳されるJitterも増幅してしまいますので、Jitterをどれだけ抑えられるか高次LPFの特性も考慮しなければなりません。システムの仕様に対して、どの要素を重視するかによって、Gain、FilterのCut Off等を考える必要があります。

お問い合わせ

本記事に関してご質問がありましたら、以下より問い合わせください。

Microchip メーカー情報Topへ

Microchipメーカー情報Topページへ戻りたい方は、以下をクリックください。