~無限の可能性を持つソフトコアCPUの世界へようこそ~

はじめに

前回は市販マイコンの課題と、それを解決するソリューションとしてのソフトコアCPUについてお話ししました。今回はCPU搭載FPGAの設計をどの様なスタイルで行うのか、そしてNios® IIの使用においてアルテラ社製ツールの対応について解説します。

ソフトコアCPU搭載FPGAの設計フロー

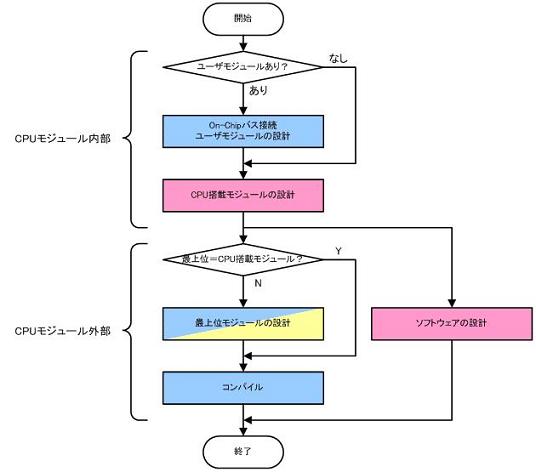

図1にソフトコアCPU搭載FPGAの設計フローを示します。デバイス全体から見た場合、設計対象がCPU搭載モジュール内部と外部で手順が2分されます。色分けは次に説明する設計ツールに対応しています。市販CPU-IPの場合はフローが異なる場合もありますので、今回は種々のツールサポートがあるFPGAデバイスベンダー製CPUを採用する場合として考えて下さい。以下、図で示した順番に解説していきます。

図1 ソフトコアCPU搭載FPGAの設計フロー

![]() On-Chipバス接続ユーザモジュールの設計

On-Chipバス接続ユーザモジュールの設計

突然深い話に入ったという印象を持たれるかもしれませんが、“ブロックレベルの上位設計においてオンチップのCPUバスにユーザモジュールを直接接続する様に設計する”という単純な話です。

FPGAデバイスベンダー製のソフトコアCPUには、CPU本体だけでなくタイマー、I/Oポート、外部メモリインターフェイス等の周辺モジュールがあらかじめOn-Chipバスに直接接続可能な形で提供されております。

これらを組み合わせるだけでも一般的な用途には十分対応できますが、FPGAによる「ユーザオリエントなSoC」をめざす皆さんは、やはりユーザモジュールをOn-Chipバス接続で組み込みたくなるのではないでしょうか。

FPGAデバイスベンダーのツールも当然ユーザモジュールのOn-Chipバス接続をサポートしているので、接続信号の仕様が理解できれば一般的な使い方であれば組み込むのは難しくないでしょう。ここで一般的な使い方と書いたのは、設計したユーザモジュールが、CPUからアクセスされるだけのスレーブモジュール(バスマスタ機能は持たない)で、アクセスも単純な非同期リード/ライトである場合を示します。FPGAデバイスベンダーのOn-Chipバスはシステム性能を高めるために様々な工夫がなされているので、On-Chipバスに特化した高速アクセスプロトコルや、バスマスタを組み込もうとするには、マイコンシステムに関する知識とそれなりの経験が必要になります。

正直申し上げて、私はソフトコアCPUを初めて使う方に対しては、On-Chipバス接続のユーザモジュールの使用をお勧めしていません。

その理由はツールに不慣れな状況で新しい機能を色々使ってしまうと、不具合発生時の原因解析に多くの時間を要してしまう場合があるからです。まずは不確定要素を極力少なくした範囲でとにかく慣れることが、早期に立ち上がる1つのコツだと思います。

![]() CPU搭載モジュールの設計

CPU搭載モジュールの設計

前述のユーザモジュールの有無とは無関係に、FPGAデバイスベンダー提供のツールを使ってCPUを搭載したモジュールを設計します。実際の作業はCPUや周辺モジュール毎に固有のパラメータと、モジュール間接続に必要な設定を行いながら1モジュールずつ組み込んで行くというものです。 CPU(広い意味ではバスマスタ+On-Chipバス)搭載専用と位置づけられるこのツールの使い勝手が設計効率を左右するので、各社共工夫を凝らしています。

![]() 最上位モジュールの設計

最上位モジュールの設計

後で解説しますが、CPU搭載モジュールの設計ツールは、周辺モジュールも含んだ自分の最上位階層をHDL(Hardware Description Language)で出力するので、その記述をそのままFPGAプロジェクトの最上位階層として使用することができます。

しかしアプリケーションによっては、CPUから直接制御されないモジュール(図 1のフローには含めていません)や、On-Chipバスと直結できないIP等をFPGAに組み込む事も多いと思います。その場合はCPU搭載モジュールと他のモジュールを含めた更に1つ上位の階層を、HDLもしくは回路図を用いて自分で設計する必要があります。

HDL設計が主流となっている現在で今更回路図?と、思われるかもしれません。

確かにデバイス非依存の設計にHDLのみの設計は有効ですが、FPGAデバイスベンダー提供のソフトコアCPUを使いながらベンダー非依存と言うことは考えられません。それに今回は本質から外れるので説明はしませんが、最上位階層を回路図で設計しておいた方が以降の作業で色々メリットがあるので、私はCPUモジュールのみの場合でも、可能な限り回路図の階層を追加しています。

![]() コンパイル

コンパイル

論理合成、配置配線、タイミング解析およびコンフィギュレーションデータ作成など、FPGAデバイスベンダー提供のツールを使用した通常の設計作業です。

![]() ソフトウェア設計

ソフトウェア設計

CPUはソフトウェアがなければ機能しません。そこで設計したCPUモジュールに応じて必要なソフトウェア(初期化プログラム、デバイスドライバ、ライブラリ、OS、ミドルウェア、アプリケーション等)の設計が必要です。FPGAデバイスベンダー提供のCPUの多くはオリジナル設計なので、WindowsやLinuxのOS上で動作するGNU(GNU is Not Unix)ベースのクロス開発環境を提供しています。

市販マイコンとは異なり、メモリや周辺モジュールのアドレス配置や割り込みも任意となるCPU搭載FPGAでは、初期化プログラムやデバイスドライバ等、俗にファームウェアと呼ばれるハードウェア寄りのソフトウェアは設計毎に準備する必要があります。つまりCPU搭載モジュール設計ツールの使い勝手と同様に、CPUユーザが設計したCPUモジュールに対して、一品一様で面倒くさいが必要不可欠なソフトウェア設計をどこまでサポートしてくれるかも、ソフトコアCPU採用の大きな判断要素となる訳です。

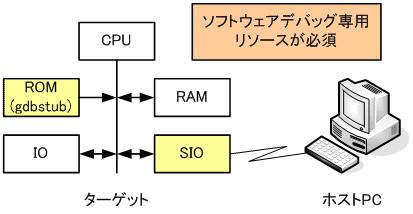

またICE(In Circuit Emulator)のサポートも重要です。GNUベースのデバッグでは、ターゲット側にgdbstubというモニタプログラムをターゲット側のROMに書き込みます。そして、CPUのソフトウェア割り込み命令を利用すると共にシリアルポートでホストPCと通信してデバッグを行うのが一般的です(図2参照)。

しかしこの方法は、命令の入れ替えを行うためデバッグ対象のソフトウェアがRAM上になければならないことや、デバッグ専用のシリアルポートが必要なこと等、汎用的ではあるものの制約があります。

一方On-Chipデバッガとも呼ばれるICEは、FPGAのコンフィギュレーションで使用するJTAG(Joint Test Action Group)ポートを介して通信するので専用のシリアルポートを必要としません(図3参照)。またOn-Chipデバッガの機能次第ではROM上で実行されるソフトウェアのデバッグも可能で、最終製品と同等のリソースでデバッグする事ができます。

図2 gdbstubによるソフトウェアデバッグ環境

図3 ICEによるソフトウェアデバッグ環境

Nios II を搭載する際に使用する設計環境

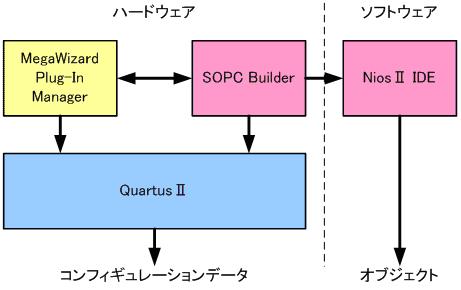

図4にNios IIを搭載する際に使用する設計環境を示します。各機能の色分けは図1のフローに対応しています。Quartus® IIには効率よく設計するために多くのサポート機能が搭載されており、MegaWizard Plug-In Managerは、回路図で設計する際に使用するマクロライブラリの管理ツールです。

Nios IIはCPUですので、ハードウェアだけでなくソフトウェアの設計ツールも必要ですが、アルテラ社はその全てを提供しています。以下、Nios II搭載FPGAの設計に必要なツールについて解説します。

図4 Nios II の設計環境

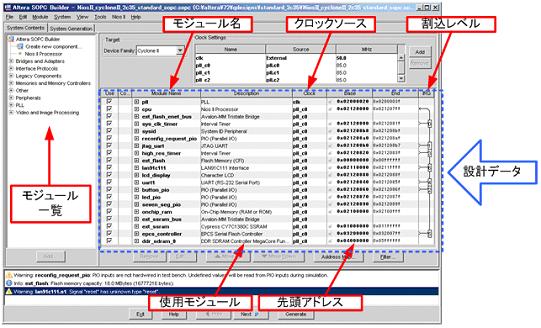

Nios II搭載モジュールの設計ツールです。Nios II、標準提供の周辺モジュール、およびユーザモジュールの選択、アドレスや割り込みレベル設定など一切を管理し、論理の自動生成まで行います。少し前のバージョンからQuartus IIに標準添付されているので名前だけは知っていても、Nios IIを使わないので起動したことがないという方も多いのではないでしょうか。

図5に現在販売されているNios II開発キットCyclone IIエディションでのSOPC Builderの設定画面を示します。画面の都合で各モジュールの接続は表示していません。勿論初めて起動した時は青線で示した設計データ部は空で、左側にあるモジュール一覧から機能モジュールを呼び出し、それぞれのモジュールに固有のパラメータを指定しながら追加していきます。Nios IIに関しては、CPUのタイプ(e/s/f)、デバッグモジュールの選択や、例外ベクタ配置のメモリリソース等を、スレーブモジュールに関しては固有パラメータ以外に、Nios IIから見た先頭アドレスと必要に応じて割込レベルを設定します。設計フローで開設したOn-Chipバス接続のユーザモジュールも、設計完了時点でモジュール登録しておくことで、標準提供のモジュールと同様に扱えます。必要な機能モジュールを全て呼び出して設定を行えば設計は終了し、後は”Generate”ボタンを押せば、CPUも含めた呼び出した全てのモジュール、モジュール間接続、および最上位記述が指定したHDLで出力されます。またQuartus IIの回路図エディタで呼び出せるシンボルも出力されるので、最上位階層を回路図で容易に作成することが可能です。

図5 SOPC Builderの例(Nios II開発キットCyclone IIエディション)

更にソフトウェア設計用に組み込んだモジュールに関する情報も出力するので、ソフトウェア設計も効率よく行えます。

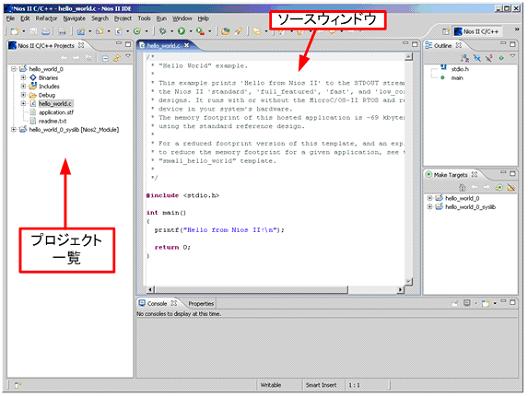

Nios II 用のソフトウェア開発環境で、GUIにはEclipseが採用され、コンパイラ、デバッガや標準ライブラリなど、ソフトウェア設計に必要なものが全て揃っています。図6にhello_worldのアプリケーションテンプレートでプロジェクトを作成した時のIDEの画面を示します。

図6 IDEの画面(hello_world)

ソフトウェア設計については次回以降で詳しく解説しますので、今回は紹介にとどめておきます。

おわりに

どうでしょう?

ソフトコアCPUを搭載したFPGA設計方法についてご理解頂けたでしょうか。CPUということで専用ツールのサポートはありますが、Nios IIもIPの一種ですので特殊な設計手法は不要なのです。また今回解説したアルテラ社製のツールは、フル機能版/無償版関係なく標準添付されていますので、直ぐにでも試してみることが可能です。各ツールの使用方法についてはアルテラ社提供のドキュメントを参照するか、もしくは販社の担当者に問い合わせしてみて下さい。また開発キットを入手すれば、サンプルデザインを使用したソフトウェアの評価まで簡単に行え、製品搭載のライセンスも入手できます。

高騰の一途をたどっている開発費を捻出できない小中量産機器メーカにとって、ソフトコアCPUとFPGAの組合せは「ユーザオリエントなSoCがミニマムオーダ1個から実現できる唯一の選択肢」なのです。

次回は、ハードウェアの実装事例についてご紹介する予定です。

~ソフトコアCPUの実装事例とそのポイント(1)~

◆浅井様のご紹介・連載タイトルはこちらから