Altera FPGA 向けのデザインを RTL レベルのファンクション・シミュレーションする場合、Quartus® Prime Pro Edition では NativeLink シミュレーションがサポートされていないため、今までは RTL シミュレーション用のスクリプト生成 & 編集 でおこなうフローをご紹介してきました。

しかし!

Quartus® Prime Pro Edition 24.1 以降のバージョンでは

新たに Run Simulation 機能がサポートされ、従来のフローと比べて 作業がさらに簡素化されました!

このページでは、Quartus® Prime Pro Edition ユーザー向けに

Run Simulaion 機能を活用した RTL レベルのファンクション・シミュレーションを実行する方法 をご紹介します。

このフローは、デザインに IP を含む・含まないに関係なく実行できる方法 で、とても便利ですよ。

なお 今回は、Questa* - Intel® FPGA Edition (以下、Questa - IFE という。Starter Edition を含む) をシミュレーターに用いてご案内します。

必要な事前準備

プロジェクトへデザインを登録

Quartus® Prime プロジェクトに、Quartus® Prime がコンパイル時に必要なデザインファイルを登録します。

IP デザインは、*.ip ファイルを登録します。

Project メニュー > Add/Remove Files in Project

IP 用のシミュレーション・モデル生成

[Notes] デザインに IP を含む場合にのみ 実施してください。

IP を RTL シミュレーションするには、IP 用のシミュレーション・モデルを生成しておく必要があります。

IP Catalog または Platform Designer で IP を作成する際に、Generate HDL 実行時にポップアップされる Generation ダイアログボックスにおいて、”Create simulation model オプション“ で言語を指定します。併せて シミュレーション実行用スクリプトを生成させるために対応ツールを選択します。

その後 Generate (または Generate HDL) ボタンをクリックすると、シミュレーション・ツール向けのファンクション・シミュレーション用モデルとスクリプトファイルが生成されます。

EDA ツールの実行プログラムのパス設定

① Tools メニュー > Options > EDA Tool Options をクリックします。

② Questa Intel FPGA 行 右端の [...] ボタンをクリックし、Questa-Intel FPGA Edition の実行プログラムが保存されているフォルダーを指定し、

Drectory Containing Tool Executable 欄に登録します。

例えば Windows OS であれば、questasim.exe が保存されている win64 フォルダーを指定してください。

Board and IP Settings

① Assignments メニュー > Settings > Board and IP Settings を選択します。

② 下記オプションを設定します。

・ Generate IP simulation model when generating IP オプション = On

・ シミュレーターの選択 (今回の例では QuetaSim)

シミュレーターの指定 / 言語指定

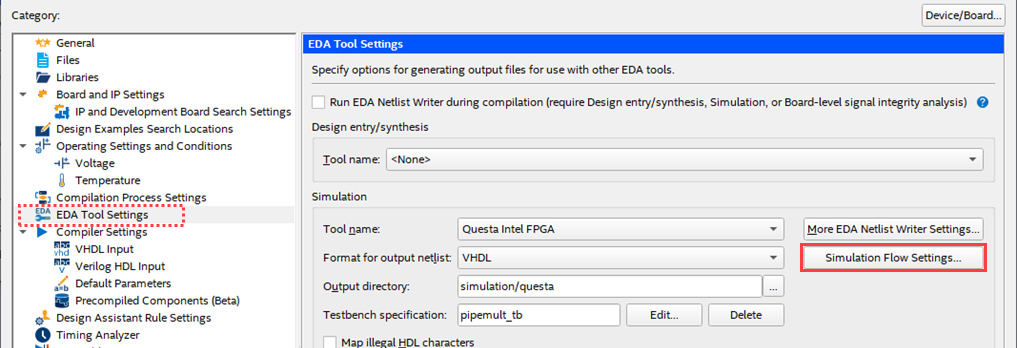

Assignments メニュー > Settings > EDA Tool Settings > Simulation において、以下の項目を選択します。

・ Tool name: 使用するシミュレーターツール (今回の例では Questa Intel FPGA を選択)

・ Format for output netlist: 使用する言語を選択

・ Output directory : simulation/questa (デフォルトのままを推奨)

テストベンチの登録

Assignments メニュー > Settings > EDA Tool Settings > Simulation 内の Testbench specification 欄 右横にある [New] ボタンをクリックし、

New Test Benches Settings ダイアログボックスにおいて、シミュレーションに使用するテストベンチファイルを登録します。

・ Test bench name

テストベンチのモジュール名を入力

・ Simulation period

シミュレーション実行の終了時間を設定

・ File name

右端の [...] ボタンをクリックし、テストベンチ・ファイルを選択。Add ボタンで登録。

Simulation Flow Settings

① Assignments メニュー > Settings > EDA Tool Settings > Simulation 内の Format for output netlist 欄 右横にある [Simulation Flow Settings] ボタンを

クリックします。

② 下記 2つのオプションをセットし、[OK] ボタンをクリックします。

・Command-line/batch mode = OFF

・Simulation scripts generation only = OFF

操作方法

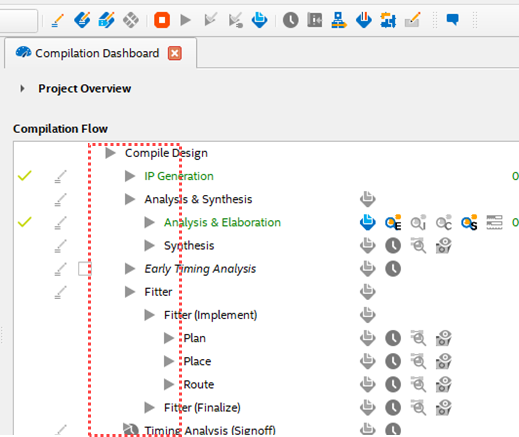

① Analysis & Elaboration 実行します。

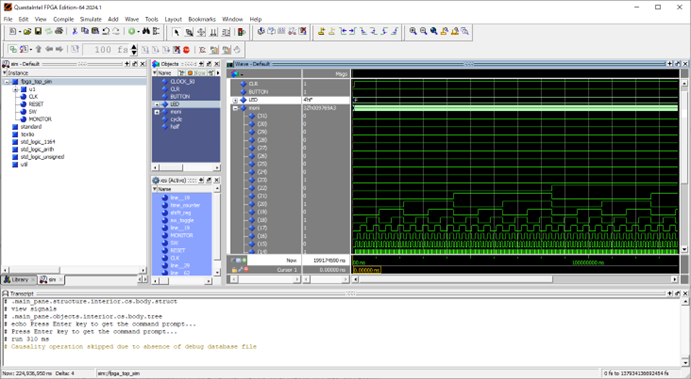

② View メニュー > Tcl Console ウィンドウを起動し、下記コマンドを入力し実行します。

execute_flow -simulation

Quetsa-Intel FPGA Edition の GUI が自動的に起動し、ソースやシミュレーション・モデルのコンパイルやライブラリー作成が実行されます。

その後、シミュレーションが実行され、Wave ウィンドウに波形が表示されます。

![]() みなさんもぜひ、Pro Edition の最新 Ver. を使用して、Run Simulation 機能でファンクション・シミュレーションを実施してみてくださいね。

みなさんもぜひ、Pro Edition の最新 Ver. を使用して、Run Simulation 機能でファンクション・シミュレーションを実施してみてくださいね。

補足事項

Run Simulation 機能は、シミュレーターの GUI を閉じないと Quartus® Prime のステータスが Done しないため、

シミュレーションの実行自体が Done していても、Quartus® Prime の Process (Synthesis や Fitter などの実行) はグレーアウトになり実行できません。

シミュレーターの GUI を閉じる、または Quartus® Prime の Processing メニュー > Stop Processing を実施して終了させてください。

もし、シミュレーターの起動や実行を Quartus® Prime のプロセス実行の一連フローに含ませたくない場合は、

上記 Simulation Flow Settings でご紹介した下記オプションを On にすることにより、スクリプトだけを生成させることができますよ。

・ Simulation scripts generation only = ON

これで、execute_flow –simulation 実行後 スクリプトやバッチファイルを生成して、Quartus® Prime のプロセスは終了します。

![]()

あとは、生成された do ファイルを別途シミュレーターで利用する、もしくはバッチファイル (.bat) / シェルスクリプト(.sh) を利用してシミュレーターを起動・実行してください。