※ この不具合は、以下の Quartus Prime で解消されています。詳細は、下記 FAQ をご覧ください。

・Intel® Quartus® Prime Standard Edition Software v21.1 and later

・Intel® Quartus® Prime Pro Edition Software v21.3 and later

上記バージョンよりも前の Programmer を使用するユーザーは、以下の方法で対応してください。

--------------------------------------------------------------------------------------------------------

こんにちは。

マクニカで Altera® FPGA 製品の技術サポートをしている アルテラ ハナコ です。

Cyclone® IV の EP4CE75 を使用しているユーザー必見!

FPGA 経由でコンフィグレーション ROM に jic ファイルを書き込む際に発生する不具合のワークアラウンドをご紹介します。

不具合の状況

以下の条件において、不具合が確認されています。

| Tool |

Quartus® II 13.1.4 以降 (Quartus Prime Standard Edition および Lite Edition を含む) |

| FPGA | EP4CE75 |

| 転送するファイル形式 | .jic |

| 実行内容 |

コンフィグレーション ROM に jic ファイルを転送するため、工場出荷時の Enhanced SFL image を使用して Program オプションを実行する.

<Programmer の GUI イメージ>

|

|

Programmer で 発生する エラーメッセージ |

Error (209025) Can't recognize silicon ID for device … |

不具合の要因

Quartus II 13.1.4 以降 および Quartus Prime の Programmer に装備された EP4CE75 用の Enhanced Serial Flash Loader (以下 Enhanced SFL) イメージに不具合があります。検証したところ、Quartus Prime Standard および Lite Edition の ver.20.1 でも改善されていませんでした。

回避策

EP4CE75 用の SFL IP を自作し、その sof ファイルで jic ファイルをコンフィグレーション ROM へ転送します。

作業手順は以下のとおりです。

- SFL IPを作成

- トップデザインに SFL IP をインプリメント

- 自作の SFL IP 用にタイミング制約を追加

- コンパイル

- EP4CE75 に sof ファイルをダウンロード

- jic ファイルをダウンロード

それでは、この作業内容をご案内します。

1. SFL IP を作成

Quartus Prime において、ワークアラウンド用のプロジェクトを新規作成し、ターゲットデバイスに EP4CE75 を選択します。

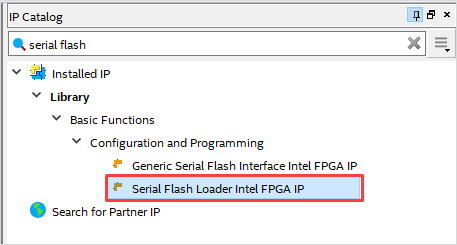

Tools メニュー > IP Catalog において、"Serial Flash Loader Intel FPGA IP" を選択します。

(ver.17.1 以前の Quartus Prime で作成する場合は、IP 名が Altera Serial Flash Loader IP です。)

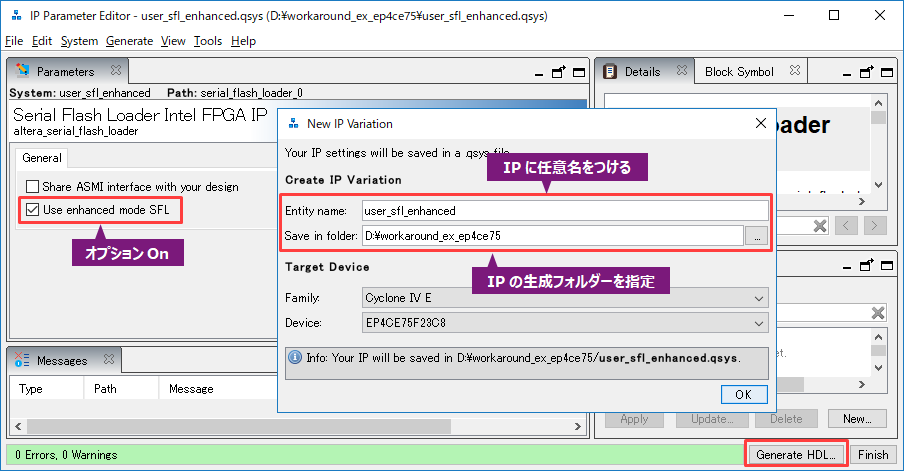

IP に対して任意名および生成するフォルダーを指定し、General タブにおいて以下のオプションを有効にします。

Use enhanced mode SFL = On

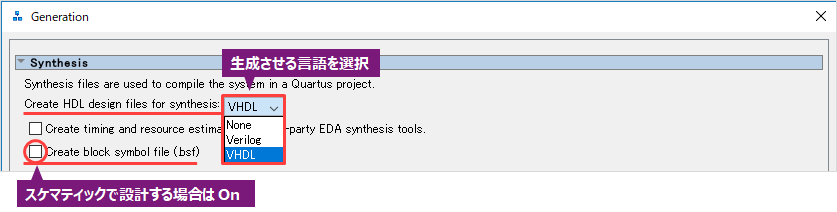

[Generate HDL] ボタンをクリックし、生成させる言語を指定します。

[Generate] ボタンをクリックし、SFL IP を生成します。

2. トップデザインに SFL IP をインプリメント

File メニュー > New により白紙のデザインファイルを開き、最上位デザインを作成します。

エンティティ名は任意です。

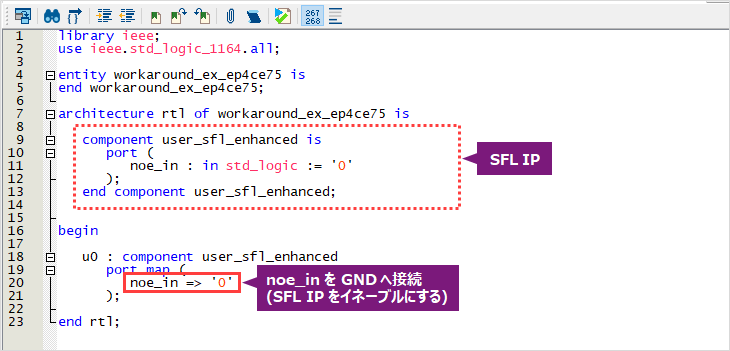

手順1 で作成した SFL IP を最上位デザインにインプリメントします。

(IP の生成されたフォルダー内にあるインスタンス用のテンプレートを活用すると便利です。)

SFL IP をイネーブルにするため、入力の noe_in ポートを GND へ接続します。

以下は、VHDL のデザイン例です。

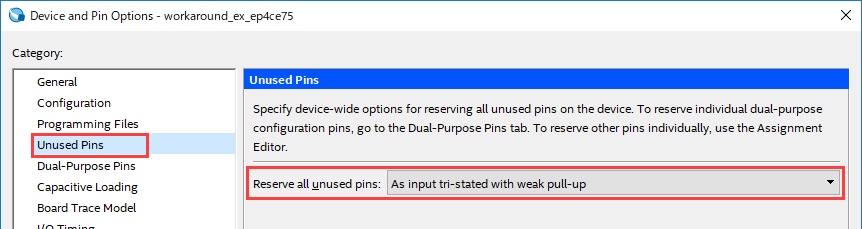

Assignments メニュー > Device > Device and Pin Options > Unused Pins を指定し

未使用ユーザー I/O ピンを以下のとおりに設定します。

Reserved all unused pins: As input tri-stated with weak pull-up

3. 自作の SFL IP 用にタイミング制約を追加

SFL IP に対してタイミング制約ファイル (.sdc) を作成します。

メーカーの Web ページ Knowledge Base で公開されている制約を参考にしてください。

##########

## 参考例

## デザイン、コンフィグレーション・デバイス、ボードのトレース長に応じて信号名、パス、タイミングを変更する必要があります。

##########

# clock

derive_clock_uncertainty

create_generated_clock -name {altera_dclk} -source [get_ports {altera_reserved_tck}] \

-master_clock {altera_reserved_tck} [get_ports {sfl:inst|altserial_flash_loader:altserial_flash_loader_component|\

GEN_ASMI_TYPE_1:asmi_inst~ALTERA_DCLK}]

##########

# constrain JTAG port

set_input_delay -clock altera_reserved_tck 20 [get_ports altera_reserved_tdi]

set_input_delay -clock altera_reserved_tck 20 [get_ports altera_reserved_tms]

set_output_delay -clock altera_reserved_tck 20 [get_ports altera_reserved_tdo]

###########

# ASMI port

set_output_delay -add_delay -clock [get_clocks {altera_dclk}] 13.000 \

[get_ports {sfl:inst|altserial_flash_loader:altserial_flash_loader_component|GEN_ASMI_TYPE_1:asmi_inst~ALTERA_SCE}]

set_output_delay -add_delay -clock [get_clocks {altera_dclk}] 8.000 \

[get_ports {sfl:inst|altserial_flash_loader:altserial_flash_loader_component|GEN_ASMI_TYPE_1:asmi_inst~ALTERA_SDO}]

set_input_delay -add_delay -clock [get_clocks {altera_dclk}] 11.000 \

[get_ports {sfl:inst|altserial_flash_loader:altserial_flash_loader_component|GEN_ASMI_TYPE_1:asmi_inst~ALTERA_DATA0}]

##########

# Remove clock groups set by Time Quest

remove_clock_groups -all

##########

# Set False Path

set_false_path -from [get_ports {altera_reserved_tck}] \

-to [get_keepers {sfl:inst|altserial_flash_loader:altserial_flash_loader_component|\

GEN_ASMI_TYPE_1:asmi_inst~ALTERA_DCLK}]

set_false_path -from [get_keepers {sfl:inst|altserial_flash_loader:altserial_flash_loader_component|\

alt_sfl_enhanced:ENHANCED_PGM:sfl_inst_enhanced|device_dclk_en_reg}] \

-to [get_ports {sfl:inst|altserial_flash_loader:altserial_flash_loader_component|\

GEN_ASMI_TYPE_1:asmi_inst~ALTERA_DCLK}]

[注意] GEN_ASMI_TYPE_1 の末尾番号は異なる場合があります。

sdc ファイル作成し保存後、下記メニューで .sdc をプロジェクトに登録します。

Assignments メニュー > Settings > Timing Analyzer カテゴリ

4. コンパイル

コンパイルを実行します。

Processing メニュー > Start Compilation

5. EP4CE75 に sof ファイルをダウンロード

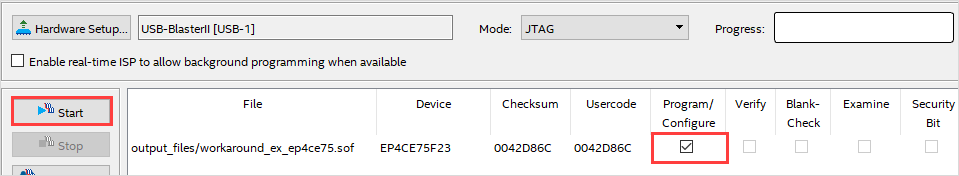

Programmer を起動します。(Tools メニュー > Programmer)

Hardware Setup を設定し、Mode に JTAG を選択します。

コンパイルで生成された sof ファイルをセットし、Program/Configure オプションを有効 (On) にします。

[Start] ボタンをクリックして、EP4CE75 へデータを転送します。

書き込み完了後、Programmer の画面から sof ファイルを [Delete] ボタンにより削除してください。

6. jic ファイルをダウンロード

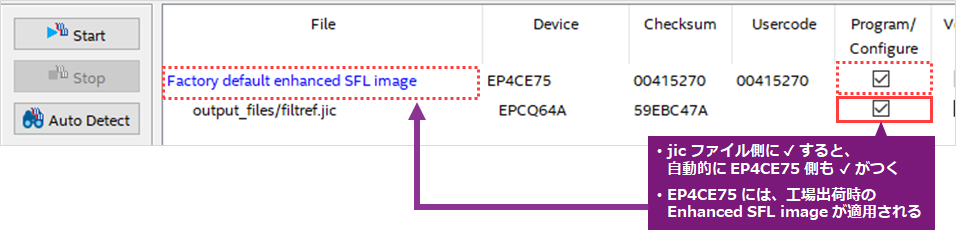

Programmer にあらかじめ作成しておいた jic ファイルを登録します。

jic ファイルの Program/Configure オプションを有効 (On) にします。

[参考: jic ファイル作成]

Quartus® ガイド - プログラミング・ファイルの生成と変換 (Convert Programming Files)

FPGA 経由で EPCQ デバイスへプログラミング (JIC プログラミング)

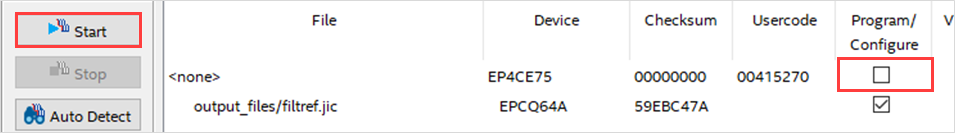

Factory default enhanced SFL image の Program/Configure オプションのみを無効 (Off) にします。

※ 手順5 により、SFL イメージは EP4CE75 へダウンロード済み

[Start] ボタンをクリックし、jic ファイルのみをダウンロードします。

以上で作業は終了です。

EP4CE75 経由でコンフィグレーション ROM へ jic ファイルを書き込む際は、この方法で回避してください。

おすすめ記事/資料はこちら

Altera® FPGA の開発フロー/FPGA トップページ

Quartus® ガイド - プログラミング・ファイルの生成と変換(Convert Programming Files)

FPGA 経由で EPCQ デバイスへプログラミング(JIC プログラミング)