こんにちは、しわしわ です。

今回はメモリ IP を生成する前に必要な、FPGA の選定作業とその方法について説明します。

前回の記事 『メモリ IP ~正確で効率的なデータ転送~』 では、DDR メモリを制御する回路であるメモリ IP の構成について書きました。

「メモリ IP の構成が分かったからメモリ IP を生成しよう!!」 と思い、

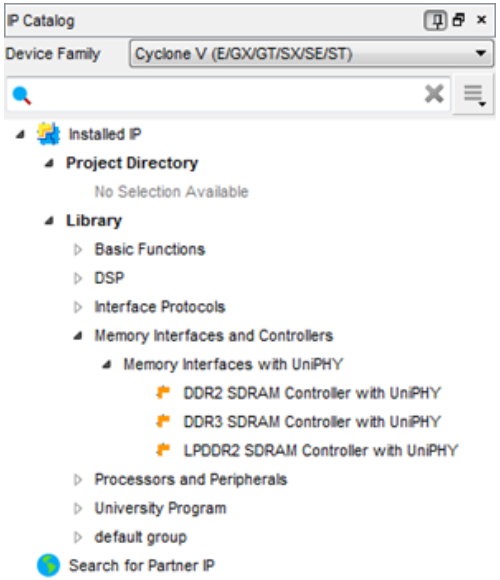

Quartus® Prime の 『Tools』 から生成したいメモリ IP を選択できる 『IP Catalog』 を起動。

どのメモリ IP を生成しようかな~と選択しようとすると、

しわしわ: 『あれ、メモリ IP って DDR2、DDR3、LPDDR2 以外にも種類があったような…』

そこで、今回はメモリ IP 生成の前に行わなければいけない、FPGA の選定についてです。

FPGA の選定

メモリ IP を生成するにあたり、どの FPGA ファミリがどのメモリをサポートしているのかを知る必要があります。

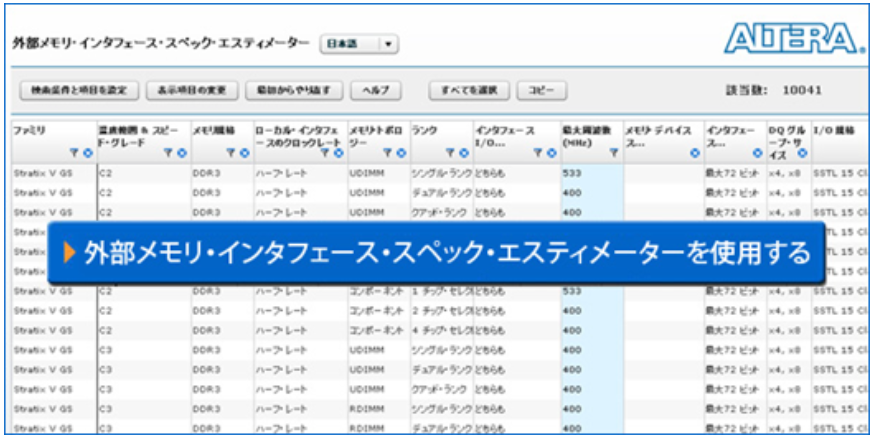

そこで有効になるのが EMIF Spec Estimator というツールです。

EMIF Spec Estimator とは、メモリスペックに応じた FPGA の選定が出来るツールです。

これを用いることで各デバイスのメモリインタフェースの性能が分かります。

※ EMIF Spec Estimator につきましては過去記事で詳しく説明されています。

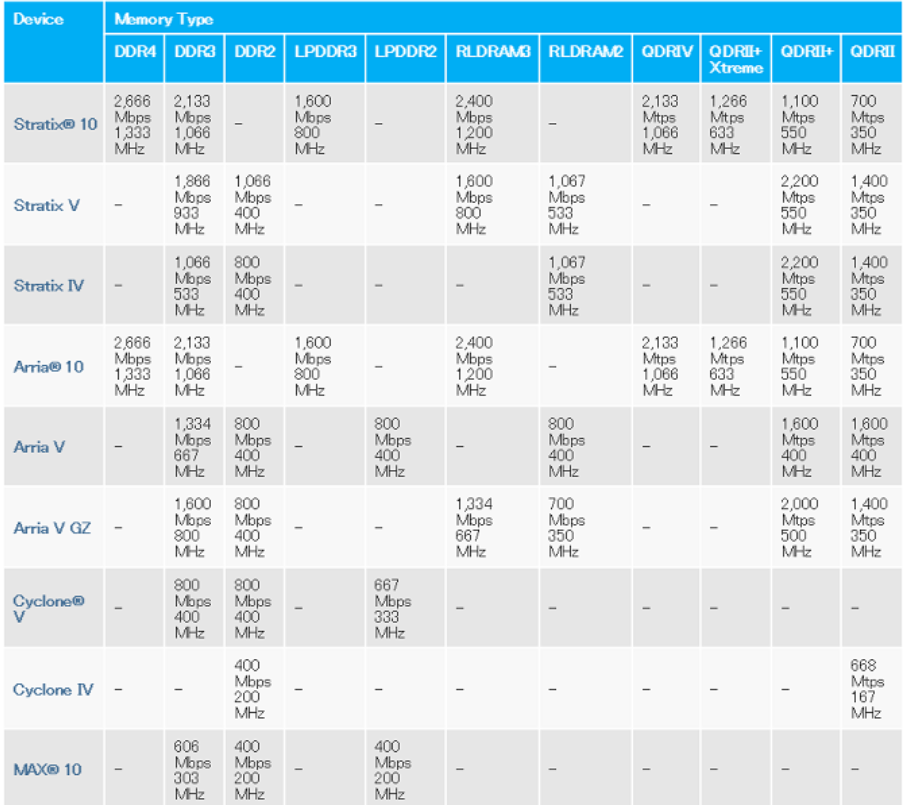

また、どの FPGA がどのメモリをサポートしているのかすぐに分かる一覧表はないか調べてみた結果、

アルテラ社ホームページの External Memory Interface のページから 「Device Support」 をクリックして開くと、External Memory Interface Support Device Memory Type の表がありました。

下記がその表で、縦軸が FPGA ファミリ、横軸がメモリタイプを示しています。

(※ 最新デバイスについては仕様が変更されている可能性もありますのでアルテラ HP をご確認ください)

また、表の中の数字は各 FPGA ファミリに対するメモリタイプの最大動作周波数及び最大データ転送速度です。

各 FPGA ファミリ、メモリタイプごとに最大動作周波数は決まっているため、

同じメモリを使った場合でもデバイスによって最大動作周波数が変わります。

例えば、DDR3 メモリの場合 Stratix® V では最大動作周波数が 933 MHz なのに対し

Stratix® 10 での最大動作周波数は 1066 MHz です。

今回、私のプロジェクトでは Cyclone® V が選択されていました。

Cyclone® V の項目を見てみると、RLDRAM や QDR は対応しておらず、

LPDDR2、DDR2、DDR3 に対応していることが分かりました。

今回の記事で、どの FPGA がどのメモリをサポートしているのかという FPGA の選定方法が分かりましたので

次回はメモリ IP の生成方法について書きたいと思います。

まとめ

- FPGA の選定方法は EMIF Spec Estimator と External Memory Interface Support Device Memory Type がある

- I/O 規格やクロックレート、インタフェースの種類など詳細な検索をしたい方は EMIF Spec Estimator が有効

- 一目で各デバイスでの最大動作周波数やどのデバイスがどのメモリに対応しているかを知りたい方は External Memory Interface Support Device Memory Type が有効

しわしわ のメモリシリーズ

・ 『SDR と DDR ~FPGA による DDR データの処理~』

FPGA による DDR データの処理についてまとめました。

・ 『メモリ IP ~正確で効率的なデータ転送~』

メモリ IP の構成要素と概要についてまとめました

・ 『メモリ IP ~FPGA の選定~』

どの FPGA がどのメモリをサポートしているか選定方法についてまとめました

・ 『メモリ IP ~生成とパラメータ入力~』

メモリ IP の生成方法と簡単にパラメータ設定が出来るプリセットについてまとめました

・ 『メモリ IP ~プリセットの保存と呼び出し~』

メモリ IP のプリセットを用いる際の注意点とプリセットの保存方法及び呼び出し方法についてまとめました