こんにちは、研修期間も終わりメモリチームに配属が決まりました、しわしわです。

メモリに関する知識を身につけるために、先輩たちが過去に書いたメモリ関連の記事を熟読していました。

※過去のメモリ関連の記事一覧はこちら

External Memory Interface ~ メモリとは? ~

External Memory Interface ~ リード? ライト? ~

External Memory Interface ~ PHY って? ~

External Memory Interface ~ ALTMEMPHY? UniPHY? ~

External Memory Interface ~ External memory interface Spec Estimator ~

External Memory Interface ~ External memory interface HDR ~

トレーニングや過去の記事を読み、メモリの勉強をしていると

FPGA-メモリ間と FPGA 内部ではデータ転送方式が違うことが分かりました。

違うデータ転送方式なのに、どうしてデータを正常に処理できるのだろう?と疑問に思ったので

今回は、 FPGA とメモリのデータ転送方式について調べてみました。

1. FPGA とメモリのデータ転送方式 ~ SDR と DDR ~

冒頭で述べたとおり、FPGA-メモリ間と FPGA 内部ではデータ転送方式が異なります。

FPGA 内部では CLK の立ち上がりのみでデータを転送する SDR (Single-Data-Rate) 方式 でデータを転送しています。

一方、FPGA-メモリ間では CLK の立ち上がりと立ち下がり、両方でデータを転送する DDR (Double-Data-Rate) 方式 でデータを転送しています。

FPGA内部のデータ転送方式 : SDR (Single-Data-Rate)

FPGA-メモリ間のデータ転送方式 : DDR (Double-Data-Rate)

※SDR と DDR は 過去記事でも説明されています。

ここでひとつ疑問が生じました。

『CLK の立ち上がり、立ち下りでデータ処理できる DDR 方式でメモリから FPGA にデータを転送しても

FPGA 内は、CLK の立ち上がりのみでデータを転送する SDR 方式なのでデータを処理できないのでは?』

さっそく先輩に聞いてみました。

しわしわ 「メモリから DDR 方式で転送されたデータは SDR 方式の FPGA 内で処理しきれるのですか?」

先輩 「FPGA は並列処理ができるから処理できるよ」

研修で学んだはずなのにすっかり忘れていました、FPGA は並列処理ができるのです。

ではメモリから DDR 方式で転送されたデータは FPGA 内でどのように処理されるのでしょうか?

2. FPGA による DDR データの処理

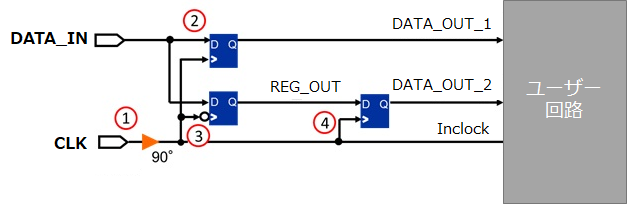

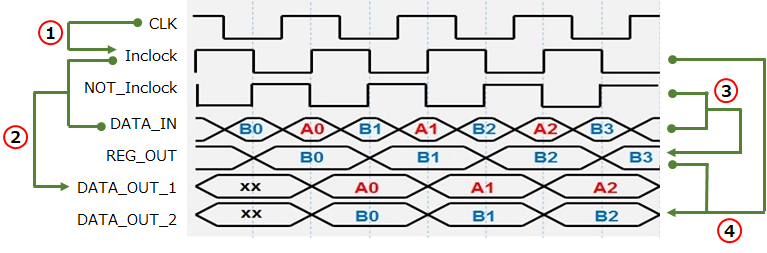

FPGA による DDR データの処理図 (図1) と、データとクロックのタイミング図 (図2) および 略語は、下記のようになっています。

|

略語 |

説明 |

| DATA_IN | メモリから FPGA に DDR で転送されるデータ |

| InClock | 90° 位相シフトさせた CLK |

| NOT_Inclock | Inclock の NOT |

| REG_OUT | DATA_IN を NOT_Inclock の立ち上がりのタイミングで取り、出力されるデータ |

| DATA_OUT_1 | DATA_IN を Inclock の立ち上がりのタイミングで取り、出力されるデータ |

| DATA_OUT_2 | REG_OUT を Inclock の立ち上がりで取り、出力されるデータ |

| データ A | DATA_IN において、CLK の立ち上がりで転送されるデータ (図2 の赤文字 A) |

| データ B | DATA_IN において、CLK の立ち下がりで転送されるデータ (図2 の青文字 B) |

DDR で転送されたデータを SDR で処理できるようにするために

【1】 まず、CLK を90°位相シフトします (CLK → Inclock) 。

【2】 次に DATA_INを Inclock の立ち上がりのタイミングでとると、DATA_OUT_1のような出力となり、データ A だけを出力します。

【3】 また、 DATA_INを NOT_Inclockの立ち上がりのタイミングでとると REG_OUTのような出力となり、データ B だけを出力します。

【4】 【3】によって出力された REG_OUTを Inclockの立ち上がりのタイミングでとることによって、DATA_OUT_1(データ A) と同じタイミングで DATA_OUT_2(データ B) が出力されます。

このように、CLK の 90° 位相シフトや NOT を使用し、立ち上がりと立ち下りのデータを2系統に分けて並列に処理することで、DDR 方式で転送されたデータを SDR 方式に変換し、FPGA 内部で正常にデータを処理できることがわかりました。

今回学んだ、FPGA とメモリのデータ転送方式の知識を活かして、

タイミング解析やタイミング設計に関するお問い合わせへの対応に役立てていきたいと思います。

まとめ

・CLK の立ち上がりのみでデータを転送する方式を SDR (Single-Data-Rate)、

CLK の立ち上がりと立ち下がり、両方でデータを転送する方式を DDR (Double-Data-Rate)と言う。

・FPGA 内部では SDR 方式でデータを転送、FPGA-メモリ間では DDR 方式でデータを転送。

・メモリから DDR 方式で転送されるデータは、FPGA 内部で SDR 方式に変換され、並列処理される。