こんにちは、日々トレーニングにて知識を身につけているしわしわです。

前回の記事で『FPGA による DDR データの処理』について書きました。

改めて自分で読んでみると、DDR→SDR への変換は FPGA のどの部分で行われているのだろう?

という新たな疑問が生まれました。

しわしわ 「DDR から SDR への変換処理は FPGA のどの部分で行われているのですか?」

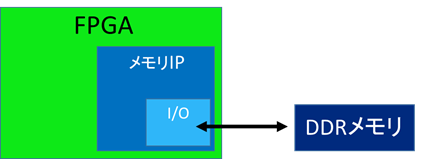

先輩 「メモリ IP の中の I/Oの部分で変換されるよ」

※I/O というのは『Input/Output』の略で文字通り、入出力を行う部分のことを言います。

※I/Oについての説明は過去記事のこちら

図1. FPGA とメモリインタフェース

確かに入出力の部分で FPGA 内部で処理できる形に変換しなければデータを処理できない

と納得できました。

しかし、また新たな疑問が生まれました。

『メモリIP の中の I/O? メモリ IP ってなんだろう…』

ということで今回はメモリ IP について調べてみることにしました。

IPとは

メモリIPを調べるにあたり、まずIPについて復習しました。

初めに IP という言葉を聞いたときは IP アドレスの方の IP (Internet Protocol) を連想していましたが

ここでの IP はIntellectual Propertyの略で、直訳すると『知的財産』となります。

知的財産ってなんだ??と、初めて聞いた時はよく分かりませんでしたが

簡単に言うと IP とは、『設計済みの機能回路ブロック』のことです。

過去記事でもお話しましたが、回路規模の増加に伴い、

すべての回路ブロックを初めから設計しようとすると、多くの工数が必要になります。

しかし、CPU やメモリ・コントローラなど、FPGA を設計する際に使用する各機能ブロックに

既存の設計情報 (IP) を用いることで簡単に FPGA を設計することが可能になります。

※インテル/パートナー IP の全リストについては、インテル社のFind IPをご覧ください。

メモリ IP とは

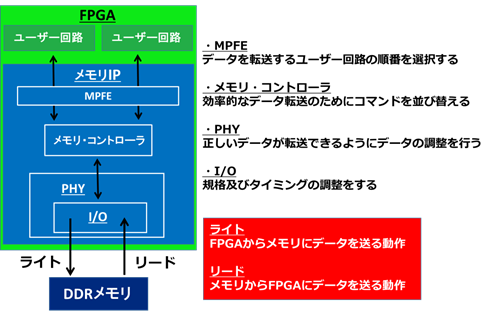

メモリ IP とは、DDR メモリを制御する回路のことで、おおまかに下記の2つの役割があります。

・FPGA-メモリ間で正確にデータを転送する

・FPGA-メモリ間で効率的にデータを転送する

メモリIPは図2.の青枠のようなブロック図となります。

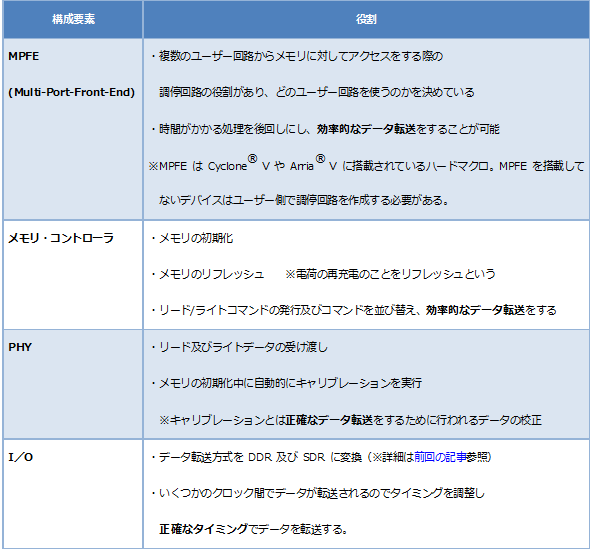

また、表1.のように、大きく分けて4つの要素で構成されます。

メモリIPの各構成要素の役割は図2. と表1の通りです。

図2. FPGA とメモリのインタフェース及びメモリ IP のブロック図

表1. メモリ IP の構成要素

FPGAが起動後、ユーザー回路から DDR メモリへ、リード/ライトができるようになるまでに

メモリ IP が行っている動作は下記のようになります。

1. メモリ・コントローラがメモリの初期化を行い、その間、PHYはキャリブレーションを実行する。

2. キャリブレーションが終わるとユーザーがメモリ・コントローラを制御することが可能になる。

3. MPFEによりユーザー回路が選択され、メモリ・コントローラにより、リード/ライトコマンドが発行される。

4. 発行されたコマンドは PHY, I/Oを通り転送され、それに伴うデータ転送が I/O上でメモリ規格に沿って行われる。

IPは簡単に FPGA を設計できる反面、内部を把握していない場合、バグがあったときデバッグが困難です。

今回、メモリ IP に関する記事を書き、メモリ IP の各要素の役割を理解することが出来たので

バグがあったときのデバッグや、より効率的なデータ転送を行えるようなメモリ IP の作成に役立てていきたいと思います。

まとめ

・IP は設計済みの機能回路ブロックであり、再利用ができ、簡単に FPGA を設計することが可能。

・メモリ IP はDDR メモリを制御する回路であり、正確で効率的なデータ転送を行う役割がある。

・メモリ IP は MPFE、メモリ・コントローラ、PHY、I/O で構成されDDR→SDRへの変換は I/O の部分で行われる。