太郎です。今回は PLL (Phase Locked Loop : 位相同期回路) による分周 / 逓倍について書きます。

前回の 新人エンジニアの赤面ブログ 『バッファーについて』 でもご紹介した通り、PLL のメイン構成要素は PFD / CP , LPF , VCO でした。

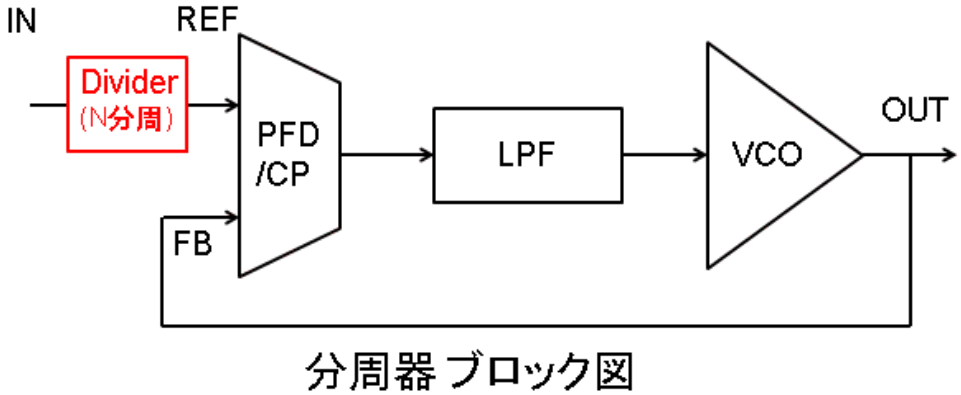

PLL は、リファレンス信号(以下 REF) / フィードバック信号(以下 FB)に分周器(Divider)が加わることによって、分周器 / 逓倍器として機能します。

今回は、その原理について書きます。

PLL による分周

PLL の分周回路は下図のように REF に分周器が付きます。

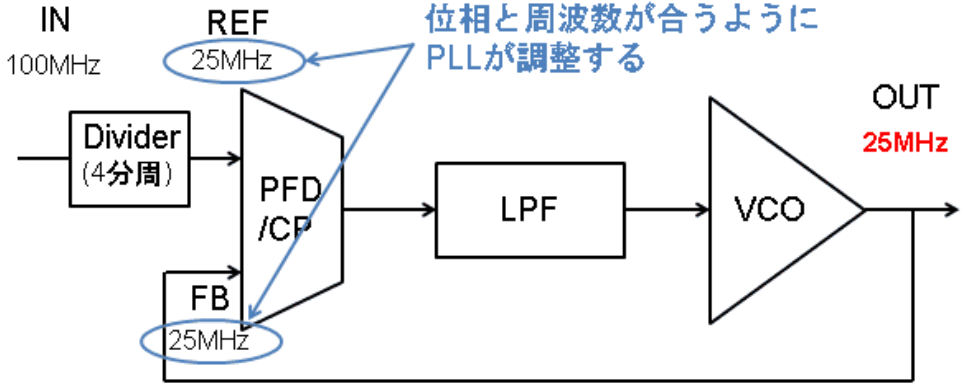

例として、入力 (IN) が 100 MHz, 分周器が 4 分周するものだとすると、REF は IN の 1/4 の 25 MHz となります。

すると、REF の位相 / 周波数に合うように FB の位相 / 周波数を PFD / CP が調整します。

PFD は REF と FB の位相 / 周波数を比較し、REF と FB の位相 / 周波数が等しくなるまで UP / DOWN 信号を出力し続けます。

このようにして、PLL による分周は行われます。

しかし、このブロック図を見て、わざわざ PLL を介さなくても、分周は分周器だけで実現可能だと思われた方もいるのではないでしょうか?

「分周する」 という目的だけであれば、確かに分周器だけで実現可能です。

しかし、入出力間で同期を取るのであれば PLL が必要です。

また、PLL による分周は、入力信号に対し VCO でクロック信号を生成し直すため、信号の精度は VCO に依ります。

VCXO (電圧制御型水晶発振器) を用いた PLL であれば、入力信号よりも精度の高い信号を得ることができます。

また、分周器が REF の前だけでなく、OUT の後段にも存在することもあります。

REF 前の分周器と OUT 後段の分周器を組み合わせて使用することで、より自由度の高い周波数を出力することができます。

PLL による逓倍

「逓倍」 とは、入力周波数を n 倍にすることを言います。最初は漢字が難しくて少々ビビりました(笑)。

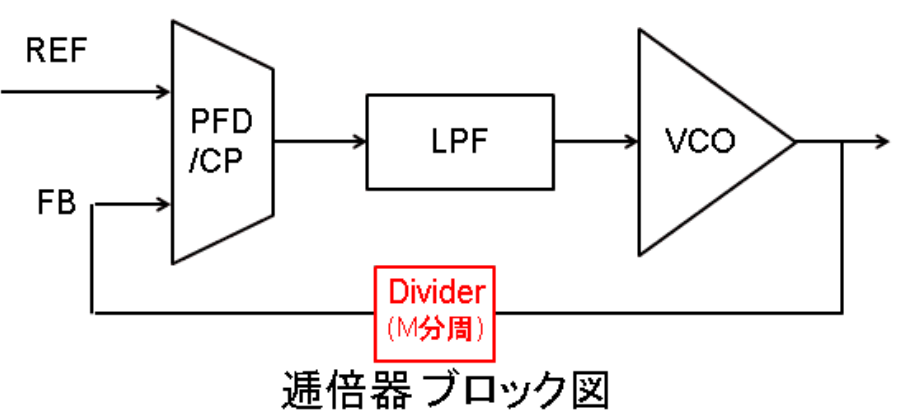

PLL の逓倍回路は下図のように FB に分周器が付きます。

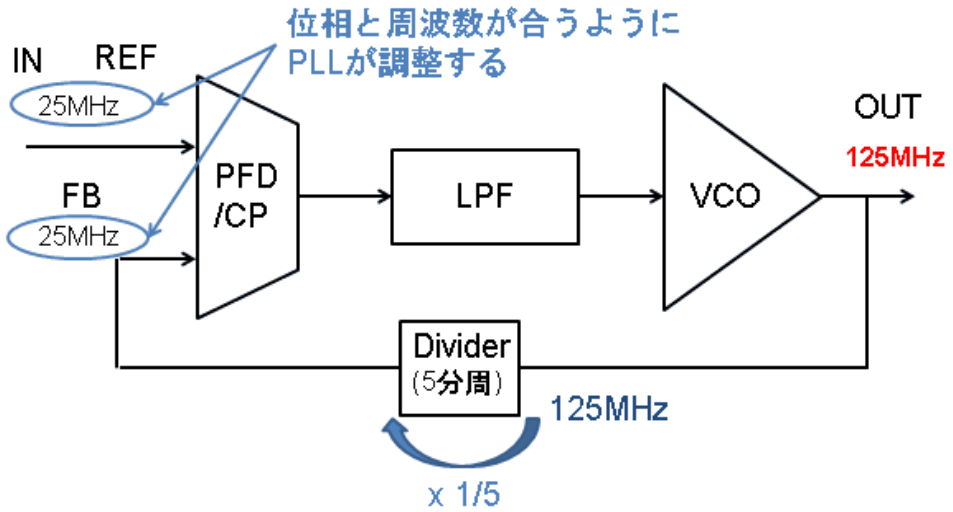

例として、入力(IN)が 25 MHz, 分周器が 5 分周するものだとすると、FB を 25 MHz に合わせるために、出力は 5 倍の 125 MHz となります。

このようにして、PLL で周波数の逓倍がおこなわれます。

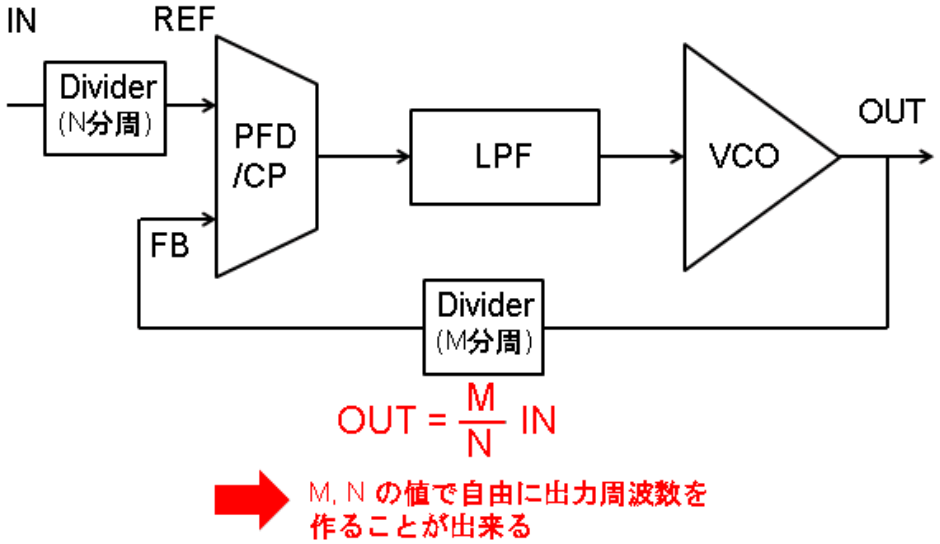

分周 / 逓倍を組み合わせた PLL

PLL による分周 / 逓倍を組み合わせることで、より自由に周波数を作り出すことができます。

例として、REF の 分周器が N 分周、FB の分周器が M 分周するものであれば、出力周波数は入力周波数の M/N 倍となります。

上図からも分かる通り、分周器の M , N の値の自由度が、作り出す周波数の自由度に直結しています。

IDT 社の製品には、Integer PLL 内蔵タイプと Franctional PLL 内蔵タイプで分かれている製品があるのですが、ここでの “Integer” , “Franctional” は上図の M , N の分解能を示しています。

IDT 社の製品である FemtoClock® NG では、FB 分周を Integer / Franctional をピンに入力する信号で使い分けることが出来ます。

FemtoClock® NG は位相 Jitter が非常に小さいのが特徴です。Franctional FB にすることで、周波数の分解能が上がり、数十 Hz 単位のステップで周波数の設定をおこなうことができます。出力する位相 Jitter は 0.5 ps rms です。

一方、Integer FB では、Franctional FB と比較し分解能は落ちるのですが、出力する位相 Jitter は 0.2 ps rms であり、非常に精度の高い周波数を出力できます。 Integer / Franctional の使い分けはユーザーの仕様によって決まりますが、いずれにしても出力信号の Jitter は小さいです!

クロック・ジェネレーターや Synthesizer では、このような PLL の原理によって、目的の周波数を作り出しています。

次回は PLL の応用方法について書きます。