IC の空き端子や論理を与えたい場合に、プルアップやプルダウンの抵抗を接続します。そのときの抵抗値については、「何となく」、「適当に」選択しているのではないでしょうか。あるいは、なぜ抵抗が必要なのか、あまり考えることなく、昔からやっているから、という単純な理由で抵抗を用いているかもしれません。

今回は、この抵抗値について考えてみることにします。

プルアップやプルダウンの目的

プルアップやプルダウンの目的は、主に、次の3つだと思います。

(1) 空き端子(または未使用端子)の開放を避けるため

(2) ハイかローの論理を意図的に与えるため

(3) バスの出力が全て開放(disable)になったときの論理を与えるため

それぞれについて考えてみます。

空き端子(または未使用端子)の開放を避けるため

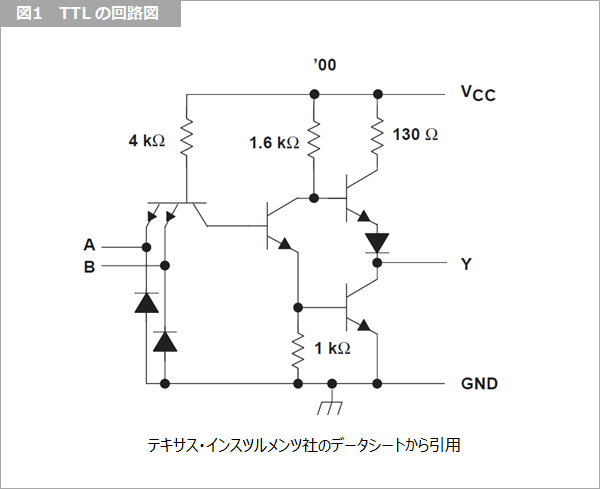

図1 は TTL の 7400 の回路図です。入力が開放のとき、入力のトランジスタは、逆トランジスタとして動作し、ベースからコレクタに電流が流れます。この状態はこのままで安定なので、「(1) 空き端子(または未使用端子)の開放を避けるため」は、TTL の場合には処理不要です。使わない端子を、後で使う場合もあるので、むしろ開放のままがいいでしょう。

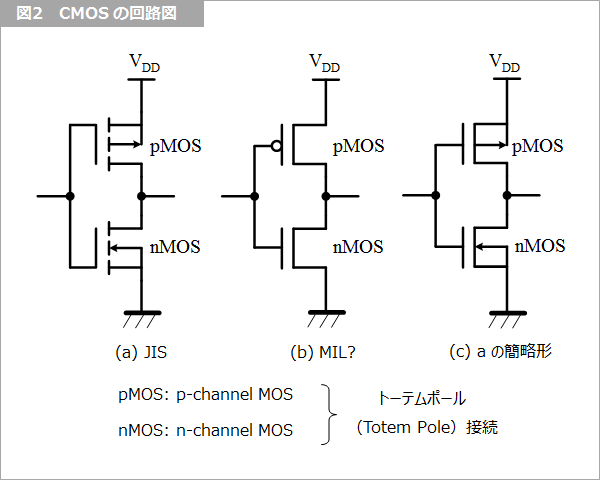

図2 は CMOS の回路図です。CMOS は、図に示すように、回路が上下対称なので、入力を開放にすると、入力がちょうど中間レベルとなり、最悪の場合には、出力トランジスタが両方ともオンになって、大きな貫通電流が流れるので、入力を開放にすることを避けます。したがって、入力をハイかローに固定するために、電源またはグウランドに接続します。

このときに、特に電源に直接接続せずに高い値の抵抗を接続する「習慣」があります。この高抵抗を接続する理由は、「(2) ハイかローの論理を意図的に与えるため」の TTL の場合と混同しているからだと推察します。

ハイかローの論理を意図的に与えるため

「(2) ハイかローの論理を意図的に与えるため」の場合は、TTL の入力は直接電源に接続せずに、高抵抗で電源に接続します。抵抗が必要な理由は、TTL の最大定格に起因しています。

TTLの最大定格は、電源電圧 Vcc が 7V、入力電圧が 5.5Vです(脚注1)。入力電圧の最大定格が低い理由は、TTL は、図1 に示すように、エミッタ入力で、バイポーラトランジスタは、エミッタとベースとの逆耐圧が低いためです。したがって、入力を電源電圧に接続すると、電源のマージン試験などを行う際に、電源電圧を 5.5V 以上に上げた場合に、入力が破壊する可能性があります。このため、抵抗を接続することが推奨されました。

その抵抗値は、TTL の入力電流から求める必要があります。入力電流は、7400 では、IIH<40uA@2.4V という規格があります。したがって、Vcc=4.75V(最小値)のときに 2.4V を確保するために、Rpullup<(4.75V-2.4V)/40uA=59kΩ にする必要があります。この習慣が、CMOS に移行した際に、値だけが独り歩きして、「プルアップの際には、数 10kΩ の抵抗を介して電源に接続する」というルールが定着したと考えます。

CMOS は、ハイを与える場合に、直接電源に接続しても構いません。ローを与える場合は TTL も CMOS もグラウンドに直接接続して構いません。ただし、試作回路の検証の際に、ハイまたはローに設定した端子に、反対の論理や信号を加えたい場合があります。そのためには、電源やグラウンドに直接接続せずに高い抵抗を介しておくといいでしょう。抵抗値の上限は、入力電流の最大値に対してハイまたはローが確定するように設定しますが、上の TTL の例のように決めればよいでしょう。

抵抗値の下限は、他の論理の確定した出力を接続する場合を想定して決めます。最も駆動能力の弱い(小さい)ドライバを 4mA とし、Vcc を 3.6V (max) とすると、VOL を 0.4V として、(3.6V-0.4V)/4mA=800Ω となります。こんな小さな抵抗は通常用いないと思うので、下限はほとんど考えなくてよいようです。もちろん反対の論理を加えるような可能性が皆無なら、直接接続します。

「(1) 空き端子(または未使用端子)の開放を避けるため」、「(2) ハイかローの論理を意図的に与えるため」いずれの場合も、入力端子にあらかじめプルアップやプルダウンの抵抗が内蔵されている場合があります。その場合には、当然、外部に抵抗を接続しません。

バスの出力が全て開放(disable)になったときの論理を与えるため

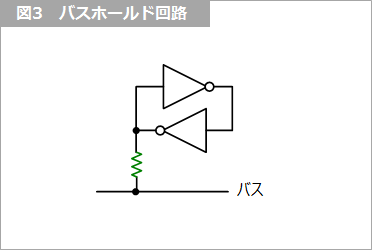

「(3) バスの出力が全て開放(disable)になったときの論理を与えるため」のバスに論理を与える場合には、抵抗の上限は、I/O 端子のリーク電流の合計を考慮して決めます。リーク電流が 20uA の素子が、そのバスに 8個接続されていると、160uA となります。電源を 3.0V (min) として、ハイの 2.4V を確保するためには、(3.0V-2.4V)/160uA=3.75kΩ となるので、思ったより小さな値になります。下限は、上に述べたように、ほとんど考える必要はないと思います。バスに論理を与える場合には、図3 に示すようなラッチを用いたバスホールド回路を用いると、バスが開放される前の論理を保持します。

脚注1

例外として、LS TTL は、ダイオード入力なので、入力電圧の最大定格も電源電圧と同じく、7V です。

碓井有三のスペシャリストコラムとは?

基礎の基礎といったレベルから入って、いまさら聞けないようなテーマや初心者向けのテーマ、さらには少し高級なレベルまでを含め、できる限り分かりやすく噛み砕いて述べている連載コラムです。

もしかしたら、他にも気になるテーマがあるかも知れませんよ!