これまでに説明した複数のキャパシタの共振によるインピーダンスの凹凸を、実際のキャパシタの種類と数を用いて解析するツールがインテルから提供されている PDN(Power Distribution Network/電源供給ネットワーク)ツールです。エクセルベースなので、特別なインストールも必要ないので、気軽に試してみることができます。

今回は、このツールのしくみについて解説します。

ツールを試したい方は、ここからダウンロードできます。

電源供給ネットワーク(PDN)ツール・ユーザガイド

ユーザ・ガイド(日本語)

ユーザ・ガイド(英語)

シグナルおよびパワー・インテグリティ・サポート(インテル)

Intel® FPGA Signal Integrity and Power Integrity

回路トポロジー

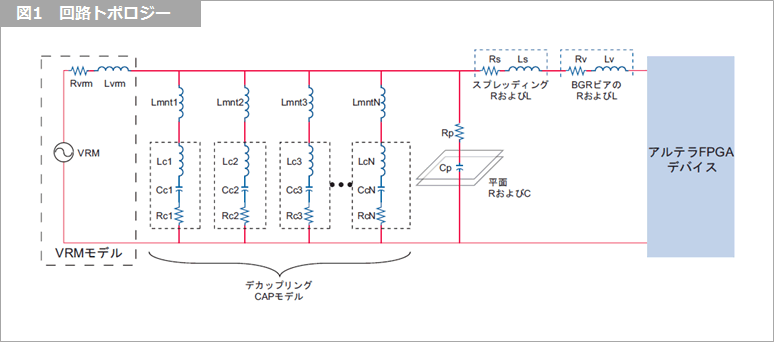

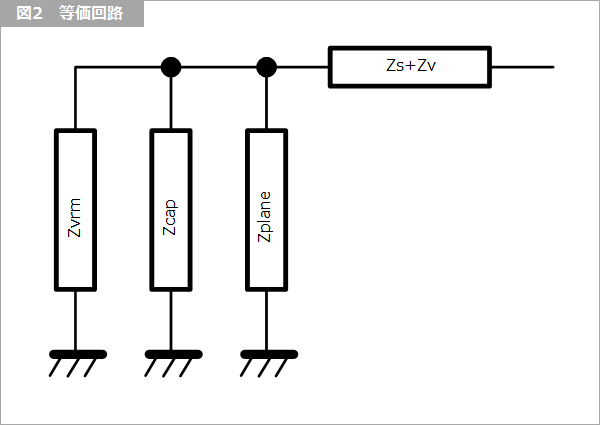

図1 に回路トポロジーを、図2 に等価回路を示します。

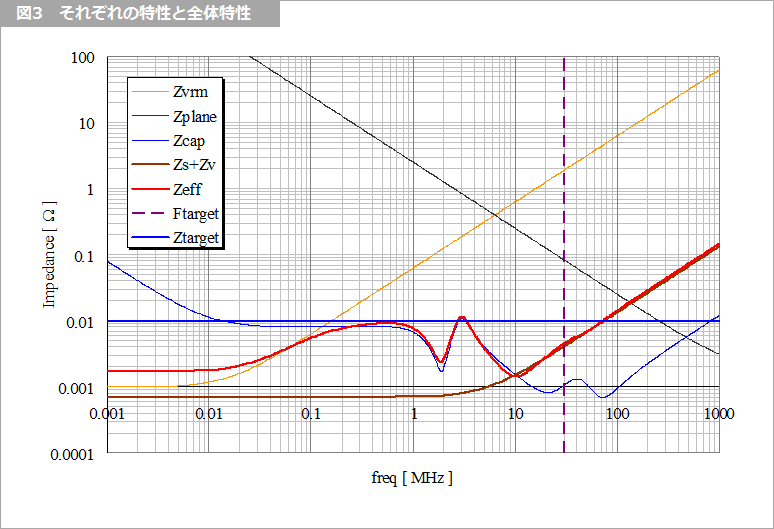

図3 に各ブロックごとのインピーダンス特性と全体の等価電源インピーダンスを示します。

PDNツールでは、周波数とインピーダンスのターゲットを設定して、それを満足するキャパシタの種類と数を決めます。

各エレメントについて述べます。

(1) 電源供給モジュール VRM(Voltage Regulator Module)

文字どおり電源レギュレータです。

理想電源に直列に抵抗 Rvrm とインダクタ Lvrm を介して電圧が出力されます。

Rvrm は低周波においては非常に低い値をとるので、電源供給系においては低周波領域のインピーダンス低減に寄与します。ただ、ある周波数から上は周波数に比例して増加するので、「(2) デカップリング・キャパシタ」にバトンタッチをします。

なお、Rvrm および Lvrm は、VRM のメーカから入手します。

図3 の特性では、Zvrm として示します。低域の特性に寄与します。

(2) デカップリング・キャパシタ

これまでに触れた複数のキャパシタを並列接続したものです。

多数の異なる容量のキャパシタを用いることにより、広い周波数帯域に対して全体的にインピーダンスのピークを押さえて平坦にします。

キャパシタに直列接続されるインダクタは、キャパシタ自体が有する ESL(Equivalent Series Inductance)と基板に実装される際に生じる Lmnt との和で表します。

(3) 電源層のキャパシタ

電源-グラウンドは、平行平板キャパシタを形成しています。その容量は、

C = εLW/h

と表せます。

ここに、ε は誘電率、L と W は長さと幅で、h は電源-グラウンド間の距離です。2枚のグラウンド層が電源層を挟んでいる場合には、それぞれの容量の和となります。

抵抗は、長方形の 2辺の長い方を長さ L とし、短い方を幅 W として、

R=ρL/Wt

で求めます。

ρ は抵抗率で、銅の 25 ℃ における値は、1.72 × 10^-8 です。

(4) 電源層と IC との接続

複数のキャパシタに対して、直列に抵抗とインダクタがつながります。

全体の特性(Zeff)は、(1) ~ (3) の並列接続に対して、(4) が直列に接続されます。それぞれのインピーダンスは複素数なので、エクセルの複素数関数を用いて計算します。

図3 の全体特性(Zeff)で高い周波数でインピーダンスが増加していますが、この領域は IC 内部の容量によって電源ノイズを抑えるので、周波数の上限 Ftarger を与えます。

碓井有三のスペシャリストコラムとは?

基礎の基礎といったレベルから入って、いまさら聞けないようなテーマや初心者向けのテーマ、さらには少し高級なレベルまでを含め、できる限り分かりやすく噛み砕いて述べている連載コラムです。

もしかしたら、他にも気になるテーマがあるかも知れませんよ!