Intel: When I compiled HDL code written in arrays to infer memory for MAX® 10 FPGAs, it was placed in logic elements instead of memory blocks.

Category: Tools

Tools: Quartus® Prime Standard Edition, Lite Edition

Device: MAX®10

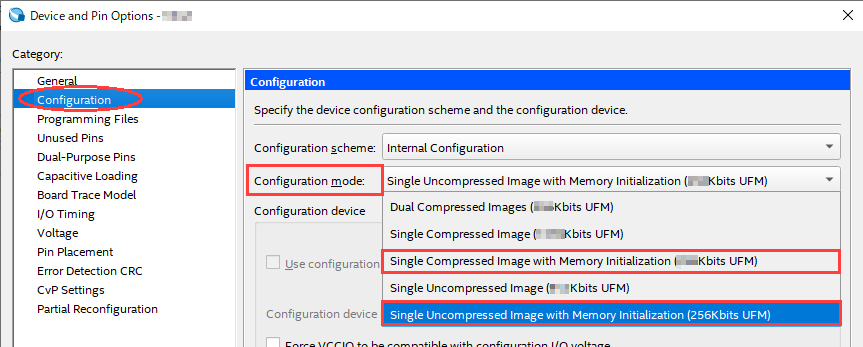

To force the "ROM" or "RAM with initial values" memory in the user-written HDL code to be placed in the memory blocks of the MAX® 10 FPGA, set the Configuration Mode setting (under Device and Pin Options) to one of the following: Please specify.

・Single Compressed Image with Memory Initialization

・Single Uncompressed Image with Memory Initialization

The reason why it is still not assigned to a memory block may be that it is not recognized as memory, such as not being suitable for the memory block structure of the target device.

To place it in the memory block inside the FPGA, it is recommended to use a memory IP, but if you want to describe it in HDL, please refer to the document below.

■ Inferring Memory Functions from HDL Code (「Intel® Quartus® Prime User Guide: Design Recommendations」より)

<Pro Edition>

https://www.intel.com/content/www/us/en/docs/programmable/683082/22-2/inferring-memory-functions-from-hdl-code.html

<Standard Edition>

https://www.intel.com/content/www/us/en/docs/programmable/683323/18-1/inferring-memory-functions-from-hdl-code.html

Note that if the MAX® 10 FPGA device function option is Compact, you cannot set the initial value to the memory block. please note.

[Related FAQ]

My design created in HDL is not assigned to a memory block in my FPGA. Is there a way to specify it?

Can Compact in MAX 10 devices set initial values to M9K memory?

![]() Experienced FAE

Experienced FAE

Free consultation is available.

From specific product specifications to parts selection, the Company FAE will answer your technical concerns free of charge. Please feel free to contact us.