FPGA & SoC FPGA with highest performance at 20nm

Arria ® 10 FPGAs & SoCs deliver the highest performance at 20nm, offering a performance advantage over competitive devices by one speed grade. It also features the industry's only hardened floating-point DSP that consumes up to 40% less power than previous generation mid-range FPGAs & SoCs and delivers up to 1,500 GFLOPS of processing performance.

Arria® 10 FPGAs & SoCs deliver the highest performance at 20nm

- 1 speed grade faster than competing FPGAs & SoCs

- Industry's only mid-range FPGA supporting 25.78 Gbps

- Highest performance 2,400 Mbps DDR4 SRAM memory interface

- Hardened IEEE 754 Compliant Floating Point Arithmetic Delivering 1,500 GFLOPS DSP Performance

- 96 transceiver lanes providing 3.3 Tbps of serial bandwidth

40% less power than previous generation FPGA & SoC

- Programmable Power Technology reduces static power consumption by selecting lower power transistors for non-performance critical paths

- Smart Voltage ID allows device to operate at optimum voltage without impacting performance

- VCC Power Manager - User selectable trade-off between performance and power consumption with operating voltage

- Low Static Power Grade - Provides devices with reduced static power consumption

![]() Download the latest version of Quartus® Prime design software

Download the latest version of Quartus® Prime design software

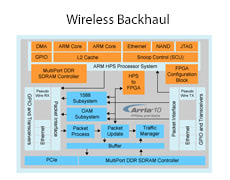

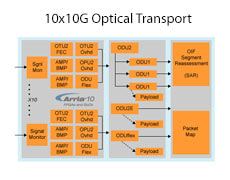

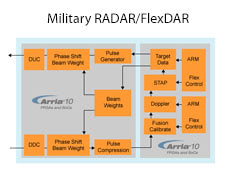

Arria® 10 FPGA & SoC Applications

|

|

|

|

Industry's only 20nm ARM-based SoC FPGA

- Offers multiple SoC devices with dual-core ARM Cortex TM-A9 HPS

- CPU running at 1.5 GHz per core

- Migrate from 28nm SoC FPGA Arria® V to Arria® 10 without changing processor code

Saves board space through integration

- Twice the density of previous generation midrange products with over 1 million logic elements

- Hardened Intellectual Property (IP): DDR4 memory controller and PCI Express® (PCIe®) 3.0 specification (Gen3)

Increase productivity and accelerate time-to-market with Altera® Quartus® Prime design software

- Industry's fastest 20nm compile times and most advanced design environment

- Low latency, best-in-class IP cores for 100G Ethernet, 100G Interlaken, PCIe Gen3, and more

- Industry's fastest compile times (up to 2.5x faster than the nearest competing software) for faster design iterations and timing closure

- C-based design entry using Altera 's SDK for OpenCL™, providing an FPGA-friendly design environment

- System-level design environment with Qsys system integration tools

- DSP Builder - A model-based DSP environment within the MATLAB/Simulink environment

Table 1. Arria® 10 Varieties

| Breed | explanation |

| Arria® 10 GT | Supports chip-to-chip data rates up to 25.78 Gbps, backplane data rates up to 12.5 Gbps, up to 96 full-duplex transceivers, and up to 1.15 million LEs worth of FPGA |

| Arria® 10 GX | Up to 96 full-duplex transceivers supporting chip-to-chip data rates up to 17.4 Gbps and backplane data rates up to 12.5 Gbps, and up to 1.15 million LEs worth of FPGA |

|

Arria® 10 SX |

Dual-core ARM Cortex-A9 HPS, up to 48 full-duplex transceivers supporting chip-to-chip data rates up to 17.4 Gbps and backplane data rates up to 12.5 Gbps, and up to 660,000 LEs worth of SoC |

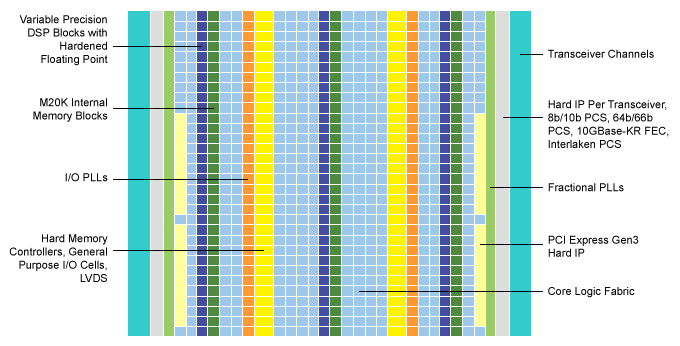

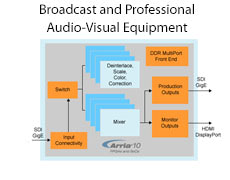

Figure 1: Arria 10 FPGA Architecture