Realizing "SLVS-EC v3.0/3.1," a next-generation CMOS image sensor interface, with FPGA

Overview

SLVS-EC v3.0/3.1 Rx IP is an interface IP core that runs on Altera® FPGAs. By using this IP, you can quickly and easily create products that comply with the latest SLVS-EC standard v3.0/3.1. An evaluation kit is also provided for early adoption.

- Realizing reception function from SLVS-EC interface using Altera® FPGA

- Compatible with the latest SLVS-EC Specification Version 3.1

- Supports powerful De-Skew function. Allows you to design boards without having to worry about skew between lanes.

- An evaluation kit is available for speedy evaluation of actual equipment.

Example of system configuration using this IP

SLVS-EC Standard Overview

- SLVS-EC (Scalable Low Voltage Signaling with Embedded Clock) is an interface standard for high-resolution, high-speed image sensors developed by Sony Semiconductor Solutions Corporation.

- The SLVS-EC standard is being standardized by the Japan Industrial Imaging Association (JIIA).

SLVS-EC interface connection to Sensor

Features

- Compatible with SLVS-EC Specification Version 1.2/2.0/3.0 and the latest 3.1

- Realizes various functions defined in the SLVS-EC Link layer

- 32 or 64 pixel selectable output interface

- Supports 8, 10, 12, 14, 16 bits per pixel - Utilizing the features of GCC (Gigabit Channel Coding) added in the latest SLVS-EC Version 3.0/3.1, transmission is achieved with less overhead than conventional ANSI 8b10b.

- Supports error correction function using ECC (Error Correction Code)

- Supports Byte to Pixel conversion in 1, 2, 4, 6, and 8 lane configurations

- Includes header parsing and payload error detection

- Unnecessary functions can be removed using compile options.

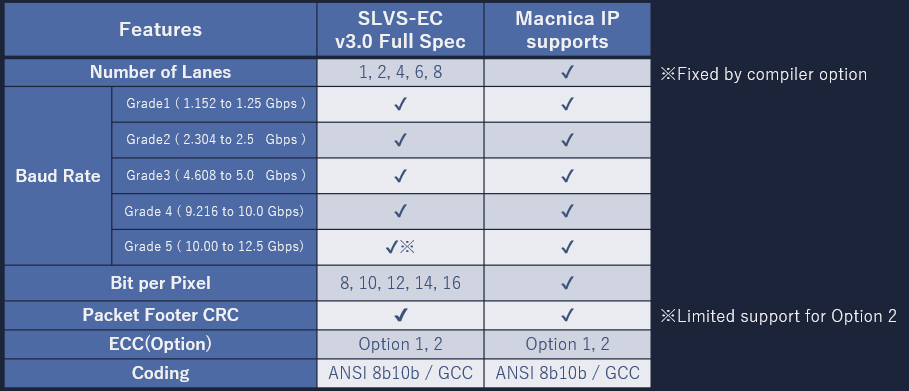

Specifications

corresponding device

Manufactured by Altera®

- Arria® 10 FPGA

- Agilex™ 7 FPGA

- Agilex™ 5E(GroupB) FPGA

Evaluation Kit: Luminous IMX537 SLVS-EC Sensor EVM

For more information on the evaluation kit, please see here.

Evaluation kit usage example

How the connection works

exterior

Our related solutions

CoaXPress® Device IP Package for Altera® FPGA - Semiconductor Business -Macnica (macnica.co.jp)

CoaXPress® Device IP Package for Microchip FPGA - Semiconductor Business -Macnica (macnica.co.jp)