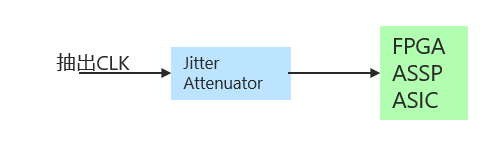

About jitter attenuator

The number of high-speed serial interface protocols is increasing, and the number of cases where high-speed ADCs (Analog Digital Converters), DACs (Digital Analog Converters), and high-speed FPGAs for signal processing are used is increasing. Including the high-speed interface used in the Physical Layer, ASSP, etc., the input regulations for reference clock jitter / wander become stricter as the speed increases. In order to reproduce and use the clock embedded in the signal, the clock is embedded in the data so that 0 or 1 such as scrambling or 8B10B is not continuous to some extent, and the received data is processed by the clock data recovery circuit (CDR). Regenerate the clock from

This clock is often recovered by the interpolator method, and the recovered clock contains low-frequency jitter and wander of the transmission path. If the clock including this jitter is used as the reference clock and the transmission clock is generated by the PLL inside the FPGA and inside the ASSP, the jitter contained in the reference clock does not satisfy the internal PLL regulations, and the PLL cannot be synchronized, jitter, Wander can pass through and lead to degradation of the eye pattern of the transmitted data. This deterioration of the eye pattern may lead to the inability to comply with the transmission data regulations and the deterioration of the error rate on the receiving side.

In audio products, all jitters and wanders leak out from speakers and headphones as noise. Therefore, it is recommended to use an IC such as a jitter attenuator or jitter cleaner to suppress jitter.

Depending on the manufacturer, there are different names such as jitter attenuator, jitter cleaner, and clock conditioner, but the internal structure of the IC is the same.

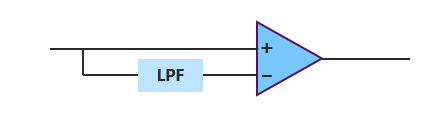

When jitter attenuators and jitter cleaners began to appear, LPFs were commonly used. Therefore, a configuration was adopted to reduce low-frequency jitter by setting a register that sets the cutoff frequency of the LPF.

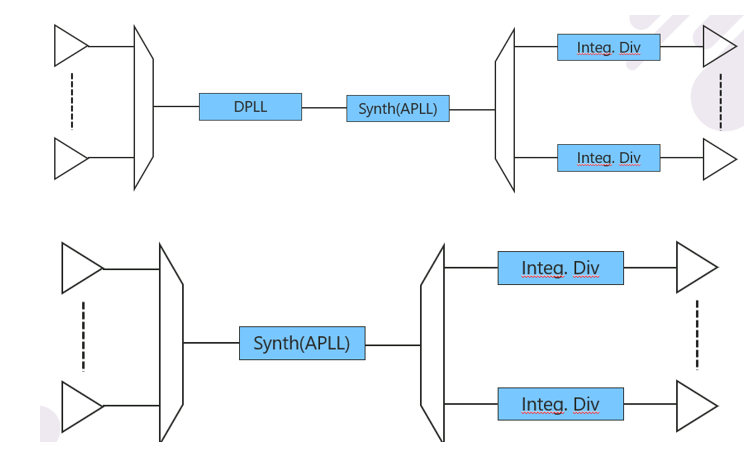

After that, due to the progress of PLL IC, PLL came to be adopted, and the internal configuration of both jitter attenuator and jitter cleaner came to be composed of DPLL + analog PLL. Some may consist entirely of analog PLLs.

A DPLL removes the jitter and an analog PLL generates the desired frequency. DPLL and VCO used in analog PLL are both built-in, and only analog PLL requires external PLL. Some DPLLs can lower the loop bandwidth, and some can also remove the wander contained in the reference clock. In order to eliminate wander, it is normal to set the DPLL loop bandwidth to less than 1Hz (the wander frequency refers to less than 10Hz), and setting the loop bandwidth to a low value has the adverse effect of lengthening the lock time of the DPLL. there is.

The band used by normal line cards is selected around 10Hz to 20Hz. By setting this loop bandwidth, jitter from 12Khz to 20MHz can be removed and the transmission regulations can be met. Next is the analog PLL. When using an external VCO, a VCO with good jitter stability is required. This is because any jitter in the VCO translates directly to jitter in the output. Create desired frequency with analog PLL and output. If you need multiple frequencies, use a fractional divider. Because fractional division introduces more jitter into the output, it is common practice not to use fractional division on clocks used for transmission.

Inquiry

If you have any questions regarding this article, please contact us below.

To Microchip manufacturer information Top

If you want to return to Microchip manufacturer information top page, please click below.